Бортовой вычислитель воздушного судна на конфигурируемых процессорах

Автор: Иванов И.М., Викторов Д.С.

Журнал: Журнал Сибирского федерального университета. Серия: Техника и технологии @technologies-sfu

Статья в выпуске: 6 т.12, 2019 года.

Бесплатный доступ

В статье рассматривается бортовой вычислитель воздушного судна, построенный на конфигурируемых процессорах, разработан алгоритм управления избыточностью бортового вычислителя, который предполагает комплексное применение структурной, временной и версионной избыточностей, и приведена модель надежности.

Бортовой вычислитель, надежность, отказоустойчивость, управление избыточностью

Короткий адрес: https://sciup.org/146281378

IDR: 146281378 | УДК: 629.7.025.001.2:620.193 | DOI: 10.17516/1999-494X-0163

The onboard computer of the aircraft on the configurable processor

The article deals with an on-board computer of an aircraft built on a configurable processor, an algorithm for controlling the redundancy of an on-board computer is developed, which assumes a complex application of structural, temporal and versional redundancies and provides a reliability model.

Текст научной статьи Бортовой вычислитель воздушного судна на конфигурируемых процессорах

This work is licensed under a Creative Commons Attribution-NonCommercial 4.0 International License (CC BY-NC 4.0).

Задачи разработки и проектирования комплексов бортового оборудования (КБО) перспективных авиационных комплексов (ПАК) являются одними из приоритетных задач авиационной промышленности Российской Федерации [1, 2].

В интересах совершенствования КБО по дальнейшей унификации модулей и компонентов с целью снижения массогабаритных характеристик, повышения производительности элементной базы, надежности и отказоустойчивости предлагается разработать бортовой вычислитель воздушного судна на конфигурируемых процессорах и алгоритм управления избыточностью бортового вычислителя.

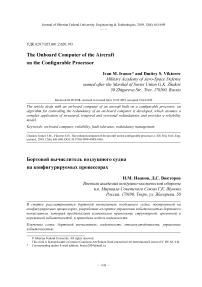

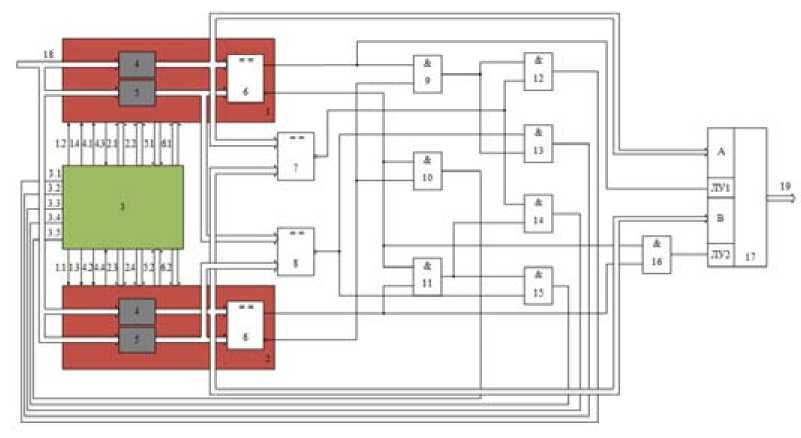

Предлагаемый бортовой вычислитель с управляемой избыточностью воздушного судна содержит два конфигурируемых процессора различных фирм производителей, в кристаллах которых синтезировано по два внутренних канала обработки информации и по одному элементу сравнения (полученного путем описания логики работы процессора на одном из языков описания аппаратуры JHDL, AHDL, VHDL или Verilog, причем для описания алгоритмов функционирования внутренних каналов обработки информации применяются разные языки программирования), вне кристаллов располагаются две схемы сравнения, восемь элементов И, коммутатор, блок управления и контроля, вход данных системы и выход данных системы (рис. 1). Блок управления и контроля (рис. 2) содержит дешифратор кода неисправности, семь элементов И, пять элементов ИЛИ, генератор синхронизирующих импульсов, постоянно запоминающее устройство (ПЗУ) начального адреса, конфигурационное ПЗУ, ПЗУ коэффициента деления, две памяти контрольных точек, счетчик адреса, счетчик количества повторов кода неисправности, счетчик коэффициента деления, счетчик модификации адреса очередной контрольной точки (КТ), два коммутатора, мультивибратор, схему сравнения, регистр адреса команды-инициатора, регистр кода неисправности, асинхронный регистр, регистр адреса очередной КТ, входы неисправности,

Рис. 1. Бортовой вычислитель воздушного судна на конфигурируемых процессорах

Fig. 1. The onboard computer of the aircraft on the configurable processor

Рис. 2. Блок управления и контроля

Fig. 2. Control and monitoring unit управляющие выходы, выходы адресов, выходы загрузки программного обеспечения (ПО) обработки данных, выходы формирования КТ, входы завершения формирования КТ, входы передачи данных, выходы передачи данных.

Такое построение бортового вычислителя (БВ) позволяет парировать одиночные и кратные отказы технических средств (ТС) и ПО и за счет контроля интенсивности сбоев изменять интенсивность формирования КТ.

Алгоритм управления избыточностью бортового вычислителя

При разработке алгоритма управления избыточностью БВ приняты следующие допущения:

-

1) средства контроля и диагностирования считаются абсолютно надежными;

-

2) отказы конфигурируемых процессоров (КП) носят случайный и независимый характер;

-

3) проявления дефектов программного обеспечения независимы друг от друга;

-

4) интенсивности восстановления после сбоев и отказов являются неизменными;

-

5) восстановление сбившегося внутреннего канала обработки (ВКО) информации осуществляется путем повтора программы обработки информации с предыдущей контрольной точки (КТ), при этом КТ представляет собой периодически записываемое операционной системой в энергозависимую память состояние всех полей основной памяти БВ;

-

6) последствия отказов программного обеспечения обработки данных в ВКО ликвидируются путем перепрограммирования;

-

7) последствия поврежденных блоков КП ликвидируются путем перепрограммирования отказавшего ВКО в свободную область КП;

-

8) одновременный отказ ВКО в каждом из КП невозможен.

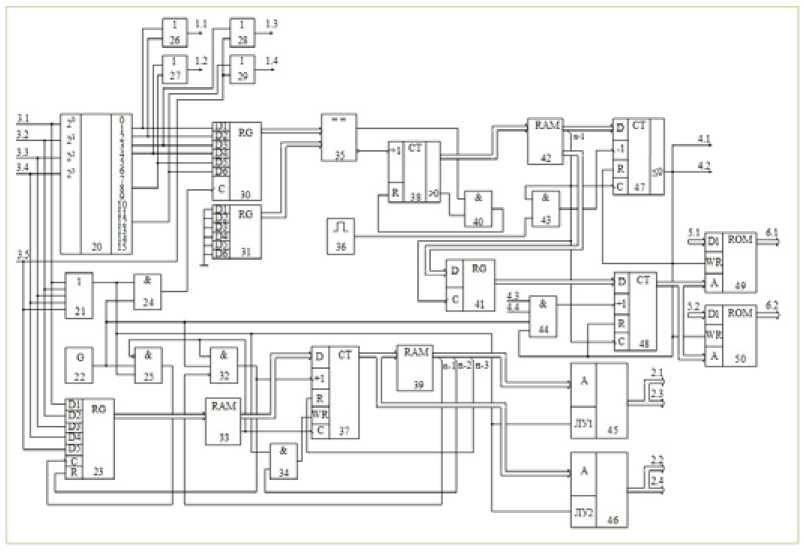

Предлагаемый алгоритм управления избыточностью представлен на рис. 3. Сущность алгоритма заключается в комплексном применении структурной (структурное резервирование), версионной (бортовой вычислитель реализован на КП различных фирм производителей, логика работы процессоров описана на различных языках описания аппаратуры) и временной (восстановление вычислительного процесса осуществляется по КТ, и в зависимости от частоты проявления последовательных сбоев осуществляется динамическое изменение интервалов формирования КТ) избыточностей, направленных на повышение отказоустойчивости бортового вычислителя.

Бортовой вычислитель начинает работу в двухканальной конфигурации. В процессе функционирования данные обрабатываются внутренними каналами обработки информации, которые программно синтезированы в кристаллах конфигурируемых процессоров; кроме того, в кристаллах КП синтезировано по одной схеме сравнения, которая поразрядно сравнивает информацию между ВКО КП. Формирование КТ осуществляется с частотой Хкт, которая выбирается из особенностей программного обеспечения. Проверка исправности функционирования бортового вычислителя осуществляется за счет средств контроля и диагностирования.

При несовпадении результатов обработки информации во внутренних каналах обработки информации КП средства контроля и диагностирования регистрируют код неисправности К; отказавшего внутреннего канала обработки информации, предпринимается попытка его восстановления путем m -кратного повторения вычислений с предыдущей контрольной точки, где m - количество возвратов к предыдущей КТ. В случае восстановления отказавшего внутреннего канала обработки информации бортовой вычислитель продолжает функционировать в двухканальной конфигурации (неисправность идентифицируется как сбой в канале). В противном случае при m >3 принимается решение об отказе конфигурируемого процессора и по зарегистрированному коду неисправности K i блоком управления и контроля бортового вычислителя формируется команда на частичное (отказ одного ВКО) либо на полное (отказ двух ВКО) перепрограммирование конфигурируемого процессора. После успешного перепрограммирования осуществляется получение очередного пакета информации и ее обработка. При несовпадении результатов обработки информации после перепрограммирования конфигурируемого процессора и выполнения условия K i = K i+1 (полученный код неисправности соответствует коду предыдущей неисправности) количество последовательных повторов неисправности суммируется ( NKi +1), в результате чего частота формирования КТ изменяется на величину, равную X KT = 1/( 7 KT_kT / N Ki ). Если один и тот же код неисправности повторится больше трех раз NKi>3, канал исключается из конфигурации и БВ переходит на функционирование в одноканальной архитектуре.

Функционирование БВ в одноканальной конфигурации осуществляется аналогично.

Таким образом, комплексное применение структурной, временной и версионной избыточностей позволяет парировать отказы программного обеспечения и технических средств, дает возможность классифицировать неисправности как сбой/отказ, избегая неоправданного расхода резервных ресурсов, а также изменять частоту формирования КТ при возникновении последовательных отказов.

Рис. 3. Алгоритм управления избыточностью бортового вычислителя

Fig. 3. Algorithm for controlling the redundancy or the on-board computer

Модель надежности бортового вычислителя

Проведем количественную оценку прироста надежности при применении предложенного выше алгоритма, для чего разработаем модель надежности БВ. При разработке модели примем дополнительное допущение об экспоненциальном законе распределения времени до отказа. С учетом принятых допущений математическую модель, описывающую поведение БВ для предложенного алгоритма, можно выразить марковской цепью с непрерывным временем и следующими дискретными состояниями:

-

S 0 – исправное состояние бортового вычислителя;

-

S 1 – отказ первого внутреннего канала обработки информации первого конфигурируемого процессора;

-

S 2 – отказ второго внутреннего канала обработки информации первого конфигурируемого процессора;

-

S 3 – отказ первого конфигурируемого процессора;

-

S 4 – отказ первого внутреннего канала обработки информации второго конфигурируемого процессора;

-

S 5 – отказ второго внутреннего канала обработки информации второго конфигурируемого процессора;

-

S 6 – отказ второго конфигурируемого процессора;

-

S 7 – отказ первых внутренних каналов обработки информации первого и второго конфигурируемых процессоров;

-

S 8 – отказ вторых внутренних каналов обработки информации первого и второго конфигурируемых процессоров;

-

S 9 – отказ первого внутреннего канала обработки информации первого конфигурируемого процессора и второго внутреннего канала обработки информации второго конфигурируемого процессора;

S 10 – отказ второго внутреннего канала обработки информации первого конфигурируемого процессора и первого внутреннего канала обработки информации второго конфигурируемого процессора;

S 11 – отказ первой версии программного обеспечения;

S 12 – отказ второй версии программного обеспечения;

-

S 13 – отказ первой версии программного обеспечения и первого внутреннего канала обработки информации первого конфигурируемого процессора;

-

S 14 – отказ первой версии программного обеспечения и второго внутреннего канала обработки информации первого конфигурируемого процессора;

-

S 15 – отказ второй версии программного обеспечения и первого внутреннего канала обработки информации второго конфигурируемого процессора;

-

S 16 – отказ второй версии программного обеспечения и второго внутреннего канала обработки информации второго конфигурируемого процессора;

-

S 17 – отказ первой версии программного обеспечения и первого конфигурируемого процессора;

-

S 18 – отказ второй версии программного обеспечения и второго конфигурируемого процессора;

-

S 19 – формирование контрольной точки (КТ) при исправном функционировании обоих конфигурируемых процессоров;

-

S 20 – формирование КТ при исправном функционировании второго внутреннего канала обработки информации первого конфигурируемого процессора и первого – второго внутренних каналов обработки информации второго конфигурируемого процессора;

-

S 21 – формирование КТ при исправном функционировании первого внутреннего канала обработки информации первого конфигурируемого процессора и первого – второго внутренних каналов обработки информации второго конфигурируемого процессора;

-

S 22 – формирование КТ при исправном функционировании первого – второго внутренних каналов обработки информации второго конфигурируемого процессора;

-

S 23 – формирование КТ при исправном функционировании второго внутреннего канала обработки информации второго конфигурируемого процессора и первого – второго внутренних каналов обработки информации первого конфигурируемого процессора;

-

S 24 – формирование КТ при исправном функционировании первого внутреннего канала обработки информации второго конфигурируемого процессора и первого – второго внутренних каналов обработки информации первого конфигурируемого процессора;

-

S 25 – формирование КТ при исправном функционировании первого – второго внутренних каналов обработки информации первого конфигурируемого процессора;

-

S 26 – отказ бортового вычислителя.

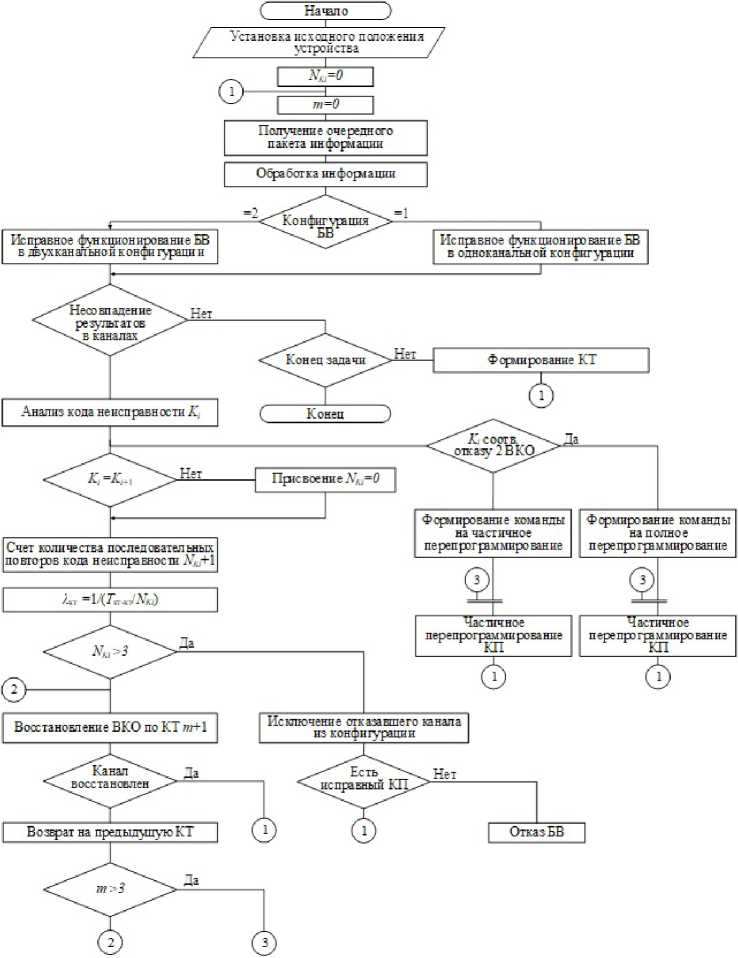

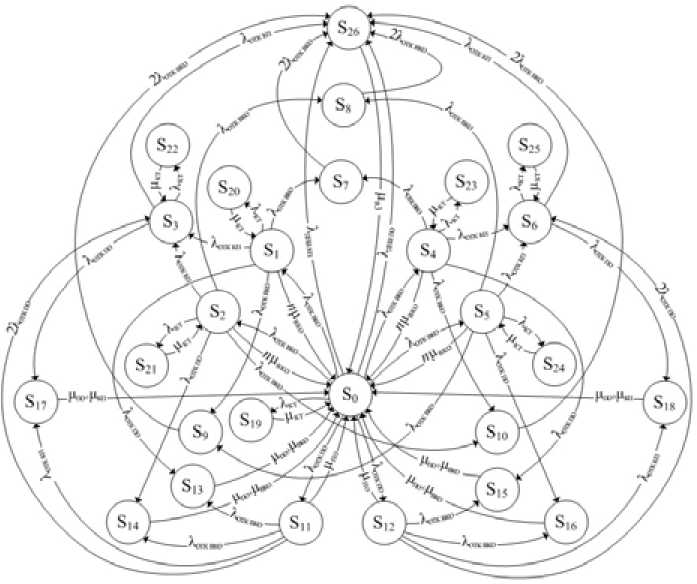

Граф переходов БВ, учитывающий интенсивности переходов, представлен на рис. 4. В соответствии с методикой расчета марковских процессов имеем следующую систему уравнений (1):

dP0( t )/ dt ( X дпатс + X дпапо + 2 X откпо + 4 X отквко + X кт ) P 0 ( t ) + n М вко P 1 ( t ) + n М вко Р2( t ) +

+ n М вко P 4( t ) + n М вко P 5( t ) + М по Р п ( t ) + М по /^ t ) + ( М по +Ц вко ) Р п ( t ) +

+ ( м по + М вко ) P 14( t ) + ( М по + М вко ) P 15( t ) + ( М по + М вко ) Р 16( t ) + ( М по + М кп ) Р 17 ( t ) +

+ ( М по + М кп ) P 18( t ) +М кт Р 21( t ) + (2 М по + 2 М кп ) Р 28( t );

dP 1( t )/ dt = - ( n М вко + 2 X отквко + X откпо + X отккп + X кт ) P 1( t ) +М кт P 22( t ) + X отквко P 0( t );

dP 2( t )/ dt = - ( n М вко + 2 X отквко + X откпо + X отккп + X кт ) P 2 ( t ) +М кт Р 2з ( t ) + X отквко P 0( t );

dP 3 ( t )/ dt = - ( X кт + X отккп + X откпо ) Р з ( t ) +М кт P 24 (t ) + X отккп Д ( t ) + X отккп Р 2 (t ) + 2 X откпо P 11 ( t );

dP 4( t )/ dt = - ( n м вко + 2 X отквко + X откпо + X отккп + X кт ) P 4 ( t ) +М кт P 25 ( t ) + X отквко P 0( t );

dP5( t )/ dt = — ( n М вко + 2 X отквко +X откпо +X отккп +X кт ) P 5 ( t ) +М кт Р 26 ( t ) + X отквко P 0 ( t );

dP 6 ( t ) / dt = — ( X кт + X отккп + X откпо ) Р б ( t ) +М кт P 27 ( t ) + X отккп Р 4 ( t ) + X отккп P 5 ( t ) + 2 X откпо P 12 ( t );

dPl (t) / dt = -2X отквкоР7 (t) + XотквкоP4 (t) + XотквкоР1 (tX dP8 (t) / dt = -2X отквкоP8 (t) + X отквкоP2 (t) + X отквко P5 (t);

d P 9 ( t ) / dt = - 2 X отквко P 9 ( t ) + X отквко P 1 ( t ) + X отквко P 5 ( tУ;

dP 10 ( t ) / dt = - 2 X отквко P 9 ( t ) + X отквко P 4 ( t ) + X отквко P 2 ( t );

dP11( t )/ dt = - (2 X отквко +X отккп +М по + 2 X откпо P n( t ) + X откпо P 0( t );

-

- d P i2( t )/ dt = - (2 X отквко +X отккп +М по + 2 X откпо ) P 12( t ) + X откпо P 0( t );

dP 13( t )/ dt = - ( М по + М вко ) P 13( t ) + X отквко Р П( t ) + X откпо P 1( t );

dP 14( t )/ dt = - ( М по +М вко ) Р 14( t ) + X отквко Р 11( t ) + X откпо Р 2 ( t У; (1)

dP 15 ( t ) / dt = - ( М по + М вко ) P 15 ( t ) + X отквко Р 12 ( t ) + X откпо Р 4 ( t );

dP16(t)/ dt = -(Мпо + Мвко)Р16(t) + XотквкоР12(t) + XоткпоР5(tУ dP17 (t) / dt = -(Мпо + Мкп )Р17 (t) + X отккпР11 (t) + X откпоР3 (t);

dP 18 ( t )/ dt = — ( М по +М кп ) Р 18 ( t ) + X отккп P 12 ( t ) + X откпо P 6 ( t );

dP 19 ( t )/ dt = —М кт Р 19 ( t ) + X кт Р 0 ( t );

dP 20 ( t )/ dt = -М кт Р 20 ( t ) + X кт Р 1 ( t );

dP 21 ( t )/ dt = —М кт Р 21 (t ) + X кт Р 2 ( t );

dP 22 ( t )/ dt = -М кт Р 22 ( t ) + X кт Р з ( t );

dP 23 ( t )/ dt = -М кт Р 23 ( t ) + X кт Р 4 ( t );

dP 24 ( t )/ dt = -М кт Р 24 ( t ) + X кт Р 5 ( t );

dP 25 ( t )/ dt = —М кт Р 25 ( t ) + X кт Р б ( t );

dP 26 ( t ) / dt = —М в3 Р 26 ( t ) + 2 X отквко Р 9 ( t ) + 2 X отквко Р 10 ( t ) + 2 X отквко Р / ( t ) +

+ 2 X отквко Р 8 ( t ) + ( X дпакп + X дпапо ) Р 0 ( t ) + X отккп Р3 ( t ) + X отккп Р 6 ( t ).

Рис. 4. Граф переходов бортового вычислителя

Fig. 4. Graph of transitions of the on-board computer

На основании полученной марковской модели бортового вычислителя на КП (рис. 4) и системы дифференциальных уравнений (1) получим показатели работоспособности системы – коэффициент готовности K Г и коэффициент оперативной готовности K ОГ .

Коэффициент готовности системы определяется по формуле

K Г( t ) = P 0( t ) + P 1( t ) + P 2( t ) + P 3( t ) + P 4( t ) + P 5( t ) + P 6( t ) + P 11( t ) + P 12( t ) + P 13( t ) + P 14( t ) + P 15( t ) + P 16( t ) + + P 17( t ) + P 18( t ) + P 19 ( t ) + P 20 ( t ) + P 21( t ) + P 22( t ) + P 23 ( t ) + P 24 ( t ) + P 25 ( t ) •

Коэффициент оперативной готовности системы для стационарного режима определяется по формуле (далее t – наработка системы)

K ОГ( t ) = P 0 ■ P 0( t ) + P 1 ■ P 1( t ) + P 2 ■ P 2( t ) + P 3 ■ P 3( t ) + P 4 ■ P 4( t ) + P 5 ’ P 5( t ) + P 6 ’ P 6( t ) + P 11 ’ P 11( t ) +

+ P 12 ■ P 12( t ) + + P 13 ■ P 13( t ) + P 14 ■ P 14( t ) + P 15 ■ P 15( t ) + P 16 ■ P 16( t ) + P 17 ■ P 17( t ) + P 18 ■ P 18( t ) +

+ P 19 ■ P 19( t ) + + P 20 ■ P 20( t ) ++ P 21 ■ P 21( t ) + P 22 ■ P 22( t ) + P 23 ■ P 23( t ) + P 24 ■ P 24( t ) + P 25 ■ P 25( t ) •

Отсюда получим:

K (t ) _ P , e ( А шакп + Л шапо + 2 ^ откпо + 2( Л >тквко1к1 + Л >тквко2кп) ' t । p , e ( Л >тквко1кп + Л >ткпо + Л >тк1вкп + А кт + n ' А вко ) ' t । p _ e (А гтквко1кп + ^ откпо + ^ отк1вкп + А кт + n 'Р вко ) ' t ^

+ P3 ' e

- ( А отк1

вкп + А откпо + А кт ) ' '

+ P 4 • e

( Л)тквко2кп +Л )ткпо +Л )тк2вкп + А кт + n ' А вко ) ' t

+ P 5 • e

( А >тквко2кг + А >ткпо + А отк2вкп +А кт + n ' А вко ) ' t

+

I p • e ( А >тк2вкп + А >ткпо + А кт) ' t ++ p • e -(2 А >тквко1кп + 2 А >ткпо + А >тк1вкп + А кт + А по ) ' t I p • e ( 2 А отквко2к1 + 2 А >ткПО + А >тк2вкП + А кт + А по) ' t +

I p t e ( А по + A вко) ' t | p t e - ( A по + A вко) ' t | p t e ( А по + A вко) ' t | p , e - ( A по + A вко) ' t | p t e ( А по + A кп) ' t |

+ pi8 • e - А по | ^ -п) 1 1 pi9 • e - " -' | p 20 • e -^ ^ • t | p 21 • e -^ ^ t | p , 2 • e - А t | p 23 • e - ^t | p 24 • e ^^ ^ t | p 25 • e -^ ^ t ,

где P 0( t ) - P 6( t ), P u( t ) - P 25( t ) - вероятности безотказной работы системы, находящейся в состояниях S о - S 6 , S 11 - S 25 .

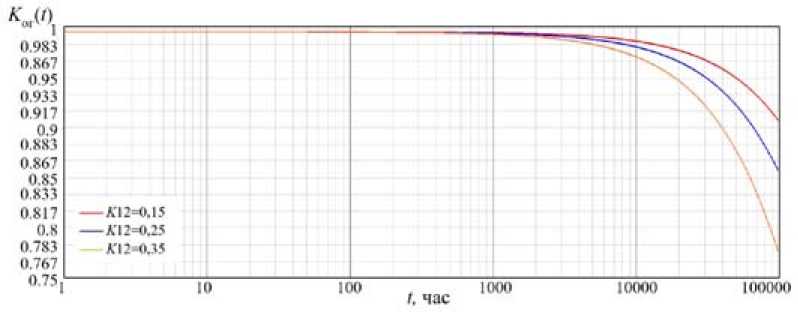

На рис. 5 представлены результаты моделирования коэффициента оперативной готовности при различных значениях коэффициентов абсолютных отказов K 12 из-за дефектов проектирования ТС и ПО, которые принимают значения 15, 25 и 35 %. При снижении доли абсолютных отказов значение K ОГ увеличивается из-за увеличения вероятности нахождения системы в исправных состояниях

Рис. 5. Графики зависимости коэффициента оперативной готовности от времени при различных значениях коэффициента абсолютных отказов

Fig. 5. Graphs of the coefficient of operational readiness of the time at different values of the coefficient of absolute failure

Результаты моделирования показали, что предлагаемый бортовой вычислитель с алгоритмом управления избыточностью будет функционировать на протяжении 100 000 ч при значении K 12 = 15 %, K ог = 0,9. Для достижения максимально эффективного применения версионно-структурного резервирования конфигурируемых процессоров в бортовом вычислителе необходимо использовать конфигурируемые процессоры, для которых коэффициент абсолютных отказов будет минимален. При этом конфигурируемые процессоры должны иметь различные версии программного обеспечения.

Список литературы Бортовой вычислитель воздушного судна на конфигурируемых процессорах

- Сельвесюк Н.И., косьянчук В.В., Федосов Е.А. Интегрированная модульная авионика. Радиоэлектронные технологии. 2015, 1, 66-71

- Меркулов В.И., канащенков А.И., Самарин О.Ф. Облик перспективных бортовых радиолокационных систем. М.: ИПРЖР, 2002. 176 с