Design Of High Performance Reconfigurable Routers Using Fpga

Автор: R.Parthasarathi, P.Karunakaran, S.Venkatraman, T.R.DineshKumar, I.Hameem Shanavas

Журнал: International Journal of Information Engineering and Electronic Business(IJIEEB) @ijieeb

Статья в выпуске: 4 vol.4, 2012 года.

Бесплатный доступ

Network-on-chip(NoC) architectures are emerging for the highly scalable, reliable, and modular on-chip communication infrastructure platform. The NoC architecture uses layered protocols and packet-switched networks which consist of on-chip routers, links, and network interfaces on a predefined topology. In this Project, we design network-on-chip which is based on the Cartesian network environment. This project proposes the new Cartesian topology which is used to reduce network routing time, and it is a suitable alternate to network design and implementation. The Cartesian Network-On-Chip can be modeled using Verilog HDL and simulated using Modelsim software.

Network-on-chip, Cartesian Network, Router, Verilog HDL, Architecture

Короткий адрес: https://sciup.org/15013138

IDR: 15013138

Текст научной статьи Design Of High Performance Reconfigurable Routers Using Fpga

Published Online August 2012 in MECS

Cartesian routing is a fast packet routing mechanism intended for geographic addresses and can effectively accelerate the packet routing process within a local or metropolitan environment. The wide area Cartesian routing described in this paper is an extension of the Cartesian routing algorithms designed to make the exchange of internet work packets between geographical regions possible. It also introduces a new hierarchical structure for the entire Internet. The proposed Internet is viewed as a hierarchy of networks consisting of routers.

At the highest level of this hierarchy, major routers exchange packets between large geopolitical areas such as countries, states, or provinces. At the lowest level of the structure, packets are routed between local routers in small geographical regions ranging from an office to a small town. There are only four layers in this structure and at each layer Cartesian routing is employed to send packets from the source router to the destination .

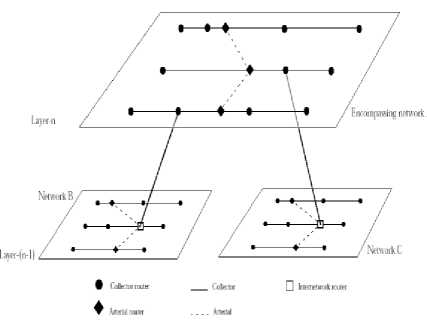

A Cartesian network consists of a set of collectors and one or more arterials

CARTESIAN ROUTER

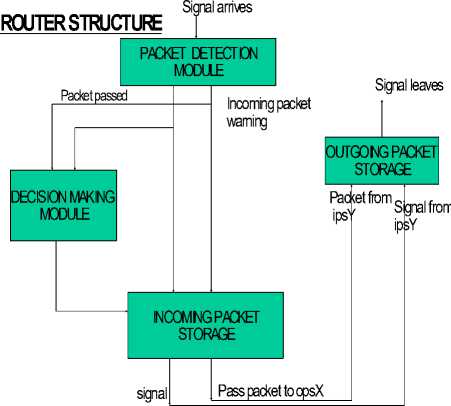

Fig: 1 Cartesian router

Each collector is a chain of collector routers running east-west and sharing common latitude. Collector routers have two side ports (east and west) to exchange packets’ horizontally’. Each collector router also has a bottom Port which allows it to connect to a set of local hosts. Arterials exchange packets between collectors.

Each arterial router, except the most northerly and the most southerly has, at least, four ports (north, south, east and west). Arterials need not share a common longitude. In a Cartesian network, the imposed topological structure relieves each router from maintaining routing tables. Each router is bound to a unique pair of addresses, the state information is minimal, and each router maintains the accessibility of arterials to its west andeast.

-

2.1 Cartesian Network Initialization

-

2.2 Cartesian Routing

-

2.3 Wide Area Cartesian Networks

In Cartesian routing, each arterial issue Arterial This Way (ATW) control packets during its initialization process. An ATW tells the receiving collector router if an arterial is accessible through the incoming port. An ATW also specifies what kind of connection is accessible via the incoming port: north, south, north and south or neither. Upon receiving an ATW, each collector router updates its Arterial Direction Indicator (ADI) and forwards the ATW to the opposite port. ATWs are also used to establish.

Virtual Arterials, constructed in situations where it is physically impossible for an arterial to span two collectors. The ADI points in the direction of the arterial router (i.e., east or west) and indicates whether the arterial router has a connection to the north, the south, or both. Figure 1 illustrates a Cartesian network.

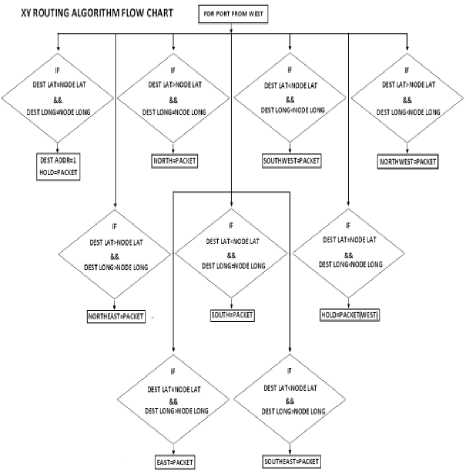

Packets can arrive on either a west or east port of a collector router. Packets intended for different latitude are forwarded out the opposite port from which they are received.

The ADI determines the packet’s initial direction on the collector router when a packet arrives on the bottom port of a collector router. In deciding a packet’s initial direction, the router first compares the packet’s destination address with its own address. The packet will be forwarded in the direction of the destination if the

Table 1:4-port routing algorithm

Список литературы Design Of High Performance Reconfigurable Routers Using Fpga

- Lee, Se-Joong Lee, and Hoi-Jun Yoo, "Low-Power Network-on-Chip for High-Performance SoC Design Kangmin" "IEEE transactions on very large scale integration (vlsi) systems," vol. 14, no. 2, february 2006.

- W. Dally et al., "Route packets, not wires: On-chip interconnection networks,"in Proc. Des. Autom. Conf., Jun. 2001, pp. 684–689.

- L. Benini et al., "Networks on chips: A new SoC paradigm," IEEE Computer,vol. 36, no. 1, pp. 70–78, Jan. 2002.

- D. Bertozzi et al., "Xpipes: A network-on-chip architecture for gigascale system-on-chip," IEEE Circuits Syst. Mag., vol. 4, no. 2, pp. 18–31,2004.

- E. Rijpkema et al., "Trade offs in the design of a router with both guaranteed and best-effort services for networks on chip," in Proc. Des., Autom. Test Europe Conf., Mar. 2003, pp. 350–355.

- V. Nollet et al., "Operating-system controlled network on chip," in Proc. Des. Autom. Conf., Jun. 2004, pp. 256–259.

- C. Wu and H. Chi, "Design of a high-performance switch for circuit-switched on-chip networks," in Proc. Asian Solid-State Circuits Conf. , 2005, pp. 481–484.

- M. A. Al Faruque, T. Ebi, and J. Henkel, "ROAdNoC: Runtime observability for an adaptive network on chip architecture," in Proc. IEEE/ACM Int. Conf. Comput.-Aided Des. (ICCAD) , 2008, pp. 543–548.

- H. Jingcao, U. Y. Ogras, and R. Marculescu, "System-level buffer allo-cation for application-specific networks-on-chip router design," IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. , vol. 25, no. 12, pp. 2919–2933, Dec. 2006.

- Y.-C. Lan, S.-H. Lo, Y.-C. Lin, Y.-H. Hu and S.-J. Chen, "BiNoC: A bidirectional NoC architecture with dynamic self-reconfigurable channel," in Proc. Int. Symp. Netw.-on-Chip, 2009, pp. 266–275.

- C. Xuning and L. Peh, "Leakage power modeling and optimization in interconnection networks," in Proc. Int. Symp. Low Power Electron.Des. (ISLPED), 2003, pp. 90–95

- M. Vestias and H. Neto, "Router design for application specific network-on-chip on reconfigurable systems," Field Program. Logic Appl., vol. 1, pp. 389–394, 2007