Детектирующая тестовая последовательность для магистральных структур в системах с оперативной памятью

Автор: Гаврилин Борис Николаевич, Выборное Петр Владимирович

Статья в выпуске: 23 (240), 2011 года.

Бесплатный доступ

Предлагается тестовая последовательность обнаружения и разделения неисправных состояний подсистемы «магистраль - внешняя память» вычислительного ядра БЦВМ. Сжато излагаются также некоторые новые подходы и принципы, использованные при построении алгоритма диагноза.

Тестовая последовательность, диагностика отказов, оперативная память

Короткий адрес: https://sciup.org/147154756

IDR: 147154756 | УДК: 623.618

Detecting test sequence for the main structures in systems with ram

Test sequence for the detection and separation of faulty states of the subsystem «main transmission line - external memory» for on-board computer processing core has been proposed. Briefly presented some new approaches and principles used in constructing the diagnostic algorithm.

Текст научной статьи Детектирующая тестовая последовательность для магистральных структур в системах с оперативной памятью

Проверки, которые производятся после изго-товления модулей бортовой цифровой вычисли-тельной машина (БЦВМ) и в ходе их испытаний, показали, что 70‒90 % всех неисправностей при-ходится на вычислительное ядро . Эти неисправно-сти подразделяются на три группы: 1) дефекты демультиплексированной параллельной магистра-ЛИ ( дпм), или, что то же самое, неисправности * связей между процессором и внешней памятью; 2) дефекты кристаллов внешней памяти; 3) дефек-ты, относящиеся к работе микропроцессора. Доля магистральных дефектов среди всех дефектов вы-числительного ядра составляет 85‒90 %. Традици-онно для тестирования подсистемы «магистраль ‒ внешняя память» применяются программы, ори-оптированные преимущественно на проверку са-мих кристаллов памяти [1, 2]. Эти тесты обнару-живают факт неработоспособности подсистемы в целом, в том числе и из-за дефектов связей, однако являются малоинформативными с точки зрения определения неисправного состояния. Практиче-ски такая потребность существует именно в отно-шении магистральных дефектов, а также разделе-ниягрупп 1и 2.

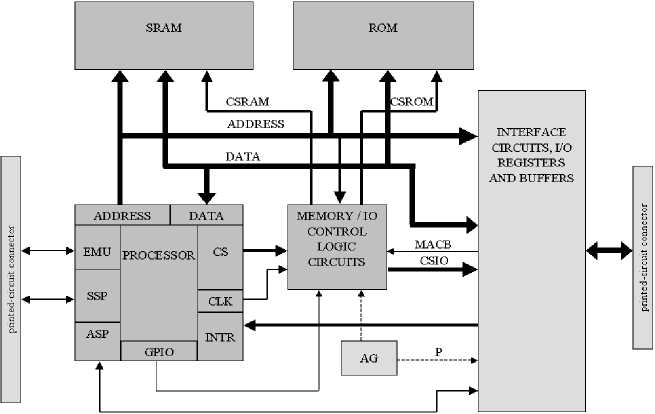

Объект диагностики . Вычислительное ядро модуля состоит из процессора PROCESSOR, логи-ки формирования сигналов управления MCLC, магистральных шин адреса ADDRESS, данных DATA и управления CS, статической оперативной памяти произвольного доступа SRAM и какого-либо типа постоянной (энергонезависимой) памя-ти с параллельным доступом ROM (рис. 1). Шина управления, как правило , расщепляется путём ло-гического комбинирования процессорных стробов CS c некоторыми разрядами адреса или битами MACB регистра ввода-вывода. В простейшем слу-чае логика MCLC может отсутствовать, тогда сиг-налы управления памятью являются процессор-ными стробами в чистом виде.

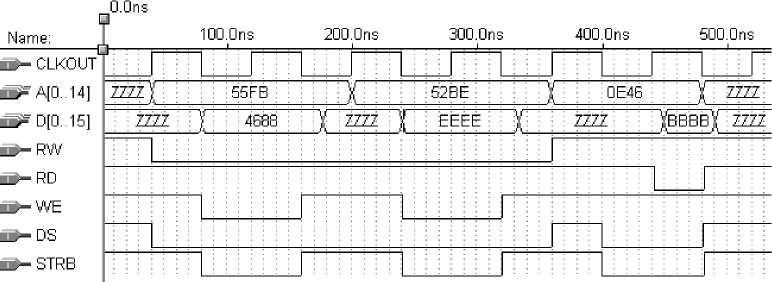

Рассмотрим типовые временные диаграммы сигналов демультиплексированной синхронной магистрали, имеющей 16-разрядную шину адреса и 16-разрядную шину данных D[0…15] (ZZZZ обозначает пассивное состояние шины) (рис. 2). Во время конвейерных циклов выборки команды или чтения(read)/записи(write) операндов из/в внешней памяти процессорный контроллер маги-страли по сигналам дешифратора команд уста-

Рис. 1. Функциональная схема вычислительного модуля БЦВМ

навливает адрес A[0…15], мультиплексируя одну из внутренних адресных шин процессора наружу, и уровни сигналов управления, заставляя память выставить данные или стробируя запись данных из процессора в память. Назначение сигналов управ-ления : WE ‒ запись (по возрастащему фрону), RD ‒ строб чтения, R/W ‒ селектор чтения/записи, STRB ‒ общий строб доступа по магистрали, DS ‒ строб доступа к адресному пространству данных, CLKOUT ‒ тактовая частота магистрали (в данном примере 12,5 МГц).

Допустим, что для физической адресации яче-ек SRAM 32K*16 использованыA[0…14], а разряд A15 используется как сигнал управления для фор-мирования строба доступа к микросхеме, напри-мер, согласно уравнению CE=A15 OR DS. На вы-воды WE (write enable) и OE(out enable) микросхемы SRAM заведены процессорные стробы WE и RD.

Сигналы и классы неисправностей . Все сигналы диагностируемого модуля разбиваются на пять функциональных групп: 1) CS ‒ линии пита-ния микросхем подсистемы и образующие по форме временной диаграммы шесть подгрупп сиг-налы управления памятью, к которым относятся процессорные стробы, тактовая частота магистра-

ЛИ, управляющие адресные разряды, биты регист-ров I/O доступа к памяти MACB и производные перечисленных сигналов; 2) A ‒ адресные разряды магистральной шины, участвующие в физической адресации ячеек памяти; 3) D ‒ линии данных; 4) F ‒ внешние сигналы постоянного уровня; 5) P ‒ периодические несинхронизированные с CLKOUT внешние сигналы, производные непро-цессорных генераторов, если они есть в устройст-ве (AG на рис. 1). Группы 1, 2 и3 образуют маги-стральные сигналы (I), группы 4и5 ‒ внешние (E).

Физическими дефектами нашего объекта яв-ляются : -ду собой (SH-I1-I2-…) или со сторонними сигна-лами (SH-I-E), обрывы сигнальных линий и отсут-ствие питания микросхем памяти и управляющей логики (BR-I), общие для подсистемы дефекты логических элементов MCLC и сигнальных трак-ТОВ (SPF-CS), дефекты переключения сигналов (SWF-I), вызванные высоким сопротивлением сиг-нальных цепей, и дефекты кристаллов памяти (MCD). Все возможные одиночные неисправности подсистемы принадлежат к одному из следующих классов , выделяемых соответственно функции сигнала(-ов):

Рис. 2. Временные диаграммы магистральных сигналов (write-write-read)

-

1) BR-CS ‒ обрывы сигналов управления и питания от микросхем SRAM;

-

2) SH-CS-A ‒ замыкания CS с линиями A;

-

3) SH-CS-D ‒ замыкания CS с линиями D;

-

4) SH-CS-F ‒ замыкания CS с внешними ли-НИЯМИ постоянного уровня F;

-

5) SH-CS-P ‒ замыкания CS с периодически-ми сигналами P;

-

6) SPF-CS ‒ статические дефекты тракта фор-мирования сигнала CS;

-

7) SWF-CS ‒ дефекты переключения CS;

-

8) BR-D ‒ обрывы разрядов данных;

-

9) SH-D-A ‒ замыкания между линиями дан-ных и адреса;

-

10) SH-D-D ‒ замыкания линий данных ;

-

11) SH-D-F ‒ замыкания разрядов данных c линиями постоянного уровня;

-

12) SH-D-P ‒ замыкания линий данных с сиг-налами группы P;

-

13) SWF-D ‒ дефекты переключения разрядов данных;

-

14) BR-A ‒ обрывы разрядов адреса;

-

15) SH-A-A ‒ замыкания между линиями ад-реса;

-

16) SH-A-F ‒ замыкания линий адреса c ЛИ-НИЯМИ постоянного уровня;

-

17) SH-A-P ‒ замыкания с сигналами группы P;

-

18) SWF-A ‒ дефекты переключения разрядов адреса;

-

19) MCD ‒ дефекты кристалла SRAM.

Класс образуется одним или несколькими ви-дами неисправностей. Вид есть типовое связанное искажение уровней определённых сигналов, в ряде случаев сопровождающееся и нарушением работы электронных схем, для которых эти сигналы явля-ются входными . Например, ВИДЫ SH-WE-A[x], SH-RD-A[x], SH-CE-A[x], SH-A[15]-A[x], SH-DS-A[x] и SH-CLKOUT-A[x] составляют класс SH-CS-A. Искажение уровней вызывается либо дефектами сигнальных линий, либо кристальными дефектами памяти (MCD) и элементов магистральной логики (часть дефектов SPF). Как будет показано ниже, приведённая функциональная классификация в ос-новном совпадает с разбиением видов дефектов на ранжированные группы и характеризует влияние дефектов на обмены с памятью с точки зрения про-цессораи, следовательно , способ их обнаружения.

Логические типы магистральных дефек-тов.В [3] было показано, что использование толь-ко классических OR- и AND-моделей замыканий и константных моделей обрывов [4] недостаточно для описания поведения подсистемы, так как в неисправном состоянии она может утрачивать свой детерминизм. Поэтому логические типы за-мыканий были дополнены неопределённым со-:

-

S0 (suppressing 0) ‒ устанавливается потенци-ал , всегда воспринимаемый приёмником как ус-тойчивый лог. 0 (может быть и выше стандартного Uвх0max);

S1 (supressing 1) ‒ устанавливается потенциал, всегда воспринимаемый приёмником как устойчи-вая лог. 1 (может быть и ниже стандартного U 1min);

INDTL (indetermined level) ‒ результирующий потенциал приёмником воспринимается неустой-чиво : . 1, то как лог. 0 в течение одного цикла или в разных циклах.

Аналогичным образом логические типы об-:

H1 (hanging 1) ‒ вход микросхемы ведёт себя так, как будто на него подана постоянная лог. 1;

H0 (hanging 0) ‒ вход микросхемы ведёт себя так, как будто на него подан постоянный лог. 0;

HSSW (hanging self-switching input) ‒ вход самопроизвольно переключается из-за наводок в кристалле, воспринимается неодинаково при об-ращениях с разными наборами на шине адреса, чтении и записи или изменяется в течение одного обращения.

Модели неисправностей . Пусть

Z =Т(X, Yn‒1, n) ‒ некоторая форма представления передаточной функции исправного дискретного последователь-ностного объекта диагностики (E0), где X ‒ набор входных переменных в цикле n; Yn‒1 ‒ значение внутренних переменных после фронта записи в элементы памяти в цикле n‒1; Z ‒ выходные функции в цикле n после определённого времени установки выходов. Легко определить, что эта функция для подсистемы «магистраль ‒ оператив-ная память» :

Dr[A](n) = Dm[A’](n) = Dp[A](i = max(0, n‒1)), где Dr[A](n) ‒ данные , читаемые процессором в n-цикле из адреса A; Dm[A’](n) ‒ содержимое ячейки с физическим адресом A’, однозначно соотносимым с магистральным адресом A; Dp[A](i = max(0, n‒1)) ‒ данные, выставляемые процессором на магистраль в i-цикле записи в па-мять по адресу A, i-цикл является последней запи-сью по адресу A.

Объект, находящийся в i-неисправном со-стоянии (Ei), которому соответствует одиночный дефект1 Si, реализует передаточную функцию Zi = Тi(X, Yn‒1, n). Функция Zi с входным набором Xt = {A, Dp} и, возможно, значением внутренних переменных Yn‒1 описывает элементарную про-верку лt, результат которой принято обозначать Rti. Такие функции с необходимыми наборами Xt (об их выборее далее) составлялись в виде синтак-сических диаграмм записи-чтения для каждого вида магистрального дефекта и его логического типа [3]. Синтаксическая диаграмма является тек-стовым представлением поведения объекта, кото-рое получается, если вместо временных диаграмм исправных сигналов (см . рис . 2) подставить диа-граммы неисправных и проследить работу памяти в этих условиях.

Методика разбиений . Если множество до-пустимых одиночных неисправностей объекта S, а множество их сочетаний ‒ C (SСC), то фактиче-ская j-неисправность подсистемы в общем случае представляется Cj = Sk + Sl + … + Sp, причём на дефекты Sk…Sp не налагается ограничений по чис-лу и видовой принадлежности. Особенностью сис-тем с неоднородными сигналами является то, что детектирующие проверки для некоторого подмно-жества неисправностей могут быть осуществлены только при отсутствии некоторых других их под-множеств. Для выбора последовательности прове-рок, обнаруживающих любые неисправности при наличии произвольных их сочетаний, нами пред-ложен принцип разбиения на ранжированные под-множества и маскирования дефектов подчинённых рангов.

Принцип состоит в следущем :

S группируется в непересекающиеся ранжирован-ные подмножества Ft (t ‒ ранг подмножества) та-ким образом, чтобы любой одиночный дефект подмножества текущего ранга можно было обна-ружить при отсутствии дефектов старших рангов и независимо от наличия или отсутствия любых де-фектов из подмножеств подчинённых рангов. Са-мым старшим рангом является первый, для него все остальные подмножества, имеющие ранг t > 1, являются подчинёнными. Критерием включения простого дефекта Si в подмножество старшего ранга Ft из исходного F’, ранг которого принима-ется равным t+1, является возможность физически осуществить и однозначно интерпретировать та-кую элементарную проверку, которая при наличии любых других дефектов ранга t+1 даст результат Rt (ответ исправного объекта) при отсутствии Si и Rti * Rt ‒ при его наличии.

Таким образом, сначала берется исходное множество F’=S, t=1 и выделяется F1, затем t=2, F’=S‒F1 и уже из нового F’ выделяется группа дефектов F2 и так далее вплоть до последнего класса или вида дефектов. В результате примене-ния этой процедуры исходное множество разбива-ется на v подмножеств Ft (t = 1, 2, …, v) так, что S=F1 и F2 и… Fv. Каждому подмножеству Ft соответствует свой этап теста, предназначенный для обнаружения и определения дефектов только из этого подмножества. Этапы теста выполняются поочерёдно в ранговом порядке соответствующих подмножеств, начиная с самого старшего (t=1) И кончая младшим (t= ). Основная тестовая после-довательность состоит из детектирующих прове-рок для каждого подмножества Ft; в неё не вклю-чаются части этапов, выполняющих окончатель- ное разделение и определение дефектов внутри подмножества. Иными словами, это путь по графу алгоритма диагноза от состояния «полностью не-определённо» до «исправно».

Главная тестовая последовательность. Ал-горитмы детектирующих проверок каждого этапа представлены в виде Фортран-подобного псевдо-кода; для примера взята простая подсистема, ОПИ-санная в начале . :

Адреса ячеек SRAM: AD0=0000h ‒ нижней (нулевой), ADF=7FFFh ‒ верхней;

RPT nw: X0—>(AD0)…nw сопряжённых запи-сей числа X0 по адресу AD0;

RPT nr: A[I=0…nr‒1]<—(AD0)…nr чтений в массив A из адреса AD0;

sdc (settle down cycles) ‒ количество циклов, по прошествии которых считается, что дефекты переключения перестают проявляться.

Операторы вида IF(Rti#Rt) GOTO FIND_xx | FAILURE_xx ‒ переход на подпрограмму опреде-ления неисправностей внутри детектированного подмножеств Ft (c локализующими проверками | без дополнительных проверок).

EAED: F1={SPF-CS, BR-CS, SH-CS-A, SH-CS-D, BR-D, SH-CS-F, SH-CS-P, SH-D-F, SH-D-P}. Выявление дефектов F1 производится последова-:

-

1) после многократной записи по адресу A0 RAM числа D0 это же самое число D0 правильно читается процессором, начиная с цикла sdc+1;

-

2) после многократной записи по адресу A1 RAM числа D1 это же самое число D1 правильно читается процессором, начиная с цикла sdc+1 .

Входные переменные обеих проверок связаны следующим образом: A1=NOT A0, D1=NOT D0, A0 и D0 берутся произвольно . Инверсные значе -НИЯ Aи Dp обеспечивают обнаружение замыканий SH-CS-A и SH-CS-D с любыми подгруппами CS, а инверсия данных, кроме того, ‒ также и с BR-D и SH-D-F. Многократное чтение необходимо для достоверного обнаружения замыканий INDTL-ТИПОВ, а также замыканий CS иD с сигналами P.

Любые замыкания разрядов адреса между со-бой типа SH-A[x](1)-A[y](0)(…-A[z]), а также с другими сигналами SH-A[x](0)-D[y](1), SH-A[x](1)-F(0), SH-A[x]-P и обрывы адреса BR-A[x] могут приводить уровень на этих разрядах Aв зону неопределённости (неустойчивости). В таком случае неизвестен не только определённый адрес попадания, что само по себе не представляет осо-бого неудобства, но и то, постоянен ли адрес в пределах цикла. Непостоянство адреса в пределах цикла приводит к практически непредсказуемой порче как записываемых, так и читаемых данных ‒ в том смысле, что случайным образом изменяются все разряды D. Маскирование подобных дефектов делается применением наборов {A0=0000h, D0=0000h} и {A1=7FFFh, D1=FFFFh}, полностью исключающих возможную неустойчивость из-за SH-A[x]-A[y](…-A[z]) и SH-A[x]-D[y].

EAED:

-

- RPT nw: 0000h—>(AD0)..............(1)

-

- RPT nr: A[I=0…nr‒1]<—(AD0)...(2)

-

- YA=A[sdc]

-

- DO I=sdc+1, nr‒1

-

- YA=YA OR A[I]

-

- END DO

-

- IF(YA#0000h) GOTO FAILURE_AD0_X0

-

- RPT nw: FFFFh—>(ADF)..............(3)

-

- RPT nr: A[I=0… nr‒1]<—(ADF)...(4)

-

- YB=A[sdc]

-

- DO I=sdc+1, nr‒1

-

- YB=YB AND A[I]

-

- END DO

-

- IF(YB#FFFFh) GOTO FAILURE_ADF_XF

Для избежания влияния возможной несла-бильности адреса из-за BR-A, SH-A-F и SH-A-P, а также для маскирования SWF применена много-кратная запись, которая помещает значения 0000h (1) и FFFFh (3) во все ячейки, куда они в принципе могут попасть. Многократное чтение позволяет определить, получаем мы значения 0000h и FFFFh из памяти устойчиво или нет. Результаты каждой элементарной проверки ‒ массивы, получаемые в (2) и (3), ‒ подвергаются поэлементным логиче-ским OR и AND, результаты которых позволяют за одно сравнение обнаружить неисправность. OR собирает хотя бы раз полученные по каждому раз-ряду лог.1, AND ‒ лог.0; любое из этих событий означает Rit # Rt. Если в (2) получено только зна-чение 0000h, а в (4) ‒ FFFFh, то это значит, что дефекты F1 отсутствуют : N0 по адресу A0 и

- N1 по адресу A1 были правильно записаны и мно-гократно считаны из памяти, за исключением, возможно, sdc первых циклов.

CSSW: F2={SWF-A15, SWF-DS, SWF-CE}. Дефекты переключения сигналов управления вы-зывают провалы обращения к памяти после пере-: в течение какого- строб CE не достигает уровня лог. 0, и хотя бы первое чтение будет произведено с пассивной ши-ны . Элементарные проверки этого этапа представ-ляют собой следующую последовательность дей-ствий : ‒ установка логических элементов MCLC в нерабочее состоя-ние изменением одного из входных сигналов, A15 ИЛИ DS, и чтения при отключенном режиме (для сохранения уровня второго сигнала) или ожидание длительностью N магистральных циклов, установ-ка проверяемого сигнала в активное состояние и однократное чтение в этом же цикле. При этом все линии физической адресации памяти A[0…14] во время выполнения проверки необходимо поддер-живать в неизменном уровне, чтобы SWF-A не повлияли на эксперимент. Если известно значение VPB, читаемое с пассивной шины данных ‒ допус-ТИМ , это FFFFh, ‒ следует ограничиться чтением из адреса, значение в котором отличается от VPB(AD0).

CSSW:

-

- RPT nr: YA<—(8000h) !инвертированный

бит A15, чтение с пассивной шины

-

- YB <—(AD0)

-

- RPT nr: YC<—(AD0(PS)) !обращение по тому же адресу, но в пространстве кода

-

- YD <—(AD0(DS)) !снова чтение из

пространства данных

-

- IF((YB*0000h) AND (YD*0000h)) GOTO FAILURE_SW_CE

-

- ELSE IF (YB*0000h) GOTO FAILURE_SW_A15

-

- ELSE IF (YD*0000h) GOTO FAILURE_SW_DS

Стробы RD и WE переключаются в калщом цикле чтения и записи, поэтому SWF-RD и SWF-WE неотличимы от их статических дефектов и обнаруживаются на предыдущем этапе EAED.

EAND: F3={SH-A[x]-D[y]}. Данный класс за-мыканий обнаруживается записью по AD0 числа Dp[FFFF] И по ADF ‒ Dp[0000]. Правильный ре-зультат при S0 и S1 ни в какой из этих двух комби-наций получить невозможно . Логические типы за-мыкания при чтении и записи могут отличаться, но если при записи тип S0 или S1, то отличие не играет никакой роли. A[x] и D[y] при записи имеют одина-ковый и определённый уровень (лог. 0 ИЛИ лог. 1), и происходит одно из двух:

пишется в неправильную ячейку , либо в правиль-ную ячейку пишется число с искажённым разрядом D[y]. В первом случае мы прочитаем из адреса ADF ИЛИ AD0 прежнее значение, FFFFh ИЛИ 0000h, на-ходящееся там после прохождения EAED, во вто-ром ‒ читаем число с искажённым D[y]. В обоих случаях здесь при чтении Ar[x]=Dm[y].

Для INDTL-типа возможно разное логическое восприятие одного уровня двумя разными приём-никами,т.е. при записи фактический адрес Aw[x] может быть не равен D[y] (в случаях S0 и S1 это невозможно). Поэтому необходимо рассматривать запись по A[x]=0 разряда D[y] и нулём, и едини-цей, то же самое и для A[x]=1 ‒ возникают альтер-нативы, не сводящиеся к простой комбинации чте-ния и записи при S0 и S1. Однако применяя обе комбинации A-D, можно c достаточной опреде-лённостью утверждать, что INDTL также не даст правильного значения хотя бы в одной из них.

Кроме целевого SH-A-D, к неправильной за-писи может привести SWF-A, а также нестабиль-ность адреса из-за BR-A=INDTL, SH-A-F=INDTL, а также из -за SH-A-P. Поэтому для их маскирова-ния поступаем здесь аналогично EAED ‒ делаем запись многократной (1) и (3).

EAND:

-

- RPT nw: FFFFh—>(AD0)(1)

-

- YF <—(AD0)(2)

-

- RPT nw: 0000h—>(ADF)(3)

-

- Y0<—(ADF)(4)

-

- IF((YF*FFFFh) OR (Y0*0000h)) GOTO FIND_ADSHB

ADDRSTB: F4={BR-A=INDTL, SH-A-F=INDTL, SH-A-P}. (1)(3)

EAND,

AD0,

FFFFh, ,- пись при обращении по ADF, - число 0000h. Устойчивость адреса, а именно тот факт, что запись

-ходят из одной и той же ячейки (не путать с правильностью адреса ) определяется так: один раз (1, 3), -

, (2, 4).

ADF FFFFh,

AD0 ‒ 0000h,‒

.- ном случае из другой возможной ячейки будет

,

(1) (3) EAND.‒ изменяющимся уровнем на входах микросхемы ‒;

EAA. только устанавливаются флаги нестабильности , A0_INSTB

AF_INSTB.

ADDRSTB:

-

- A0_INSTB=.FALSE., AF_INSTB=.FALSE.

-

- RPT nr: YA (ADF) ! SWF-A

-

- FFFFh (ADF)..............................(1)

-

- RPT nr: A[I=0…nr‒1] (ADF).....(2)

-

- YA=A[sdc]

-

- DO I=sdc+1, nr‒1

-

- YA=YA AND A[I]

-

- END DO

-

- IF(YA FFFFh) AF_INSTB=.TRUE.

-

- RPT nr: YA (AD0) ! SWF-A

-

- 0000h (AD0)...............................(3)

-

- RPT nr: A[I=0…nr‒1] (AD0).....(4)

-

- YA=A[sdc]

-

- DO I=sdc+1, nr‒1

-

- YA=YA OR A[I]

-

- END DO

-

- IF(YA 0000h) A0_INSTB=.TRUE.

EAA: F5={SH-A[x]-A[y](…-A[z]), BR-A[x], SH-A[x]-F}. INDTL - жадресного замыкания произвольной кратности SH-A[x]-A[y](…-A[z]).- x, y, …

( ) ()

( ) --

, .-

-

x, y, …:

программной установке всех разрядов адреса в ‒ AD0 ADF.

, , LMA UMA.‒

,-

H1

SH-A-F=1, ,-

.‒

,-

-

, ,H0

SH-A-F=0.

n LMA UMA-

2n.

комбинации нулей и единиц в замкнутых разрядах

‒-

1 ‒,

‒

, . .

S0 S1.

W1 (walking 1)2, 1-

,-

BRNLMA ‒

S0, ‒S1.

В последнем случае оно обязательно попадёт в UMAW0.

LMA W1,

UMA W0,

;

UMA, LMA.

LMA, UMA. W1 W0

A[x], ,

LMA, UMA.

EAA:

-

- ECN=0000h, BRN=FFFFh, UAB=14 ! разряд адреса

-

- B1=0001h!

-

()

-

- FBW1=0000h, FBW0=0000h

-

- DO I=0, UAB

-

- ADW1=B1! W1-

- - ADW0=(NOT B1) AND 7FFFh ! W0-

- - RPT sdc+1: ECN (AD0)(1)

-

- RPT sdc+1: ECN (ADF)(2)

-

- RPT nw: BRN (ADW1)(3)

-

- RPT nw: BRN (ADW0)(4)

-

- RPT sdc+1: RBV1 (AD0)

-

- IF(RBV1 ECN) FBW1=FBW1 OR B1

-

- RPT sdc+1: RBV0 (ADF)

-

- IF(RBV0 ECN) FBW0=FBW0 OR B1

-

- B1=SHFL(B1,1)!

-

- END DO

-

- FB=FBW0 OR FBW1 !-

- ные разряды в одну переменную

-

- IF(FB 0) GOTO FIND_EAA

W1(3) W0(4)-

LMA UMA ECN(1 2),

BRN

ADW1 ADW0-

.

может быть как переписью числом BRN, так и лю -бым искажением, поскольку при записи с пере-ключением адреса внутри цикла asw (см . атрибу-ты записи на синтаксических диаграммах) данные могут искажаться непредсказуемым образом; ДЛЯ большей надёжности лучше брать ECN=NOT BRN. Поскольку на этом этапе ещё ничего не из-вестно о наличии замыканий SH-D-D, нужно взять ECN=0000h, BRN=FFFFh. Неисправный разряд A[x], детектированный операцией W1 ИЛИ W0, заносится в соответствующие переменные FBW1 и FBW0. Определение дефектов ‒ групп замыканий и обрывов ‒ осуществляется в процедуре FIND_EAA с помощью комбинаторных алгорит-мов связывания неисправных разрядов.

ADDRSW: F6={SWF-A, SWF-D}. Для каждого разряда адреса A[x] при неизменных остальных производятся сопряжённые чтения попеременно из адресов с A[x]=0 и A[x]=1. Для проверки переклю-чения необходимо длительность магистральных циклов установить минимальной, а чтение произво-дить в циклах, следующих непосредственно друг за другом. После записей (1)‒(4) этапа EAA в ячейках LMA и UMA содержится 0000h, а во всех ячейках с адресами ADW1 и ADW0 ‒ FFFFh. Для определе-НИЯ F6 достаточно использовать один из наборов адресов, возьмём LMA+ADW1. Если в переключа-тельной последовательности из каждого ADW1 получаем только FFFFh (2), а из LMA ‒ только 0000h (1), то SWF-A и SWF-D отсутствуют. В про-тивном случае в позиции текущего разряда A[x] устанавливается 1 в переменной SWFA_10 (ошибка при чтении LMA ‒ A[x] переключался из 1в 0) ИЛИ SWFA_01 (ошибка при чтении ADW1 ‒ A[x] пере-ключался из 0в 1). Получаемые OR- и AND-значения для каждого разряда сохраняются в мае-сивах V0(3) и VF(4); по этим значениям можно су-дить какой неисправностью ‒ SWF-A ИЛИ SWF-D ‒ вызвано конкретное несравнение .

ADDRSW:

-

- SWFA_10=0000h, SWFA_01=0000h

-

- B1=0001h !проверяемый разряд адреса

-

- DO CB=0, UAB

-

- ADW1=B1

-

- DO I=0, nr‒1

-

- A[2*I]<—(LMA)………………..…(1)

-

- A[2*I+1]<—(ADW1)……………...(2)

-

- END DO

-

- DO I=0, nr‒1

-

- V0[CB]=A[2*I] OR 0000h……….(3)

-

- VF[CB]=A[2*I+1] AND FFFFh….(4)

-

- END DO

-

- IF(V0[CB]*0000h) SWFA_10=SWFA_10

OR B1

-

- IF(VF[CB] ф FFFFh) SWFA_01=SWFA_10

OR B1

-

- END DO

-

- IF((SWFA_10 OR SWFA_01)*0) GOTO FAILURE_SWA

EDD: F7={SH-D[x]-D[y]-(…-D[z])}. Неисправ-ные разряды обнаруживаются либо W1, либо W0 по разрядам D, адрес здесь значения не имеет. Если обратиться к синтаксическим диаграммам SH-D-D, то будет видно , что правильный результат при ло-гических типах S0 и S1 ни в W1, ни в W0 получить нельзя :

сам, а в другом читается правильно, но искажается другой, замкнутый с ним. При INDTL-типе (про -цессорных драйверов) ДЛЯ SH-D[x]-D[y] возможна, хотя и маловероятна, запись в память по разным разрядам разных значений. Тогда результат чтения будет зависеть от результирующего уровня вы-ходных буферов памяти, который может быть лю-бым. Теоретически процессор может прочитать разряды xиy в любой комбинации {11,00,10,01}, из которых 10 правильная, хотя разное восприятие одного и того же уровня двумя элементами одной микросхемы всё же маловероятно . Такие досто-верно не исключаемые события будем отсеивать совместным применением W1 и W0. Процедура FIND_EDD, определяющая группы замыкания, использует только алгоритм полного связывания, поэтому все неисправные разряды, детектирован-ные как W1, так и W0, запоминаются в одной пе-ременной SDB.

EDD:

-

- XD1=0001h, SDB=0000h, UDB=15 !старший разряд данных

-

- DO I=0,UDB

-

- XD0=NOT XD1

-

- XD1—>(AD0) ! запись W1

-

- Y1<—(AD0)

-

- XR0—>(AD0) ! запись W0

-

- YR0<—(AD0)

-

- IF((Y0^XD0) OR (Y1^XD1)) SDB=SDB

OR XD1

-

- XD1=SHFL (XD1,1) !сдвиг текущего разряда данных на 1 влево

-

- END DO

-

- IF(SDB#0) GOTO FIND_EDD

После прохождения всех семи этапов (EAED… ‒ EDD) диагностируемая подсистема не может иметь магистральных дефектов, что даc возможность однозначно интерпретировать ре-зультаты кристалльных тестов SRAM.

Список литературы Детектирующая тестовая последовательность для магистральных структур в системах с оперативной памятью

- Уильямс, Г.Б. Отладка микропроцессорных систем/Г.Б. Уильямс. -М.: Энергоатомиздат, 1988. -С. 49.

- Van de Goor, A.J. Testing semiconductor memories: Theory and practice/A.J. van de Goor. -Chichester: J. Wiley & Sons, UK, 1991.

- Выборное, П.В. О подходах к составлению диагностических тестов вычислительного ядра БЦВМ/П.В. Выборнов, Б.Н. Гаврилин//Вопросы оборонной техники. -2010. -Серия 9. -№ 1

- Feng, C. A new diagnosis approach for short faults in interconnects/C. Feng, W.K. Huang, F. Lombardi//Proc. IEEE fault-tolerant computing symp. -1995. -June -P. 331-339.