Hybrid Decoder Reconfiguration of AVS-P7 and MPEG-4 /AVC in the Reconfigurable Video Coding Framework

Автор: Yang Gaobo, Xiang Renhua, Zhang Zhaoyang

Журнал: International Journal of Image, Graphics and Signal Processing(IJIGSP) @ijigsp

Статья в выпуске: 8 vol.4, 2012 года.

Бесплатный доступ

With the rapid development of video coding technology, all kinds of video coding standards have been advanced in recent years with a variety of different and complex algorithms. They share common and/or similar coding tools, yet there is currently no explicit way to exploit such commonalities at the level of specifications or implementations. Reconfigurable video coding (RVC) is to develop a video coding standard that overcomes many shortcomings of current standardization and specification process by updating and progressively incrementing a modular library of components. In this paper, a hybrid decoder reconfiguration is instantiated in the RVC framework by grouping the coding tools from AVS-P7 and MPEG-4/AVC. Experimental results show that compared with MPEG-4/AVC baseline profile, the reconfigurable coding system reduces the computational complexity and guarantees the coding performance at low bit rate. Moreover, it enriches the RVC video tool library (VTL) by introducing the coding tools of AVS-P7, and also verifies the flexibility and re-configurability of RVC framework to meet the needs of different applications.

Reconfigurable video coding (RVC), Syntax parser, Decoder description, Hybrid decoder reconfiguration, Coding tool replacement

Короткий адрес: https://sciup.org/15012365

IDR: 15012365

Текст научной статьи Hybrid Decoder Reconfiguration of AVS-P7 and MPEG-4 /AVC in the Reconfigurable Video Coding Framework

Published Online August 2012 in MECS

Decoder Implementation, with those elements mentioned above, the final decoder implementation is platform-dependent and regarded as non-normative part of RVC framework. It is either generated by instantiating any implementation of proprietary VTLs which own identical I/O behavior of the FUs in standard VTLs, or obtained directly from the ADM by generating SW or HW implementations by means of appropriate synthesis tools [16, 17].

Decoder

Encoder

Inverse Scaling and Quantization

Inverse Integer Transform

(b)Block diagram of PIT coding

Fig.4 The comparison diagram between traditional and PIT coding

(a)Block diagram of traditional coding

-

(a) the BSD fragement of AVS bitstream

-

(b) a fragment from AVS bitstream schema

Fig.5 bitstream syntax description of MPEG-4 AVC

-

III. The decoder reconfiguration of MPEG-4 AVC

BASELINE PROFILE

-

A. A brief introduction of Audio Video Coding Standard of China ( AVS )

The AVS video coding standard has attracted more and more attentions both from the industries and research institutes. Recently it has been accepted as an option by ITU for IPTV applications. As MPEG standards, the AVS standard is composed of several parts, such as system, video, audio, conformance testing, and reference software etc. AVS Part 7, also called AVS-P7, is for low resolution, low bit rate video applications, such as streaming, wireless multimedia communication etc. AVS-P7 shares the similar coding framework with AVS Part 2. However, there are difference in complexity and coding efficiency for them.

AVS-P7 follows the methodology of intra prediction in MPEG-4/AVC [18], which exploits the statistically spatial dependencies between pixels. There are 9 prediction modes for luminance blocks and 3 modes for chrominance blocks. For lower-bitrate mobile video applications, smaller block size will lead to better coding efficiency. Compared with MPEG-4/AVC, AVS-P7 takes the enhanced best mode to increase matching effciency between the best mode and the most probable

Hybrid Decoder Reconfiguration of AVS-P7 and MPEG-4 /AVC

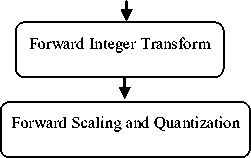

in the Reconfigurable Video Coding Framework mode, reduce the number of coded bits and guarantee the image quality. All intra predictions based on 4X4 block instead of 16 X 16 block. Moreover, the number of adjacent pixels used for prediction is decreased from 17 to 9, in order to reduce the computational complexity. The transform algorithm of AVS-P7 [7] is also different from MPEG-4 AVC. It introduces the pre-scaled integer transform (PIT) technique which combines scaling, quantization and inverse scaling together at the encoder, thus only inverse quantization is needed at the decoder to reduce complexity of decoder, as shown in the comparison diagram (Fig.4). AVS-P7 takes 64-level step-length quantizer to quantify transformed residual coefficients instead of 52 in MPEG-4 AVC. The scope extension of quantization step can flexibly and accurately compromise between bit rate and image quality. A simple and effective inter prediction is adopted in AVS-P7. It does not include bi-directional prediction and weighted prediction, and limits the number of the reference frame less than two. Therefore, AVS-7 is more easily to be implemented on mobile devices with low complexity and low requirement of storage capacity.

Fig.6 Architecture of Parser network in the reconfigured hybrid decoder

(a)

FUN_dcr

CoefDC_L

QP

ScalingList

FUN_IS_IQ_L

CoefAC_L

_ CoefACR L CoefDC_L

MbType

Algo_Merge_4×4_to_16×16

X

Algo_IS_Zigzag_4x4_DC Algo_DCR_Hadamard_LUMA_IHT1d_0 Algo_DC_Transpose4x4_0 Algo_DCR_Hadamard_LUMA_IHT1d_1 Algo_DCR_Hadamard_LUMA_Scaling Algo_DC_Transpose4x4_1 Algo_DCR_Hadamard_LUMA_Reordering

CoefDCR L MbType

QP

ScalingList

FUN_dcr

Y

L

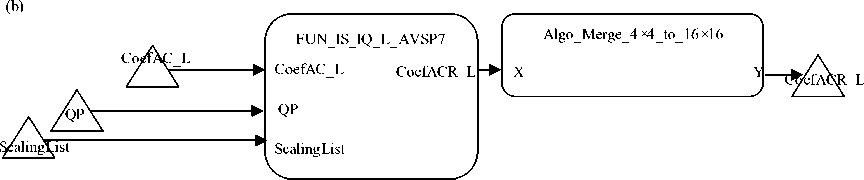

Fig.7 The implementation architecture of “Residuals Decoding” for the MPEG-4 AVC decoder (a) and the proposed hybrid decoder (b)

As mentioned above, the RVC framework provides a dynamic dataflow mechanism for constructing new video codecs by a collection of video coding tools from different video code standard, and AVS-P7 possesses several advantages in some certain situation. Although the Inverse Quantization (IQ) and Inverse Transform (IT) algorithms are completely different between AVS P7and MPEG-4/AVC, they both base on 4 X 4 blocks and have the same input and output token requirements. Thanks to the flexibility of the RVC framework, original MPEG-4 AVC baseline profile FUs (IT, IQ) can be easily replaced by the new FUs (IT, IQ) coming from AVS P7, the same principles to the functional block of Intra Prediction [ 19 ]. A new decoder solution is reconfigured in this paper. It is a hybrid decoder of AVS P7 and MPEG-4 AVC. The RVC framework provides a very interesting framework in which dynamic reconfigurations of decoders is straightforward. In the following, we describe the process of reconstructing the hybrid decoder within the RVC framework.

-

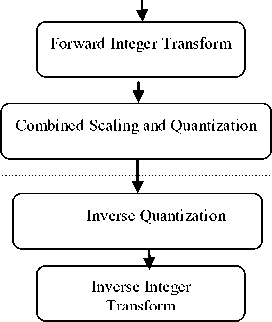

B. The generation of syntax parser

For the reconfiguration instantiation in this paper, encoder produces corresponding reconfigured bitstream and transmits it to decoder. Then decoder firstly parses the Decoder Description (DD). The Bitstream Syntax Description included in the DD explains how to fully describe the syntax structure of input bitstream and define corresponding Bitstream Syntax schema (BS schema). As shown in Bitstream Syntax Description fragment of MPEG-4 AVC (Fig. 5(a)) and BS schema fragment of MPEG-4 AVC codec (Fig. 5(b)). Before generating syntax parser from bitstream schema, one must guarantee that the schemas are correct, i.e. the schema reflects perfectly the structure of the encoded video data. So there must be a validation procedure, which guarantees that the bitstream is structured exactly as the schema describes it, then the generated parser can correctly parse the input bitstream [4]. Obviously, the Decoder Description guarantees the communication between encoder and decoder, and presented the flexibility and dynamic of reconfiguring decoder.

As stated above, the bitstream structure corresponding to the proposed hybrid decoder is described in BSDL, namely, a XML dialect. And FUs described in CAL can be also represented in a XML format: CALML. XSL Transformations are perfectly adapted to convert a bitstream schema written in BSDL into a parser in CALML [15]. As shown in the architecture of parser in the proposed hybrid decoder (Fig.6). “Algo_Synp” is generated by XSLT mentioned above. “Algo_IntraPred _Split” is employed to get the intra information and separate it into Y, U and V. “Algo_BlockExpand” gets and stuffs residual coefficients according “run, last, level” acquired from the “Algo_Synp”. And “Algo_ MMCO” is employed to update the “RefList”. “Algo_Parser_IPCM” derectly gets the pixel value of the current block.

-

(a) MPEG-4 AVC BP decoder : network IS_IQ_IT_L entities

Algo_IS_Zigzag_4 X 4_AC Mgnt_IQ_INTRA16 X 16 Algo_IQ_QSAndSLAndIDCTScaler_4 X 4 IT4 X 4

netwok IT4 X 4 entities Algo_IT4 X 4_1d_0 Algo_Transpose4 X 4_0

Algo_IT4 X 4_1d_1 Algo_Transpose4 X 4_1 Algo_ IT4 X 4_Addshift

-

(b) Reconfigured hybrid decoder: network IS_IQ_IT_L_AVSP7 entities

Algo_IS_Zigzag_4 X 4_coef_AVSP7

Algo_IQ _4 X 4_coef_AVSP7 //inverse quantization IT4 X 4_AVSP7 //inverse transform netwok IT4X4_AVSP7 entities

Algo_IT4 X 4_1d_AVSP7_0 Algo_Transpose4 X 4 _0

Algo_IT4 X 4_1d_AVSP7_1 Algo_Transpose4 X 4 _1

Algo_ IT4 X 4_Addshift_AVSP7

Fig.8 the structure of inverse scan, IQ and IT of AVC BP decoder and reconfigured hybrid decoder

-

C. Instantiation of reconfigured decoder

With those above-mentioned elements, the reconfigured decoder gets the attributes of each syntax element and the structure of current input bitstream through the Syntax Parser generated from BS schema, and gets required FUs and their connections for reconfiguring new decoder by parsing the FUs Network Description. Then Syntax Parser and those FUs are connected into a network called Abstract Decoder Model by parameter assignment and instantiation process, thus the decoder is configured successfully.

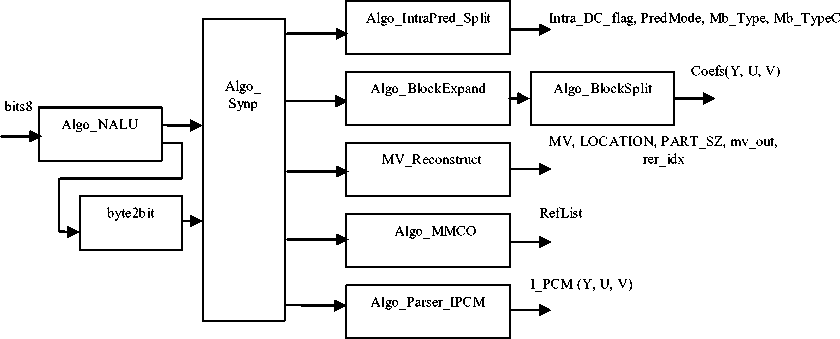

The structure of proposed hybrid decoder instantiation is similar to the MPEG-4 AVC Baseline Profile decoder, except that the IQ, IT block are replaced by those of AVS P7, and the reconfigured decoder discards a set of modules for intra 16X16 prediction mode (such as Inverse DC Hadamard transform, residual coefficient reordering). Figure 7 (a) shows the Y component imple-menttation architecture of “Residuals Decoding” within the MPEG-4 AVC decoder, and Fig.7(b) shows the corresponding functional modules within the proposed hybrid decoder. For U and V component, they are processed in the similar way as Y. These functional units are themselves hierarchical compositions of actor networks. The “FUN_dcr” module of MPEG-4 AVC BP decoder is used to decode the DC coefficients for intra 16×16 prediction mode. It includes “Algo_IS_Zigzag_ 4x4_DC”, “Algo_DCR_Hadamard_LUMA_IHT1d”, “Al go_DC_Transpose4x4”, “Algo_DCR_Hadamard_LUM A_Scaling” and “Algo_DCR_Hadamard_LUMA_Reord ering”. The “Algo_Merge_4x4_to_16×16” functional unit puts together 4x4 block in raster scan order to generate a 16×16 macroblock. Fig.8(a) illustrated the network of “FUN_IS_IQ_IT_L” within MPEG-4 AVC BP decoder. It completes the process of Inverse Scan, Inverse Quantization and Inverse Transform for residuals coefficients. The same function network of “FUN IS

IQ_IT_L_AVSP7” within the proposed hybrid decoder is illustrated in Fig.8(b), of which the “Algo_IT4 X 4_1d_0” and the “Algo_IT4 X 4_1d_1” reused the same actor “Algo_IT4 X 4_1d”, and the “Algo_Transpose4 X 4 _0” and “Algo_Transpose4 X 4 _0” reused the same actor “Algo_Transpose4 X 4”. The “Algo_ IT4 X 4_Addshift” of MPEG-4 AVC decoder can be replaced by “Algo_ IT4 X 4_Addshift_AVSP7”, which has the same input and output tokens as it. It is obvious that the reusability and exchangeability between different standard have been exploited in this instantiation, and the implementation architecture of reconfigured hybrid decoder is less complexity than the MPEG-4 AVC BP decoder.

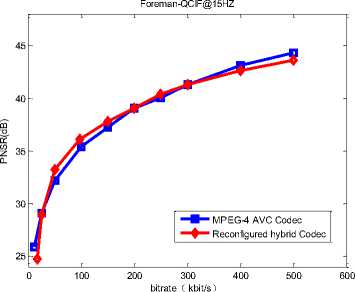

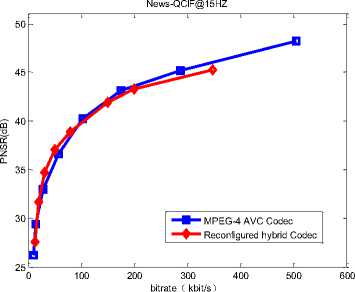

(a) Foreman

Fig.9 the R-D performance of AVC BP and the reconfigured hybrid decoder

(b) News

-

IV. Performance comparisons of reconfigurable

VIDEO CODEC

Besides the predominant reconfigurable characters of RVC standard, it is necessary to make further performance comparison between the MPEG-4 AVC BP codec and the reconfigured hybrid codec. Since AVS-P7 is mainly stipulated for mobile video standard, the number of reference frame is generally less than two instead of sixteen in MPEG-4 AVC BP. Experimental results are shown for two video sequences in QCIF format. Both Foreman and News sequences are 200 frames, and they have different motion complexity. The overall experiment environments are set as follows: the simulation was implemented on a PC with Pentium(R) 4 CPU 3.00 GHZ 2.99 GHZ and 512MB of RAM, GOP=IPPP.... , and frame rate=15 frame/second. A reconfigured bitstream is produced from MPEG-4 AVC reference software and provided as an input to the reconfigured decoder.

Fig.9 shows the Rate-Distortion (R-D) performance of MPEG-4 AVC BP and the reconfigured hybrid codec. Obviously, the two coding solutions can yield pretty nearly performance at low bitrates (<400 kbps), although the reconfigured codec gradually underperforms the MPEG-4 AVC BP as the bitrate increases.

A synthesis tool called Cal2C validates another implementation methodology of the MPEG-4 AVC BP dataflow program provided by “Open RVC-CAL Compiler (ORCC)”. It translates RVC-CAL actors to C files. The “Decoding_Y” component of MPEG-4 AVC dataflow program is composed of 34 actor instantiations in the flattened dataflow program. Each actor instantiation becomes a C file containing all its action /processing with its overall action scheduling/control. In the same way, the “Decoding_Y” component of the proposed hybrid decoder includes 26 actor instantiations. A comparison of “Decoding_Y” component between the MPEG-4 AVC BP and the reconfigured decoder is shown in Table1. It is evident that the processing resources required for the proposed hybrid decoder are less than the MPEG-4 AVC BP decoder by a reduction factor between 1 and 2.

As analyzed above, compared with the MPEG-4 AVC BP decoder, the reconfigured decoder realizes complexity reduction and guarantees performance in specific bitrate ranges. Therefore, for mobile video applications, such as mobile communication and mobile television, which have constrains of low bitrate and low computational complexity, the reconfigured decoder has significant advantages.

T able 1 A comparison of MPEG-4 AVC BP and reconfigured DECODER FOR “D ECODING Y” COMPONENT

|

Type of decoder |

CAL Number of files |

C actors Number of files |

|

MPEG-4 AVC BP decoder |

30 |

34 |

|

The proposed hybrid decoder |

20 |

26 |

|

reduction factor |

1.5 |

1.31 |

-

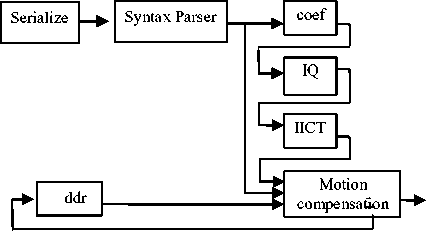

V. Implementation and simulation for the

PROPOSED DECODER CONFIGURATION

The reconfigured hybrid decoder in this paper consists of FUs written in RVC-CAL from the video tool library. Fig.10 illustrates the top-level view of the reconfigured decoder in this paper. The main functional blocks include the Serialize, Bitstream Syntax Parser, the reconstruction block, the inverse integer cosine transform(AVS P7), the inverse quantization (AVS P7), the frame buffer, the motion compensation module [20]. These functional units are hierarchical compositions of actor networks.

In the reconfiguration decoder, the input bitstream generated by MPEG-4 AVC reference software is serialized bit by bit through FU “Serialize” (“byte2bit” in Fig.6) before decoding process. The Syntax Parser network decodes the coming bitstream and produces context-control signal and a sequence of coefficients for each 4 X 4 block which will be used in the following networks. Then the following networks are to decode residuals (IQ and IICT) and implement prediction and motion compensation. The reconfigured hybrid decoder is compiled with RVC simulation tool (Open RVC-CAL Compiler) and the result of simulation shows that it can decode MPEG-4 AVC conformant bitstream correctly and elegantly.

Input Bitstream

Video

Fig.10 Top-level dataflow graph of the Hybrid decoder reconfiguration in RVC framework

-

VI. Conclusions

This paper describes the essential components of the MPEG Reconfigurable Video Coding framework based on the dataflow concept and has presented the new specification formalism called RVC-CAL. Compared with those traditional video coding standards, RVC framework provides a flexible mechanism to reconfigure video codec from the perspective of Functional Units, rather than the standard concept. The designer can devise proprietary codec system to meet different application requirements by avoiding unnecessary syntax elements and coding tools. This paper introduced the FUs of AVS P7 into Video Tool Library. Participation of AVS P7 in RVC enriches the significance of RVC framework and brings affirmative impulse for video coding field. In this paper, a hybrid decoder with FUs from MPEG-4/AVC and AVS P7 has been reconfigured. The instantiation shows great reconfiguration potential of decoder within RVC framework by replacing seemingly the existing FUs by new ones which have the same I/O tokens but different internal algorithm. This paper presents the decoder reconfiguration procedure in RVC framework, the definition of BS schema for reconfigured bitstream, and the generation of Syntax Parser. Experimental results show that compared with MPEG-4/AVC baseline profile, the reconfigured codec system reduces the computational complexity and guarantees the coding performance at low bit rate. Obviously, the decoder configuration architecture presented in this instantiation keeps the dataflow and modular mechanism of RVC. It can be further extended to support other new configurations, which will be our future investigation.

Acknowledgment

This work is supported in part by National Natural Science Foundation of China (No: 60702065), Special Pro-phase Project on National Basic Research Program of China (No: 2010CB334706) and Program for New Century Excellent Talents in University (NCET-11-0134).

Список литературы Hybrid Decoder Reconfiguration of AVS-P7 and MPEG-4 /AVC in the Reconfigurable Video Coding Framework

- Houjie Bi, Jian Wang et al. H.264/AVC and MPEG-4 Video Compression Standard for new generation Multimedia [M]. By Andrew Koenig Barbara Moo, 2009.

- HSIAO J M, TSAI C J. Analysis of an SoC architecture for MPEG reconfigurable video coding framework [C]. Proc. ISCAS 2007. New Orleans: IEEE Press:761-764, 2007.

- Mattavelli, M., I. Amer and M. Raulet. The reconfigurable video coding standard. IEEE Signal Processing Magazine, 27: 159-167, 2010.

- Lucarz, C., J. Piat, M. Mattavelli. Automatic synthesis of parsers and validation of bitstreams within the MPEG reconfigurable video coding framework. Journal of Signal Processing System, 63(2): 215-225, 2011.

- Ding, D., H. Qi, L. Yu, T. Huang, W. Gao. Reconfigurable video coding framework and decoder reconfiguration instantiation of AVS. Signal Processing: Image Commun-ication, 24: 287-299, 2009.

- Dandan, D., Lu Yu, C. Lucarz and M. Mattavelli. Video decoder reconfiguration and AVS extension in the new MPEG reconfigurable video coding framework. Proceedings of the IEEE Workshop on the Signal Processing Systems, Oct. 8-10, Washington, DC., pp: 164-169, 2008.

- AVS Video Expert Group, Information Technology – Advanced Audio Video Coding Standard Part 7: Mobility Video, in Audio Video Coding Standard Group of China (AVS), Doc. AVS – N1151, Dec.2004.

- Yu L., S. Chen and J. Wang, 2009. Overview of AVS-video coding standards. Signal Processing: Image Communication, 24: 247–262.

- ISO/IEC 23001-4, 2009. Information technology-MPEG systems technologies-Part 4: Codec configuration represen-tation.

- ISO/IEC 23001-4, 2010. Information technology-MPEG video technologies-Part 4: Video tool library.

- Amer I., C. Lucarz, G. Roquier, M. Mattavelli, M. Raulet, J.F. Nezan and O. Deforges, 2009. Reconfigurable video coding on multicore. IEEE Signal Processing Magazine, 26: 113-123.

- Eker J. and J. Janneck, 2003. CAL Language Report: Specification of the Cal Actor Language. University of Califonia, Berkeley CA.

- Gu R., J.W. Janneck, S.S. Bhattacharyya, M. Raulet, M. Wipliez and W. Plishker. Exploring the concurrency of an MPEG RVC decoder bases on dataflow program analysis. IEEE Trans. Cirruits and System for Video Technology. 19: 1646-1657, 2009.

- Open RVC-CAL Compiler [Online]. Available: http:// sourceforge.net/projects/orcc/.

- M. Bystrom, I. Richardson, S. Kannangara, M. de-Frutos-Lopez. Dynamic replacement of video coding elements. Signal Processing: Image Communication, 25(4):303-313, 2010

- Wipliez M., G. Roquier, M. Raulet, J.F. Nezan and O. Deforges, 2008. Code generation for the MPEG reconfigurable video coding framework: From CAL actions to C functions. Proceedings of IEEE International Conference on Multimedia and Expo, Hannover, pp: 1049-1052.

- Janneck J.W., I.D. Miller, D.B. Parlour, M. Mattavelli and C. Lucarz et al. 2008. Translating dataflow programs to efficient hardware: an MPEG-4 simple profile decoder case study. Design, Automation and Test in Europe (DATE), Munich.

- Wiegand T., G.J. Sullivan, G. Bjontegaard and A. Luthra, 2003. Overview of the H.264/AVC video coding standard. IEEE Trans. Circuits Systems Video Technolo., 13: 560-576.

- Yanfei Shen, Dongmin Zhang, Lejun Yu, Chao Huang and Shouxun Lin, A simplified intra prediction method, Doc. AVS – M1419, 2004.

- Shuvra S. Bhattacharyya, Johan Eker, Jörn W. Janneck, etc. Overview of the MPEG reconfigurable video coding framework. Journal of Signal Processing System, 63(2): 251–263, 2011.