Использование soft-процессоров на основе технологии FPGA для создания доверенной аппаратной платформы

Автор: Жуков Игорь Юрьевич, Ефанов Дмитрий Валерьевич, Леонов Василий Борисович, Григорьев Константин Гаярович

Журнал: Спецтехника и связь @st-s

Статья в выпуске: 1, 2014 года.

Бесплатный доступ

В статье обосновывается возможность применения soft-процессоров на основе современного поколения технологии FPGA для создания доверенной аппаратной платформы, сочетающей в себе свойства информационной безопасности и технологической независимости. Исследуется применимость закона Мура к технологии FPGA на примере семейств Spartan фирмы Xilinx и Cyclone фирмы Altera. Производится оценка производительности soft-процессора. Для реализации доверенного soft-процессора предлагается открытая архитектура OpenRISC.

Soft -процессор, доверенная аппаратная платформа

Короткий адрес: https://sciup.org/14967203

IDR: 14967203

Текст научной статьи Использование soft-процессоров на основе технологии FPGA для создания доверенной аппаратной платформы

The paper explains the possibility of soft-processors use based on the current generation of FPGA technology to build a trusted hardware platform that combines the properties of information security and technological independence. The applicability of Moore's Law to the FPGA technology is studied by the example of Xilinx`s Spartan families and Altera`s Cyclone. The assessment of soft-processor performance is made. For the trusted soft-processor implementation an open OpenRISC architecture is proposed. Keywords: FPGA, soft-processor, trusted hardware platform, Spartan, Xilinx, Cyclone, Altera, OpenRISC.

А ктуальная задача создания доверенной аппаратной платформы, сочетающей в себе свойства информационной безопасности и технологической независимости, заставляет постоянно анализировать современные процессорные технологии и архитектуры с точки зрения поиска экономически оправданных решений для получения необходимых свойств.

Стремительное развитие технологии программируемой вентильной матрицы (Field-Programmable Gate Array, FPGA) привело к тому, что сегодня стало возможным создание soft-процессоров, которые по своим характеристикам сопоставимы с серийно-выпускаемыми процессорами общего назначения.

При этом технология FPGA является очень привлекательной с точки зрения построения на ее основе доверенной аппаратной платформы, так как практически невозможно внедрить аппаратные закладки на уровне вентильной матрицы, и в тоже время становится возможным реализовать специфические функции защиты прямо в soft-процессоре.

Данная статья посвящена анализу современного состояния технологии FPGA в целях обоснования целесообразности создания доверенной аппаратной платформы на ее основе.

Метрики технологий ASIC и FPGA

Soft-процессор – это микропроцессорное ядро, реализованное на устройстве программируемой логики FPGA с использованием методов логического синтеза из стандартных логических элементов (ЛЭ), элементов АЛУ и блоков распределенной памяти.

На протяжении всей истории вычислительной техники шла борьба между универсальными и специализированными системами. FPGA-устройство по сравнению с заказной интегральной схемой высокой степени интеграции (Application Specific Integrated Circuit, ASIC) представляет собой максимально гибкое, практически полностью не специализированное логическое устройство. Ценою гибкости, однако, является менее экономный расход элементарных логических вентилей и снижение быстродействия, вызванного необходимостью использовать электронную коммутацию для соединения логиче- ских блоков, в то время как в ASIC-устройстве коммутация производится с помощью металлических проводников, задаваемых масками при изготовлении микросхемы.

Тем не менее, если обратиться к историческим аналогиям, то современный процессор общего назначения, созданный по технологии ASIC, является менее эффективным, чем цифровое устройство, созданное для выполнения определенной алгоритмической функции (то есть специализированный процессор). Несмотря на это снижение трудоемкости и времени, необходимых для создания устройства с заданной функцией, оправдывает применение процессоров общего назначения вместо специализированных. Аналогично использование soft-процессоров позволяет многократно ускорить и удешевить разработку процессора, в первую очередь, в отношении тех аспектов цифровой системы, которые могут быть реализованы только на аппаратном уровне. К таким аспектам можно отнести блоки информационной безопасности и специальных функций, реализация которых программным путем не обеспечивает необходимой производительности, либо функций, требующих максимальной детерминированности и точного соблюдения вероятностно-временных характеристик (ВВХ).

Для дальнейшего анализа введем некоторые количественные метрики, позволяющие сравнивать процессоры на основе технологий ASIC и FPGA.

Основными метриками ASIC-устройства, определяющими его производительность, являются количество элементарных логических вентилей (транзисторов) и максимальная внутренняя тактовая частота.

FPGA-устройства характеризуются количеством логических элементов и максимальной внутренней тактовой частотой. Современные FPGA-устройства также включают готовые элементы АЛУ и ячейки памяти.

Элементарный логический вентиль – это, как правило, единичный одно- или многозатворный полевой транзистор, в то время как ЛЭ может быть сопоставлен с логической микросхемой средней степени интеграции, и в среднем соответствует 20 – 30 элементарным вентилям. Статическая ячейка памяти состоит из 3 – 6 вентилей.

Для оценки эквивалентного количества логических элементов ASIC-устройств, исходя из заданных метрик FPGA-устройств, предлагается использовать следующее соотношение:

N экв ≈ 25 N лэ + 4 N бит , (1)

где N лэ – количество логических элементов FPGA, N бит – количество бит встроенной памяти FPGA.

Максимальная тактовая частота процессора для FPGA-устройства примерно в 3 – 5 раз ниже, чем при ASIC-подходе, так как в случае FPGA сигнал должен проходить через несколько статически управляемых контактов с достаточно высоким сопротивлением, в то время как в ASIC для соединения узлов схем используется металлический проводник, обеспечивающий большую скорость прохождения импульса.

Закон Мура в применении к технологии FPGA

Закон Мура в оригинальной формулировке утверждает, что максимальное количество ЛЭ, которое может быть размещено на кристалле интегральной микросхемы, удваивается каждые 24 месяца. В общем случае можно говорить об экспоненциальном росте количества элементов на кристалле вплоть до достижения размерных пределов существующей технологии. В настоящее время 14-нм технология FinFET представляет собой предел планарных кремниевых технологий и при этом является переходной к 3-мерным технологиям. В период до 2025 г. можно ожидать внедрения принципиально новых технологий,

Таблица 1. Цена и количество ЛЭ по поколениям FPGA общего назначения

|

Поколение |

Год |

Цена ЛЭ, долл. × 10-3 |

ЛЭ, тыс. |

Технология, нм |

|

Spartan1 |

1998 |

22,68 |

1,86 |

350 |

|

Spartan2 |

2000 |

4,96 |

5,29 |

180 |

|

Spartan2E |

2001 |

5,67 |

6,91 |

150 |

|

Cyclone1 |

2002 |

2,93 |

20,06 |

130 |

|

Spartan3 |

2003 |

1,19 |

62,21 |

90 |

|

Cyclone2 |

2004 |

2,28 |

18,75 |

90 |

|

Cyclone3 |

2007 |

1,6 |

24,62 |

65 |

|

Cyclone4 |

2009 |

1,38 |

28,85 |

60 |

|

Spartan6_LX |

2009 |

1,08 |

147,44 |

45 |

|

Cyclone5 |

2013 |

0,7 |

301 |

28 |

таких как логические схемы на основе графена, обладающие внутренней предрасположенностью к динамической реконфигурации [1], и использования межсоединений из графена, позволяющих кратно увеличить скорость передачи сигналов между ЛЭ и снизить потребляемую мощность на несколько порядков [2]. Рассмотрим применимость закона Мура к программируемой логике FPGA на примере семейств Spartan фирмы Xilinx и Cyclone фирмы Altera. Данные технологии созданы в целях достижения оптимального соотношения цена/характеристики и предназначены как для специализированных устройств, так и для устройств общего назначения, включая бортовые, встроенные и планшетные компьютеры [3 – 8].

За период с 1998 г., когда была выпущена первая серия устройств Spartan, до 2013 г., когда появилась серия Cyclone V, сменилось 10 поколений, при этом технологические нормы улучшились от 350 нм до 28 нм, а степень интеграции возросла от 2 тысяч до 300 тысяч ЛЭ. Стоимость одного ЛЭ снизилась за это время с 0,022 до 0,0007 долларов США (по курсу и в ценах 2013 г.).

Были проанализированы количество и стоимость одного ЛЭ для изделий, обладающих минимальной стоимостью ЛЭ в каждом поколении FPGA, по 1,6 тысячи товарных позиций (958 по Аltera, 594 по Xylinx). Результаты анализа представлены в табл. 1 .

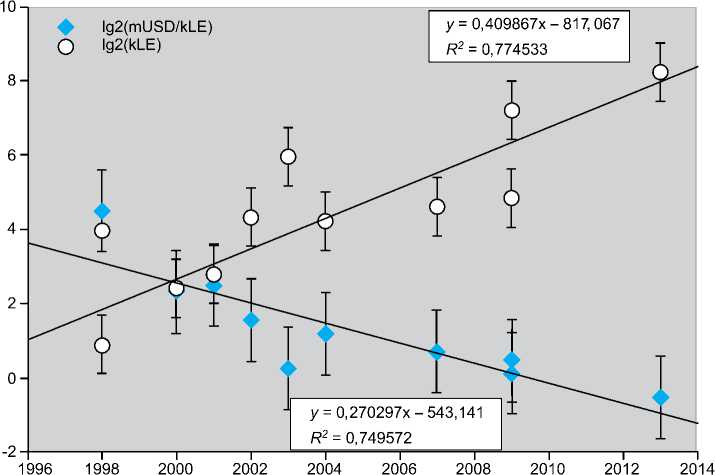

Исследуем линейную регрессию данных в логарифмическом представлении по основанию 2 (log2), коэффициент линейной регрессии при этом дает величину, обратную времени изменения зависимой переменной в 2 раза. В результате видно, что закон Мура выполняется со значительной точностью (рис. 1). Время удвоения числа ЛЭ на кристалле составляет 2,5 года ×(1/0,41), а время снижения цены в 2 раза – примерно 3 года.

Коэффициент корреляции для количества ЛЭ составил R2 = 0,77, для цены ЛЭ составил R2 = 0,75. Качество регрессионной модели оценивалось с помощью критерия Фишера. Критический уровень значимости при проверке статистических гипотез принят равным 0,05, число степеней свободы для n = 10 составляет ν = 8, что соответствует величине F крит = 5,3. Значение F ф акт = 27,5 для регрессии по количеству ЛЭ, по цене ЛЭ – F ф акт = 23,9, в обоих случаях позволяет сделать вывод о статистической значимости предложенной модели.

Рис. 1. Количество и цена ЛЭ в FPGA общего назначения (логарифмический масштаб)

FPGA-устройства опережают по технологии серийные ASIC-процессоры общего назначения на 1 – 2 поколения

Вследствие более регулярной и менее сложной структуры FPGA лидируют по темпу внедрения наиболее передовых технологий изготовления интегральных микросхем. В частности, серия Cyclone V фирмы Altera, предназначенная для широкого применения и поступившая в продажу во II квартале 2013 г., построена по 28-нм технологии, в отличие от любых серийно выпускаемых процессоров. Одновременно Altera приступила к разработке серии Stratix-10 по 14-нм технологии FinFET. Образцы серийных устройств на основе этой технологии ожидаются в 2014 г. Задержка от внедрения более продвинутой технологии в серии Stratix до появления аналогичных устройств серии Cyclone, которые попадают в ценовой диапазон широкого применения, составляла в прошлом 2 – 3 года. Поэтому можно ожидать появления 14-нм устройств серии Cyclone в 2017 г. Используя полученные выше регрессионные зависимости, цена на ЛЭ должна составить 1,4 копеек, а степень интеграции – 600 тысяч ЛЭ и 28 Мбит памяти, при цене 8500 рублей. Эти цифры хорошо согласуются с увеличением в 2 – 3 раза параметров интеграции при каждом переходе на новую размерную технологию в семей- стве Суclone и открывают возможность широкого использования soft-процессоров.

Экономические аспекты внедрения soft-процессоров

Основная экономическая закономерность заключается в том, что заказные микросхемы ASIC являются значительно более дорогими в подготовке к производству при более низкой стоимости крупносерийного изделия, в то время как программируемая логика FPGA значительно удешевляет и ускоряет процесс разработки, но при большей стоимости готового изделия.

Разработка цифровой микросхемы не является самоцелью, но преследует достижение определенных экономических целей. Рассмотрим три вида издержек: собственно себестоимость производства готового изделия ( C изд ), издержки разработки ( С р ) и убытки от недостаточного быстрого выхода готового изделия на рынок.

Себестоимость изделия C изд – это цена изготовления одного экземпляра устройства. Она состоит из двух частей: стоимости подготовки к производству ( С подг ) и себестоимости изготовления одного устройства ( С ед ). Издержки подготовки являются однократными на каждое новое изделие.

Себестоимость устройства состоит из цены материалов, изготовления и сборки. Издержки подготовки распределяются на все произведенные устройства и уменьшаются в себестоимости каждого устройства по мере увеличения объема партии. Таким образом, себестоимость изделия в партии составляет:

C изд = С ед +( С подг /N изд )

Цена разработки С р для ASIC-устройства значительно выше с учетом необходимости тщательного логического и физического моделирования, понимания технологического процесса и получения производственной документации. В силу значительной стоимости изготовления экспериментальных образцов (15 – 45 млн рублей) цена ошибки при разработке ASIC очень велика.

Для FPGA-устройства цена разработки значительно ниже, прежде всего, в результате возможности использовать метод последовательных приближений, так как при изменении требований и выявлении дефектов их исправление сводится к компиляции и перезагрузке конфигурационной памяти системы.

По мере снижения цены FPGA-устройства, количество единиц продукта, делающее экономически оправданным выбор технологии ASIC, увеличивается и в настоящее время для процессоров и микроконтроллеров составляет не менее 10 тыс. штук.

Сравнение возможностей soft-процессора с процессорами общего назначения

Soft-процессор в отличие от процессоров общего назначения, построенных на основе технологии ASIC, позволяет:

-

♦ совершенствовать и даже полностью менять архитектуру процессора, а также устранять дефекты в процессе эксплуатации;

-

♦ реализовывать аппаратные решения с максимальной отказоустойчивостью и информационной безопасностью;

-

♦ реализовывать функции, программная реализация которых неэффективна, например, новые алгоритмы кодирования/декодирования данных;

-

♦ реализовывать функции, требующие жесткой детерминированности и заданных ВВХ, например, протоколов аппаратных интерфейсов;

-

♦ значительно уменьшать число внешних компонентов и избавляться от специализированных интерфейсных микросхем, то есть сокращать номенклатуру комплектующих;

-

♦ унифицировать аппаратную часть цифровой системы управления для различных изделий;

-

♦ обеспечивать высокий уровень технологической независимости создаваемых изделий.

В отношении оценки производительности soft-процессоров будем исходить из формулы (1). Оценка числа ключей, которые могут быть реализованы на FPGA c N лэ = 300 тыс. и N бит = 14 Мбит, составит N экв ≈ 49,5 млн.

В табл. 2 приведены характеристики известных процессоров общего назначения [9], параметры которых приблизительно соответствуют достижимым для soft-процессора на существующем и планируемом в ближайшее время уровне развития технологии FPGA.

Для реализации soft-процессора целесообразно использовать архитектуру RISC, которая позволяет достигнуть

Таблица 2. Количество ключей в известных процессорах общего назначения

|

Процессор |

Год выпуска |

Ключей, млн |

Тактовая частота |

Технология |

|

ARM Cortex A9 |

2007 |

26 |

||

|

Intel Pentium Mobile |

2003 |

55 |

1,7 |

90 |

|

Intel Atom |

2008 |

47 |

1,8 |

45 |

|

Intel Pentium 4 |

2000 |

42 |

1,5 |

180 |

|

Nvidia NV25 |

2002 |

63 |

150 |

|

|

UltraSPARC T1 |

2005 |

279 |

1 |

90 |

тех же параметров, что и процессоры с архитектурой CISC, но при меньших ресурсах. Из известных на сегодняшний день RISC-архитектур наиболее перспективной, по мнению авторов, является открытая архитектура OpenRISC.

Заключение

Динамика развития технологии FPGA и характеристики современных семейств FPGA-устройств позволяют сделать вывод о том, что сегодня soft-процессор представляется наиболее перспективной аппаратной платформой для следующего поколения информационных технологий. Особое значение данная тенденция приобре-

Список литературы Использование soft-процессоров на основе технологии FPGA для создания доверенной аппаратной платформы

- Graphene: The Ultimate Switch./Chun-Yung Sung, Ji Ung Lee -IEEE Spectrum; 2012.

- Demonstration of a Subthreshold FPGA Using Monolithically Integrated Graphene Interconnects/Kyeong-Jae Lee; Hyesung Park; Jing Kong; Chandrakasan, A.P./Electron Devices. -IEEE Transactions on. -Volume 60. -Issue 1.

- Cyclone Device Handbook. -Altera, 2008.

- Cyclone II Device Handbook. -Altera, 2008.

- Cyclone III Device Handbook. -Altera, 2012.

- Cyclone IV Device Handbook. -Altera, 2013.

- Cyclone V Device Handbook. -Altera, 2013.

- Cyclone V Device Datasheet. -Altera, 2013.

- Transistors to Transformations. -Intel, 2012.