Основная типизация мультиразрядного микропроцессора в структуре современных микропроцессоров

Бесплатный доступ

Рассматриваются мультиразрядные микропроцессы - особый класс значительно улучшенных микропроцессоров, в которые встроены механизмы, отвечающие за повышение надежности работы программного обеспечения, запускаемого на данном микропроцессоре, - табличная структура регистров и система резервного копирования. Рассматривается месторасположение указанного микропроцессора и основные характеристики модельного ряда: система команд (самые популярные типы CISC и RISK), тип организации стэка (Неймана - Лебедева, гарвардская архитектура), тип распределения команд (статический или динамический). В качестве примера взят доработанный вариант микропроцессора AMD64, в котором применена табличная модель организации регистров и использовано резервное копирование.

Мультиразрядный микропроцессор, система команд микропроцессора

Короткий адрес: https://sciup.org/148326849

IDR: 148326849 | УДК: 004 | DOI: 10.18137/RNU.V9187.23.02.P.203

Basic typing of multibit microprocessor in the structure of modern microprocessors

The article considers a special class of microprocessors - multi-bit microprocessors, which are significantly improved microprocessors. They have built-in mechanisms to improve the reliability of software running on a given microprocessor. The main ones are a tabular register structure, and a backup system. The location of the specified microprocessor and the main characteristics of the lineup are considered, which include the command system (the most popular CISC and RISK types), the type of stack organization (Neumann - Lebedev, Harvard architecture), the type of command distribution (static or dynamic). An example for an analysis will be a modified version of the AMD64 microprocessor, in which a tabular model of register organization is applied and backup is used.

Текст научной статьи Основная типизация мультиразрядного микропроцессора в структуре современных микропроцессоров

В последнее время информационные технологии продолжают активно развиваться, а до этого пережили настоящий бум. IT-индустрия сегодня представлена крупными транснациональными корпорациями, такими как Microsoft, Apple, Google, Yandex и др., причем практически все крупные сектора этих компаний имеются в зарубежных странах (Китай, США, Тайвань и др.). В нашей стране присутствуют свои гиганты по производству микропроцессоров, в частности это компании МЦСТ, «Байкал электроникс» и др.

При разработке мультиразрядных микропроцессоров [1], обладающих специфическими особенностями, к которым относится работа в экстремальных условиях окружа-

Приходько Дмитрий Игоревич магистр, инженер вычислительных и электронно-вычислительных машин, «Федеральный научный центр Научно-исследовательский институт системных исследований РАН». Научноисследовательский институт системных исследований РАН, Москва. Сфера научных интересов: информационные системы, вычислительные системы, операционные системы, эксплуатация вычислительных систем. Автор более 30 опубликованных научных работ. SPIN-код: 90632855, AuthorID: 968616.

ющей среды, возникает ряд вопросов: к какой категории относится данный микропроцессор, какой тип стэка является рекомендуемым, какую систему команд можно выбрать?

Цель статьи – определить основные особенности мультиразрядного микропроцессора и класс принадлежности по типам приложений.

Опишем существующие типы приложений, которые используются в разработках в настоящее время.

Методология

В статье рассмотрена классификация микропроцессоров по следующим характеристикам: тип набора команд, тип организации стэка, тип организации распределения команд, а также вопрос о проектировании мультиразрядного микропроцессора на примере существующих решений – архитектур AMD64 [2] и «Эльбрус» [3].

Из существующих наборов команд для микропроцессоров и микроконтроллеров наибольшей популярностью пользуются следующие наборы:

-

• CISC . Полный набор команд. Первоначально использовался в микропроцессорах. Из производителей современные модели выпускают компании AMD, Intel. Постепенно будет уходить в прошлое, так как практика компиляторов показала, что столько инструкций уже не требуется, и прирост производительности заметно снижен по сравнению с RISK;

-

• RISC . Сокращенный набор команд. Первоначально разрабатывался компанией ARM, используется также в микропроцессорах «Эльбрус». Потенциал прироста этой архитектуры пока не исчерпан, в отличие от CISC.

При этом микропроцессоры по типу организации стэка, то есть по способу передачи аргументов и вызову функций в микропроцессоре, можно классифицировать следующим образом:

-

- микропроцесссоры с архитектурой организации стэка Неймана – Лебедева . Стэк организован таким образом, что аргументы и адрес функции физически расположены в одном месте. Для доступа есть информация только по указателю на вершину стэка;

-

- микропроцесссоры c гарвардской архитектурой . Стэк и аргументы функций физически разделены. Для доступа к аргументам их согласования с вызываемой функцией используются специальные дескрипторы доступа. Ярким представителем являются микропроцессоры, производимые компанией МЦСТ.

По способам распределения команд микропроцессоры классифицируются следующим образом:

-

- статические. Распределение команд закладывается полностью компилятором, процессор только выполняет их в указанном расположении;

Основная типизация мультиразрядного микропроцессора ...

-

- динамические. Распределение команд выполняется микропроцессором, процессор только выполняет их в указанном расположении.

Рассмотрим недостатки по показателям и выбор модели микропроцессора с учетом описанных недочетов.

Результаты

Описанные выше характеристики необходимо дополнить фактом, что мультираз-рядные микропроцессоры предназначены для эксплуатации в экстремальных условиях окружающей среды, к которым относят и космическое пространство. В связи с этим требования к их разработке существенно выше, чем к обычным микропроцессорам [4; 5].

Рассмотрим характеристики каждой из категорий мультиразрядных микропроцессоров.

С точки зрения набора команд – CISC и RISC – практика использования компиляторов показала, что оба решения имеют свои достоинства и недостатки (Таблица).

Таблица

Обзор основных достоинств и недостатков CISC и RISC.

|

Система команд |

Достоинства |

Недостатки |

|

CISC |

Простые инструкции для написания программ на низком уровне |

Различный размер инструкций программ |

|

Более простое построение компилятора на языке высокого уровня |

Избыточно большой набор команд, который зачастую не используется компилятором |

|

|

RISC |

Уменьшенный набор команд, который позволяет оптимизировать работу программ |

Программы сложнее отлаживать, так как число инструкций больше, чем в CISC |

|

Одинаковый размер инструкций улучшает производительность программ |

Требует более продвинутого компилятора |

Таким образом, лидером по набору команд является модель RISC, которая является более простой для микропроцессора, хотя и требует построения качественного компилятора.

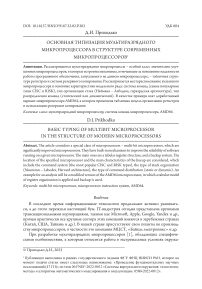

В микропроцессоре архитектуры организации стэка Неймана – Лебедева и Гарварда представлены на Рисунок 1 .

Можно отметить, что главная проблема архитектуры Гарварда при воздействии ионизирующего излучения – угроза рассогласования адресов памяти команд с аргументами. Поэтому для защиты от воздействия ионизирующего излучения понадобится организовать не просто дублирование стэка памяти и команд, но и дескрипторы обращения.

Для архитектуры Неймана – Лебедева этой проблемы не существует, так как аргументы и команды находятся физически в одном месте, и поэтому организовать защиту от неустранимого отказа достаточно путем простого дублирования.

Поэтому для мультиразрядных микропроцессоров система организации стэка Неймана – Лебедева является более предпочтительной, нежели гарвардская.

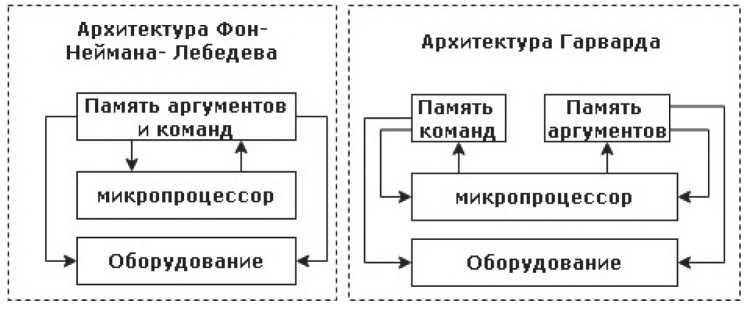

Сравнение по системе распределения команд приведено на Рисунок 2 .

Как видно из рисунка, распределение команд для архитектуры «Эльбрус» выполняется компилятором, а для архитектуры Intel x86 – встроенным в микропроцессор конвейером команд. В связи с этим можно сделать следующие выводы.

-

1. Архитектура «Эльбрус» является потенциально выигрышной по сравнению с Intel x86, так как потенциал роста первой не ограничен и зависит только от компилятора и числа ядер в микропроцессоре.

-

2. При повреждении микропроцессора архитектуры «Эльбрус» возникает вопрос перестройки исполнения VLIW-пакета при подаче команд. Для моделей Intel основная проблема – надежность механизма распределения команд в микропроцессоре.

Рисунок 1. Архитектуры организации стэка микропроцессоров Источник: выполнено автором.

Рисунок 2. Сравнение распределения команд архитектуры «Эльбрус» и Intel x86 Источник: Краткое описание архитектуры Эльбрус (URL: .

Основная типизация мультиразрядного микропроцессора ...

Таким образом, с точки зрения надежности архитектура Intel x86 проще и, следовательно, при дополнении табличной структуры регистра остается лишь обеспечить надежность системы распределения команд, то есть данная архитектура предпочтительнее.

Основные характеристики мультиразрядных микропроцессоров:

-

• используется логическая модель организации регистров, подразумевающая, что физическая последовательность записи результата может не совпадать с логической;

-

• используются различные механизмы резервного копирования значений в незадей-ствованный набор триггеров;

-

• используются особые структуры организации регистров работы с числами с плавающей точкой.

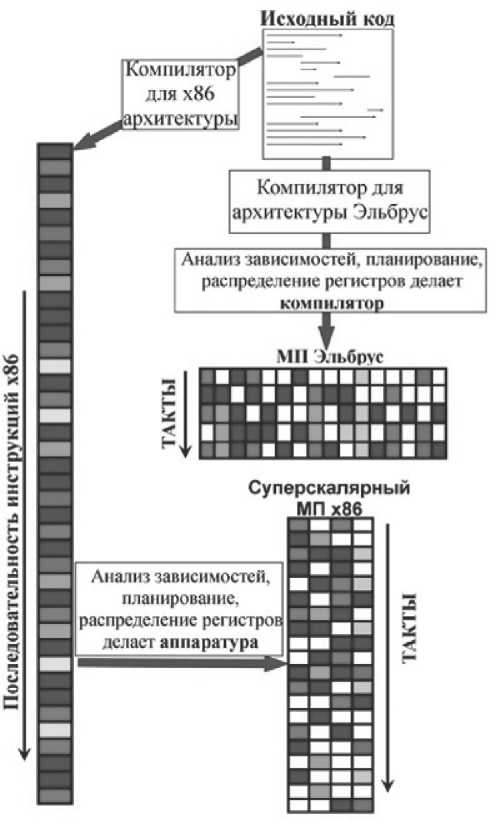

Приведем пример табличной структуры регистра микропроцессора, которая является общей чертой для мультиразрядных микропроцессоров (Рисунок 3).

Рисунок 3. Табличная структура регистров мультиразрядного микропроцессора Источник: выполнено автором.

Из Рисунка 3 следует, что мультиразрядные микропроцессоры относятся к классу более устойчивых микропроцессоров, предназначенных для запуска программного обеспечения в экстремальных условиях окружающей среды.

Обсуждение

Таким образом, из всего вышесказанного можно сделать вывод, что мультиразряд-ный микропроцессор на архитектуре Intel x86 с учетом внутренних построений в общем случае является более надежным, так как требует меньших доработок для повышения надежности. Поэтому построение мультиразрядного микропроцессора лучше выбирать на основе архитектуры AMD64. Однако с учетом последних событий достоинства микропроцессора Intel разбиваются о проблемы, связанные с тем, что архитектура Intel не является отечественной, и рост производительности архитектуры CISC по сравнению с RISC можно считать остановленным.

Поэтому проектирование мультиразрядных микропроцессоров на архитектуре «Эльбрус» возможно, но потребует следующих дополнительных доработок:

-

• внедрение системы пересборки пакетов, что позволит исключить поврежденные ядра из работы максимально безболезненно;

-

• внедрение механизма дополнительного распределения команд, что необходимо для оптимизации пересобранного пакета под оставшиеся ядра;

-

• создание системы резервирования адресации и дескрипторов для работы стэка, что необходимо для гарантированной сохранности выполненных команд в микропроцессоре;

-

• дополнение режимами работы, которые требуют меньших ресурсов микропроцессора, по аналогии с Intel.

В свою очередь, использование указанных механизмов для мультиразрядного микропроцессора на архитектуре «Эльбрус» и Intel x86 означает существенное удорожание разработки программного обеспечения [6–8] и увеличение потребления электроэнергии, что ограничивает область применения данного типа микропроцессоров.

Заключение

Показано, что мультиразрядные микропроцессоры относятся к классу микропроцессоров, предназначенных для работы в космических условиях.

Оптимальная для разработки и проектирования структура рассмотренных характеристик следующая: RISK построенная система команд, динамический конвейер команд, организация стэка по технологии Неймана – Лебедева.

Поэтому для реализации лучшим образом подходит архитектура Intel x86, однако при внедрении специальных доработок в архитектуру «Эльбрус» она может быть применена для построения мультиразрядного микропроцессора.

Список литературы Основная типизация мультиразрядного микропроцессора в структуре современных микропроцессоров

- Приходько Д.И., Мокряков А.В., Горшков В.В. Модель мультиразрядной компьютерной архитектуры, предназначенной для космических условий и ее ключевые особенности // Авиакосмическое приборостроение. 2022. № 11. С. 39-48.

- Приходько Д.И. Разработка и оптимизация методов эксплуатации информационных систем как этапа их жизненного цикла с учетом воздействия агрессивной внешней среды: магистерская дис.: 01.04.02. РГУ им. А.Н. Косыгина. М., 202. 204 с.

- Приходько Д.И. Краткий анализ архитектуры Эльбрус для задач ГО // Гражданская оборона на страже мира и безопасности: Материалы III Международной научно-практической конференции, посвященной Всемирному дню гражданской обороны. В 3 ч. Москва, 01 марта 2019 г. Ч. 1. М.: Академия ГПС МЧС России, 2019. С. 191-194.

- Горшков, В.В., Приходько Д.И., Мокряков А.В. Устройство для управления конфигурацией вычислительной системы. (2021). Патент на полезную модель 207176 U1, 15.10.2021. Заявка № 2021118609 от 25.06.2021.

- Горшков, В.В., Приходько Д.И., Мокряков А.В. Устройство для управления разрядностью вычислений. (2022). Патент на полезную модель 209758 U1, 22.03.2022. Заявка № 2021118607 от 25.06.2021.

- Карцан И.Н., Ефремова С.В. Мультиверсионная модель программного обеспечения систем управления космическим аппаратом с ранжированием принятия решения // Сибирский аэрокосмический журнал. 2021. Т. 22, № 1. С. 32-46.

- Поздняков Д.А. Компонентная программная архитектура мультиверсионных систем обработки информации и управления // Современные наукоемкие технологии. 2006. № 4. С. 62-64. URL: https://top-technologies.ru/ru/article/view?id=22646 (дата обращения: 16.10.2022).

- Приходько Д.И., Мокряков А.В., Горшков В.В. Обзор базовых механизмов мультиразрядных операционных систем, предназначенных для эксплуатации в космических условиях // Авиакосмическое приборостроение. 2022. № 12. С. 39-48.