Особенности разработки автоматизированной системы проектирования интегральных цифро-аналоговых преобразователей

Автор: Ионов Л.П.

Журнал: Инфокоммуникационные технологии @ikt-psuti

Рубрика: Технологии компьютерных систем и сетей

Статья в выпуске: 2 т.7, 2009 года.

Бесплатный доступ

Рассмотрена задача проектирования интегральных цифро-аналоговых преобразователей. Предложены методы автоматизации проектирования, основанные на использовании схемотехнического моделирования, параметрической оптимизации и искусственного интеллекта. На базе предложенных методов и алгоритмов разработана автоматизированная система проектирования DAC Compiler. Предусмотрена интеграция данной системы в систему Cadence (R) Virtuoso Design Environment [1-2].

Короткий адрес: https://sciup.org/140191317

IDR: 140191317 | УДК: 681.586.37

Automatic synthesis system development for integrated digital/analog converters

Integrated Digital/Analog Converters (DAC) design problem is considered. Design automation methods based on parametric optimization, circuit simulation and expert systems is proposed. Automatic design system DAC Compiler is designed using proposed methods. There is a capability to integrate considered system to Cadence(R) Virtuoso Design Environment System.

Текст научной статьи Особенности разработки автоматизированной системы проектирования интегральных цифро-аналоговых преобразователей

В большинстве современных интегральных схем типа «система на кристалле», использующихся в промышленности, наряду с цифровыми блоками, присутствуют аналого-цифровые и цифро-аналоговые преобразователи (АЦП и ЦАП). Данные блоки обычно занимают сравнительно малую часть площади кристалла, при этом их разработка требует непропорционально большего времени и усилий разработчиков. В цифровых интегральных схемах (ИС) широко используется синтез схемы на основе описания на языке высокого уровня, а также автоматическое размещение и трассировка топологии. По примеру цифровых ИС в работах [3-4] было предложено использовать синтез электрической схемы и для аналоговых блоков. Такой подход применим для широкого класса наиболее часто используемых аналоговых блоков. В то же время универсальность описываемого метода влечет за собой существенный недостаток: он не учитывает специфику конкретного типа схем. Второй, более современный подход [5-6], состоит в разработке ряда инструментов синтеза, каждый из которых оптимизирован для конкретного типа устройств (АЦП, ЦАП, операционные усилители и т.д.).

Независимо от того, разрабатывается система для универсального использования или для специфического класса схем, есть три основных подхода к ее построению [7]:

-

- системы на основе продукционных баз знаний;

-

- системы на основе использования мягких вычислений для решения задач параметрической оптимизации и топологического синтеза;

-

- комбинация перечисленных подходов.

Рассматривается специализированная система автоматизированного проектирования интегральных ЦАП, основанная на применении комбинационных методов построения.

Алгоритм автоматизированного проектирования интегральных ЦАП

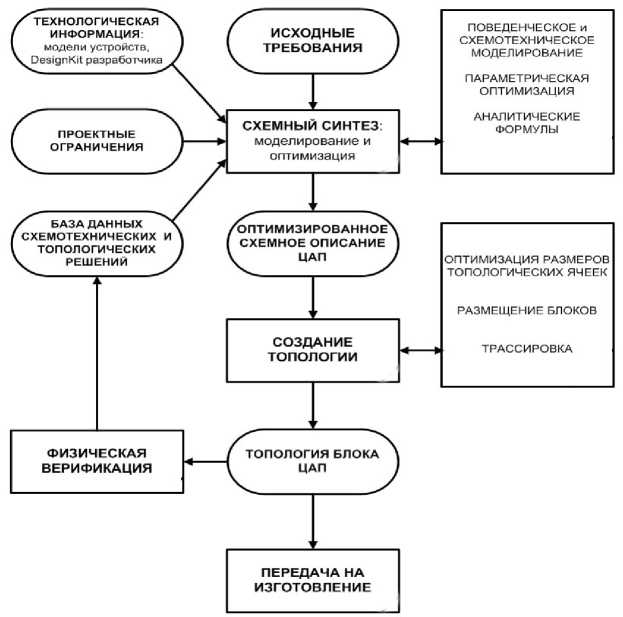

На рис. 1 представлена структурная схема процесса проектирования блока ЦАП в среде разрабатываемой системы.

Исходными данными для проектирования являются: проектные ограничения, технологическая информация, разрядность ЦАП, напряжение питания, скорость преобразования, линейность и т.д. Начальное решение, на базе которого будет выполняться оптимизация, выбирается программой автоматически из библиотеки схемотехнических решений. Особенностью базы является то, что для каждой схемы, наряду с формальным описанием элементов и соединений между ними, может быть также сохранена информация, основанная на знаниях разработчика: согласование элементов (например, для дифференциальных пар и согласованных источников тока), максимальный ток через элемент и т.п. Данная библиотека является открытой и может дополняться и редактироваться.

Для оценки характеристик получаемой схемы используются следующие три вида анализа.

-

1. Схемотехническое моделирование на уровне транзисторов

-

2. Поведенческое моделирование

-

3. Аналитические формулы и выражения

Независимо от вида анализа в системе могут использоваться наиболее распространенные системы моделирования: HSPICE и Spectre. Оценка характеристик ЦАП требует выполнения трудоемких статистических расчетов (анализ Монте-Карло). В ходе работы был разработан алгоритм вычисления характеристик ЦАП на основе статистических разбросов значений переменных оптимизации без необходимости выполнения анализа Монте-Карло.

Проектная параметрическая оптимизация не является чем-то новым при разработке аналоговых схем [8]. Но оптимизация схем ЦАП представляет собой особую задачу. Особенность состоит в том, что часть ограничений носит

Рис. 1. Структурная схема процесса проектирования блока ЦАП в среде разрабатываемой системы

целочисленный характер. Оптимизация выполняется методами целочисленного нелинейного программирования. Необходимо отметить, что большинство данных методов не гарантируют нахождение глобального экстремума целевой функции. Во многих случаях достаточно запустить оптимизацию при различных начальных условиях и выбрать из полученных решений минимальное (или максимальное). Это существенно повышает вероятность нахождения глобального оптимума, но, соответственно, и общее время оптимизации. Для большей эффективности нахождения глобального экстремума целевой функции в системе предусмотрена возможность использования метода «моделирования отжига». Этот метод очень эффективен при решении проблем с целыми и вещественными переменными. Его главный недостаток – очень низкая скорость. В ходе работы пользователь имеет возможность выбрать используемый метод.

На этапе проектирования топологии первоначально формируется требуемая геометрия элементарных ячеек (источников тока, источников смещения, переключателей и т.д.). Размещение элементарных ячеек и блоков, а также их трассировка осуществляется с использованием существующих методов, адаптированных к построению топологии ЦАП [9].

Физическая верификация используется для проверки соответствия топологии конструкторско-технологическим ограничениям и исходной электрической схеме. На данном этапе производится моделирование блока ЦАП с учетом экстрагированных паразитных элементов.

Обеспечена интеграция рассматриваемой специализированной системы в систему автоматизации проектирования электронных устройств Virtuoso Design Environment (Cadence). При интеграции и при реализации алгоритмов размещения и трассировки топологии использовался встроенный в систему Virtuoso язык SKILL.

Данная система была апробирована при разработке 10-разрядного цифроаналогового преобразователя по кремний-германиевой технологии БиКМОП с проектными нормами 0,25 мкм фирмы IHP (Германия). Результаты измерений опытных образцов показали соответствие основных измеренных параметров заданным требованиям.

Заключение

В работе представлено описание специализированной системы автоматизированного проектирования интегральных ЦАП. В процессе данной работы была создана база данных схемотехнических и топологических решений; разработана специализированная целевая функция для проведения оптимиза- ции, учитывающая специфику функционирования блоков ЦАП; разработана среда для проведения моделирования и оценки характеристик синтезируемой схемы; реализованы методы нелинейного программирования,автоматического размещения и трассировки топологии.

Список литературы Особенности разработки автоматизированной системы проектирования интегральных цифро-аналоговых преобразователей

- www.cadence.com/products/custom_ic/index.aspx http://www.cadence.com/products/custom_ic/index.aspx> Virtuoso Analog Design Environment User Guide//Cadence Design Sys. -Р. 27-53.

- Gielen G.G.E., Walscharts H.C.C., Sansen W.M.C. Analog circuit design optimization based on symbolic simulation and simulated annealing//IEEE J. Solid-State Circuits. June 1990, Vol. 25, No. 3. -P. 707-713.

- Cohn J.M., Garrod D.J., Rutenbar R.A., Carley L.R. Techniques for simultaneous placement and routing of custom analog cells in KOAN//ANAGRAM II. Proc. Int. Conf. on Computer-Aided Design. November 1991. -P. 394-397.

- Neff R.R. Automatic Synthesis of CMOS Digital/Analog Converters. Ph.D. dissertation. University of California at Berkeley, UCB/ERL. April, 1995. -P. 1-18.

- Iskander R. Synthesis of CMOS analog cells using AMIGO//Design, Automation and Test in Europe Conference and Exhibition, 2003. -P. 297-302.

- Зинченко Л.А. Интеллектуальные системы схемотехнического проектирования//Материалы Х РНК по искусственному интеллекту. М.: сентябрь, 2006. -С. 1-7.

- Yang Xu, Pileggi L.T., Boyd S.P. ORACLE: optimization with recourse of analog circuits including layout extraction//Design Automation Conference, 2004. -Р. 151-154.

- Arsintescu B.G., Otten R.H.J.M. Constraints space management for the layout of analog IC's//Design, Automation and Test in Europe. February, 1998. -Р. 971-972.