Применение стенда SDK 6.1 для отладки проектов в Altium Designer

Автор: Можный А.А., Болдырев А.В.

Журнал: Форум молодых ученых @forum-nauka

Статья в выпуске: 5 (9), 2017 года.

Бесплатный доступ

В статье рассматривается возможность использования учебно-лабораторного стенда SDK 6.1 для отладки проектов в Altium Designer. Приведена краткая информация о стенде. Описан процесс создания FPGA проекта в среде Altium Designer и загрузки файла конфигурации в стенд.

Плис

Короткий адрес: https://sciup.org/140278384

IDR: 140278384

Application of the stand SDK 6.1 for debug projects in the Altium Designer

The article considers the possibility of using the SDK 6.1 training and laboratory stand for debugging projects in Altium Designer. The brief information about the stand is given. Describes the process of creating an FPGA project in the Altium Designer environment and loading the configuration file into the stand.

Текст научной статьи Применение стенда SDK 6.1 для отладки проектов в Altium Designer

Во многих университетах для изучения основ проектирования цифровых устройств на базе ПЛИС используется учебно-лабораторный стенд SDK 6.1, разработанный более 10 лет назад. Функциональность стенда и встроенная основная ПЛИС семейства Cyclone, позволяют разрабатывать и производить отладку относительно несложных схем, что вполне достаточно для решения большинства учебных задач. В связи с этим возникает необходимость исследования возможности применения стенда для отладки проектов, созданных в современных САПР, например, таких как Altium Designer.

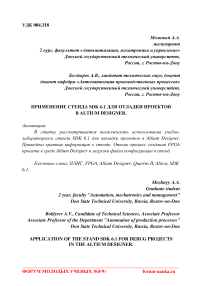

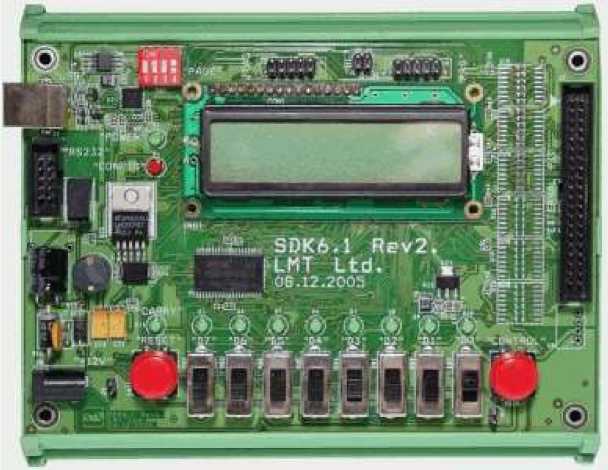

Конфигурация стенда SDK 6.1

Учебно-лабораторный стенд оснащён основной ПЛИС фирмы Altera семейства Cyclone EP1C6T144C8 с 2910 логическими элементами и 59Кбит ОЗУ. Помимо основной интегральной схемы в стенде установлена вспомогательная ПЛИС семейства MAX EPM3128ATC100 с 128 макроячейками.

Рисунок 1 – Внешний вид стенда

Стенд оснащён постоянной и оперативной памятью, разнообразными интерфейсными каналами, устройствами консольного ввода-вывода и надежной системой электропитания. В таблице 1 приведена информация о конфигурации стенда, а на рисунке 2 – его структурная схема.

Таблица 1 – Основные характеристики стенда

|

Описание конфигурации |

|

|

Компонент |

Тип/характеристика |

|

ПЛИС |

EP1C3T144-8 (2910LE, RAM 59Кбит, 1PLL) |

|

Вспомогательная ПЛИС |

EPM3128ATC100-10 |

|

Память FLASH |

1 Мб, до 8-ми конфигураций |

|

Память SRAM |

не устанавливается |

|

Память EEPROM |

256 байт |

|

Порт ввода/вывода |

24 разряда, без гальванической изоляции |

|

Порт последовательного интерфейса |

RS232 (1 канал, TxD/RxD, с гальванической изоляцией) |

|

Порт JTAG |

без гальванической изоляции |

|

Консоль |

ЖКИ 16*2 без подсветки, переключатели-8, светодиоды – 9 шт., кнопки – 1 шт. |

Рисунок 2 – Структурная схема стенда

САПР Altium Designer

САПР содержит базу данных о большинстве FPGA и CPLD устройств таких производителей ПЛИС как Xilinx, Altera, Lattice и Acctel, и периодически выпускает обновления для более новых версий. Инновационные решения, применённые в продукте, обеспечивают всеми необходимыми инструментами и технологиями для проектирования, внедрения, тестирования и отладки встраиваемых систем на базе ПЛИС в реальном времени.

Для программирования коммутации ПЛИС и отладки логики FPGA-проекта фирмой Altium Ltd разработано семейство отладочных стендов NanoBoard, на которых может быть выполнен полный цикл разработки проекта ПЛИС. Таким образом, пользователь, не имея большого опыта работы с FPGA, получает не связанную с риском среду разработки со всем, что требуется для начала [3].

Создание проекта в Altium Designer

САПР позволяет выбрать производителя ПЛИС, семейство, тип корпуса, и количество элементов. Для этого необходимо из меню выбрать DXP , затем Extension and Updates . В открывшемся окне следует выбрать вкладку Purchased , и во вложении Hardware Devices выбрать необходимую модель ПЛИС (рис. 3). В случае со стендом SDK 6.1 это Altera Cyclone первой модели. В результате произойдёт установка библиотеки, после чего программа попросит перезапуститься.

Рисунок 3 - Аппаратные устройства Altium Designer

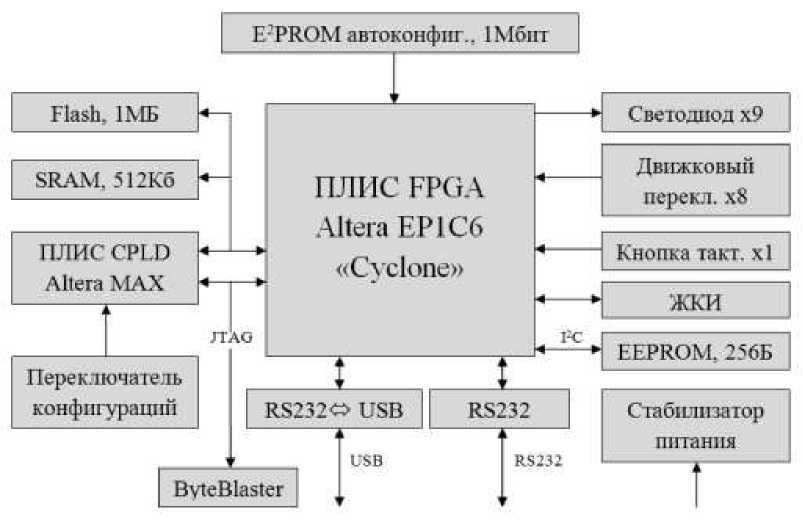

Для создания нового проекта на ПЛИС, следует выбрать из диалогового окна Files во вкладке New новый бланк проекта, Blank Project (FPGA) (рис. 4) или из основного меню выбрать File>New>Project>FPGA Project .

Рисунок 4 – Создание нового проекта

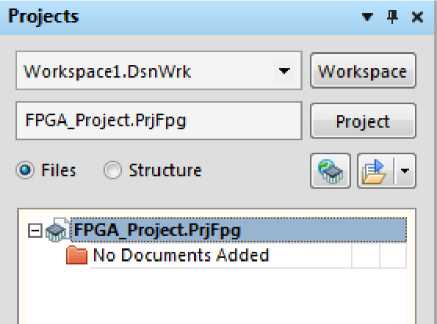

При этом создаётся файл с расширением *.PrjFpg , в котором будет сохраняться вся информация о проекте (рис. 5).

Рисунок 5 – Окно с новым проектом FPGA

Для проектирования логики ПЛИС Altium Designer поддерживает различные способы ввода данных, в том числе и на языках схемного ввода,

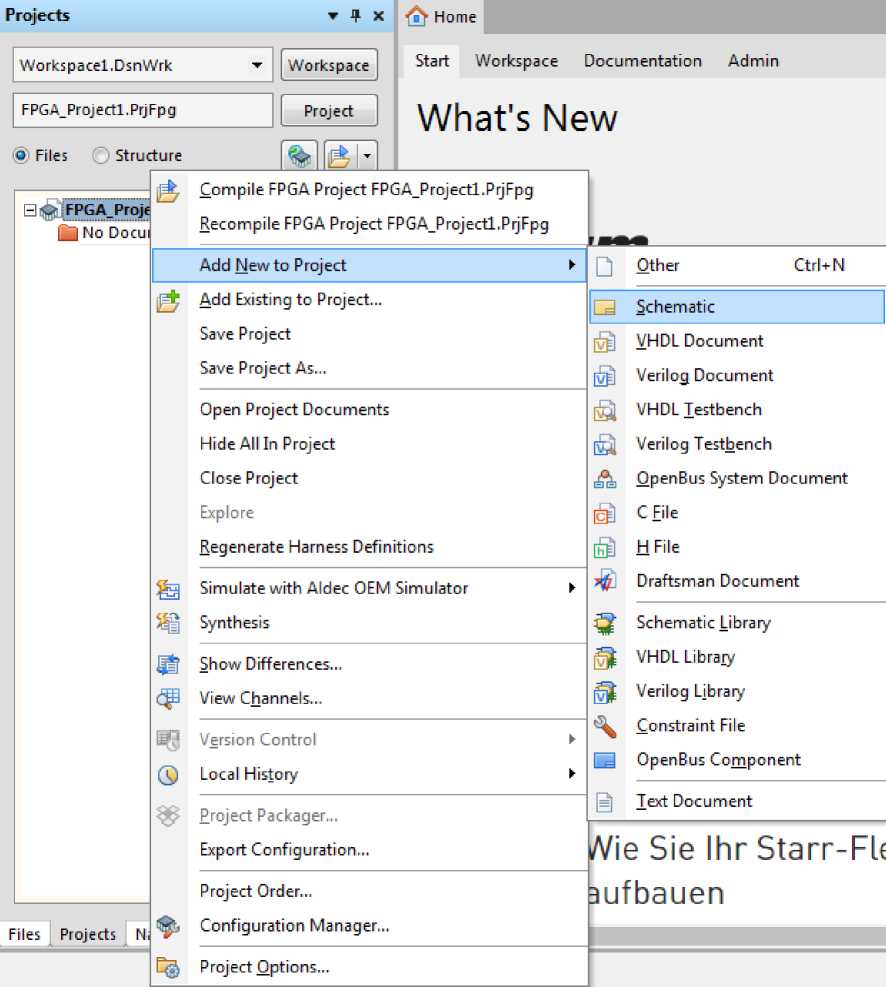

VHDL или Verilog HDL описаний логики, а также на языках С [1]. В качестве примера рассмотрим проектирование схемы счётчика Джонсона. Для выбора языка схемного ввода необходимо правой кнопкой мыши щёлкнуть на имени файла проекта на панели Projects и выбрать Add New to Project>Schematic (рис. 6).

Рисунок 6 – Выбор способа ввода данных

Необходимые компоненты для создания схемы можно найти в библиотеке FPGA Generic. Для её добавления на боковой вкладке Libraries следует выбрать кнопу Libraries. В открывшемся окне Available Libraries, выбрать Install>Install from file и указать путь …/Library/Fpga, где размещена библиотека. Затем в боковой вкладке выбрать найденный файл

Libraries

о

Libraries...

Search...

Place 2N3904

о

|Q

|Q

О

195 components

Q2N3904 Miscellan NPN General Purpo ■Q 2N3906 Miscellan PNP General Purpo; Q ADC-8 Miscellan Generic 8-Bit A/D G

■Q Antenna Miscellan Generic Antenna

ft о

Рисунок 7 – Выбор библиотеки

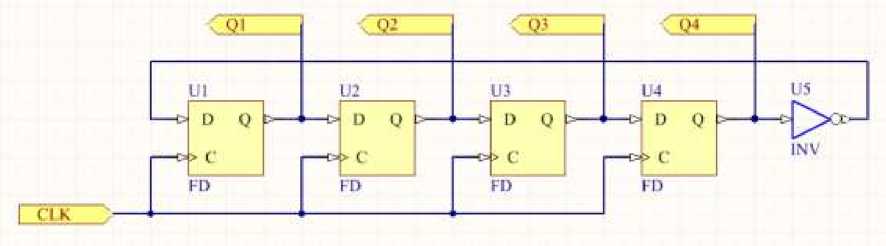

Из библиотеки необходимо выбрать элементы FD (D-триггер), INV (элемент инверсии), CLK (порт input), Q1…Q4 (порты output) (рис. 8).

Рисунок 8 – Схема соединений

После завершения процесса создания проекта, необходимо обработать исходные файлы. Обработка состоит из компиляции и синтеза проекта для получения списка соединений. Для проверки целостности проекта Altium Designer имеет мощный компилятор Design Compiler, который анализирует проект на наличие ошибок в соответствии с опциями, заданными на вкладках Error Reporting и Connection Matrix диалогового окна Options for FPGA Project. Результат компиляции можно посмотреть в всплывающем справа окне Messages.

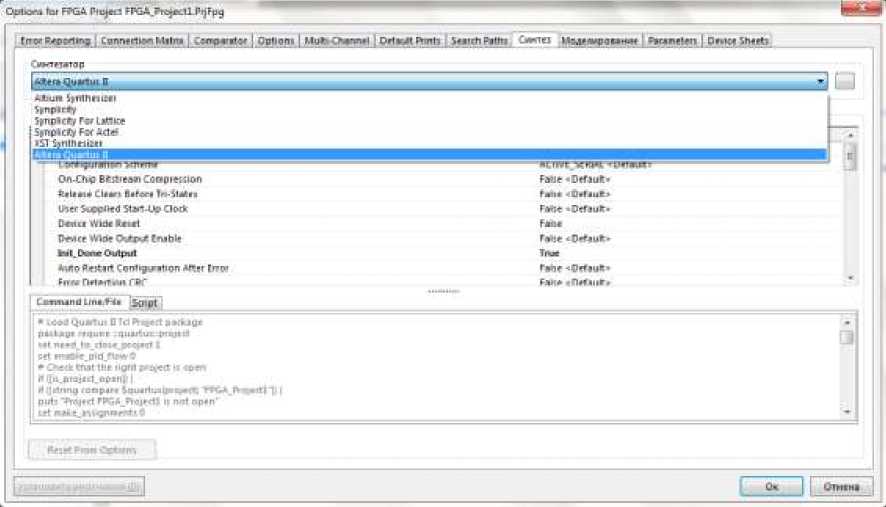

Система также включает встроенный механизм синтеза, который поддерживает использование синтезатора Altera Quartus II в среде разработки. Для того чтобы проект FPGA мог использовать этот инструмент синтеза, необходимо установить опцию синтеза проекта на Altera Quartus II. Для этого после щелчка правой кнопкой мыши на имени проекта FPGA, следует выбрать из подменю Project Options , перейти на вкладку Синтез и выбрать Altera Quartus II из выпадающего списка Синтезатор (рис. 9).

Рисунок 9 – Окно Options for FPGA Project

Работа с инструментами поставщика

Размещение и маршрутизация, процесс реализации дизайна FPGA для целевого устройства, требуют знания функциональности и архитектуры устройства, что лучше всего отображается в программных средствах, предоставляемых поставщиком устройства [5].

Программное обеспечение поставщика управляется средой Altium Designer, которая координирует все аспекты работы с проектами и файлами, необходимыми для создания файла программы FPGA [6]. Для получения доступа к инструментам поставщиков непосредственно из Altium Designer, следует выбрать из меню Tools пункт Vendor Tool Support .

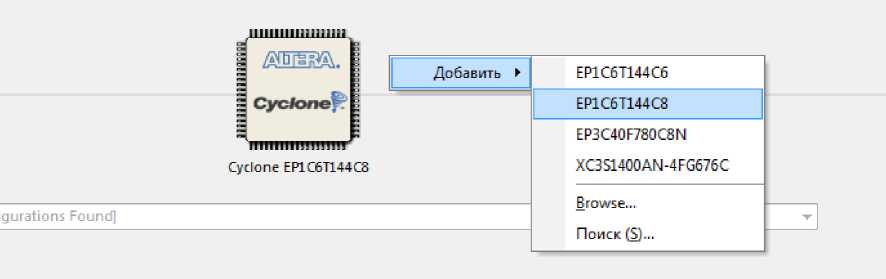

В случае со стендом SDK-6.1 инструменты Altera интегрированы и доступны в среде Altium Designer через представление устройства View > Devices View (рис. 10). Это представление позволяет поэтапно контролировать весь процесс проектирования FPGA, позволяя программировать и отлаживать конструкцию системы на FPGA.

Рисунок 10 –Добавление физического устройства

Инструменты размещения и маршрутизации доступны с этапа Build потока процессов, связанного с целевым физическим устройством в представлении устройства [7]. Чтобы включить и отобразить процесс, когда целевым устройством является ПЛИС Altera, необходимо установить инструменты поставщика Altera - либо полный набор инструментов, либо свободно загружаемую версию, доступную на веб-сайте Altera.

Параметры процесса сборки

Процесс сборки позволяет взаимодействовать с инструментами Altera и создавать файлы программы устройства, такие как Raw Binary Files ( .rbf ) для загрузки в целевое устройство FPGA. Нажимая стрелку « ↓» , можно получить список отдельных этапов, используемых для совершения процесса сборки (рис 11).

^►♦@9*i ^ ► * @ Proyrm EPGA

-

# ТгЯВИб DtiigTi ; J В--- ДШШ ^ Цф Design 1В В iSQ # Наев and Acute i -ч El ^ IWifl AVal-.-iis Й Ei

-

-= C*”' » мане вг Fie i @------------------

- гтттттттттг

Рисунок 11 - Этапы процесса сборки

Для выполнения настроек достаточно щелкнуть значок в (Параметры) рядом с каждым этапом. Ошибки или правила проектирования, которые не разрешены для целевой архитектуры или дизайна регистрируются на каждом этапе процесса сборки. Местоположение в дизайне, а также ошибка или предупреждение помещаются в файл отчета, доступ к которому осуществляется нажатием на соответствующий значок l=i .

Translate Design

На этом этапе создаются сценарии Quartus II TCL (TCLQ), параметры и файлы проекта, которые используются всеми последующими этапами процесса сборки. Сценарий QuartusII TCL связывает файлы FPGA_HexMultiplier_constraints.tcl и FPGA_HexMultiplier_macros.tcl, сгенерированные из потока процесса Synthesis. Затем файл TCLQ выполняется с помощью Quartus II Shell (Quartus_sh) и ключа -t . Если необходимо, проект Altera можно также открыть в Quartus.

Map Design To FPGA

Place and Route

На этом этапе запускается инструмент Quartus II Fitter ( Quartus_Fit ) и файл сценария Quartus II TCL (TCLQ) для размещения и маршрутизации проекта для целевой FPGA. Он объединяет файлы, сгенерированные из процесса Map Design To FPGA.

Timing Analysis

На этом этапе запускается инструмент Quartus II Timing Analyzer ( Quartus_Tan ) для анализа скорости и производительности реализованной логики для целевой ПЛИС. Параметры анализа можно настроить, щелкнув значок «Параметры».

Make Bit File

Этот процесс запускает инструмент Quartus II Assembler ( Quartus_Asm ) для генерации программируемых и конфигурационных файлов устройства Altera, таких как выходные файлы Hexadecimal ( .hexout ), Raw Binary Files ( .rbf ), Jam Files ( .jam ), Jam Byte-Code Files ( .jbc ) и Serial Vector Format Files ( .svf ) для загрузки в ПЛИС.

Загрузка файла конфигурации в ПЛИС.

Перед загрузкой файла конфигурации, необходимо подключить разъём J6 стенда SDK-6.1 к USB-порту компьютера при помощи интерфейсного кабеля и подключить питание. Затем, чтобы перевести стенд в режим загрузки через USB-порт, необходимо нажать кнопку «CONTROL», после чего на ЖКИ стенда появится сообщение: «SDK6.1 USB Flash Writer».

SDK61FW 3.4 Copyright (c) LMT Ltd. July 2005

Usage: SDK61FW write tla_address filename serial_port_name [page0_we]

Usage: SDK61FW write page_name filename serial_port_name [page0_we]

Usage: SDK61FW read tla_address size filename serial_port_name

Далее следует повторить предыдущую операцию путём нажатия на клавиатуре клавиши « ↑ » и дописать следующее: write - режим записи во FLASH-память, page_name - номер страницы во FLASH-памяти, а также путь к размещению файла конфигурации с расширением .rbf и имя последовательного порта serial_port_name , номер которого можно определить в Диспетчере устройств компьютера. После нажатия на клавишу Enter будет запущен процесс записи. Описанные выше операции в командной строке проиллюстрированы на рис. 12.

SDK61FW 3.4 Copyright

Usage: SDK61FU write tla_address filename serial_port_name [page0_wel

Usage: SDK61FU write pagejiane filename serial_port_name [page0_we]

Usage: SDK61FU read tla_address size filename serial_port_name

SDK61FW 3.4 Copyright

TLA: 20000

Total 114 packets

Transfer speed ... 3.590017 KBytes/sec

Real speed ....... 8.979250 KBytes/sec

C:\Users\DDR4>

Рисунок 12 – Загрузка файла конфигурации в ПЛИС стенда

По окончании записи, необходимо задать номер страницы памяти с помощью переключателя Page и нажать на кнопку RESET стенда. Произойдет перезапуск системы стенда, в результате чего будет произведена запись файла конфигурации из указанной страницы FLASH-памяти.

Для корректной записи необходимо помнить, что нумерация переключателей в стенде идет в обратном порядке, т.е. при указании страницы page1 для записи во FLASH-память, необходимо переключить page4, при page2 – page3 и т.д.

Заключение.

Благодаря большой базе данных FPGA и CPLD устройств, система автоматизированного проектирования Altium Designer позволяет разрабатывать проекты независимо от типа стенда и установленной ПЛИС, что позволяет сэкономить на приобретении нового оборудования и обеспечивает актуальность имеющегося. А интеграция с инструментами поставщика, например Quartus II, позволяет упростить процесс создания проекта, его адаптацию и отладку на стендовом оборудовании сторонних производителей.

Список литературы Применение стенда SDK 6.1 для отладки проектов в Altium Designer

- Карякин А. Т., Хакулов А. М. Основные возможности САПР Altium Designer // Молодой ученый. - 2014. - №2. - С. 146-148.

- По материалам сайта Altium [Электронный ресурс] - Режим доступа: http://wiki.altium.com/pages/viewpage.action?pageId=25079991 (дата обращения: 19.04.17)

- По материалам сайта Altium [Электронный ресурс] - Режим доступа: http://www.altium.com/company/newsroom/press-releases/best-both-worlds-altium-adds-high-performance-low-cost-option-its (дата обращения: 19. 04.17)

- По материалам сайта Altium [Электронный ресурс] - Режим доступа: http://wiki.altium.com/pages/diffpagesbyversion.action?pageId=4423996&originalVersion=1&revisedVersion=5 (дата обращения: 25.04.17)

- По материалам сайта Altium [Электронный ресурс] - Режим доступа: http://techdocs.altium.com/display/FPGA/Working with Altera Devices and Place and Route Tools# (дата обращения:27.04.17)

- По материалам сайта Altium [Электронный ресурс] - Режим доступа: http://techdocs.altium.com/display/FPGA/Vendor Tool Installation (дата обращения: 30.04.17)

- По материалам сайта Altium [Электронный ресурс] - Режим доступа: http://techdocs.altium.com/display/FPGA/Altera Place and Route Tools Configuration# (дата обращения: 30.04.17)