Реализация криптографического алгоритма RC6 на FPGA

Автор: Шапиев М.М., Серов С.С., Никитин К.И., Серов С.А.

Журнал: Форум молодых ученых @forum-nauka

Статья в выпуске: 5-3 (21), 2018 года.

Бесплатный доступ

Блочные шифры являются одними из самых распространенных шифров в современной вычислительной технике. Эти шифры одни из самых требовательных к вычислительным ресурсам, поэтому для реализации этих криптографических алгоритмов, можно использовать FPGA (со кр. field programmable gate array - программируемая пользователем вентильная матрица). В данной работе мы реализуем криптографический алгоритм RC6 на FPGA фирмы Altera и анализируем эту реализацию.

В статье рассматриваются: криптография, шифрование, плис, цифровая схемотехника, блочные шифры

Короткий адрес: https://sciup.org/140283058

IDR: 140283058

Implementation of cryptographic algorithm RC6 on FPGA

Block ciphers are one of the most common ciphers in modern computer technology. These ciphers are one of the most demanding of computational resources, so to implement these cryptographic algorithms, you can use FPGA (short programmed gate matrix - user-programmable gate array). RC5 on the FPGA of Altera and analyze this implementation.

Текст научной статьи Реализация криптографического алгоритма RC6 на FPGA

FPGA и алгоритм RC6

Для начала рассмотрим преимущества FPGA перед другими архитектурами. Во-первых, главным преимуществом FPGA является более низкое энергопотребление и низкая рабочая частота, во-вторых, при реализации каких-либо проектов на FPGA, микросхема становится узкоспециализированной архитектурой для решения отдельного рода задач. Исследования показывают, что почти все проекты, реализованные на них, дают большую производительность (в соотношении производительность-энергопотребление) чем на той же архитектуре x86-x64 или ARM. FPGA программируются путем изменения логики работы принципиальной схемы, например, на языке описания аппаратуры Verilog. Они являются одним из видов ПЛИС (сокр. программируемые логические интегральные схемы) [3]. Главной целью реализации алгоритма RC6 на FPGA является получение более эффективного использования ресурсов кристалла и добиться максимальной скорости шифрования.

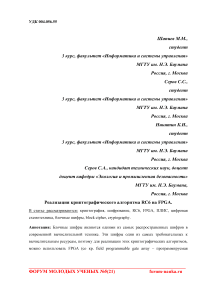

Алгоритм RC6 [1] – симметричный блочный шифр, является усовершенствованной версией своего предшественника RC5. Этот алгоритм является одним из пяти финалистов конкурса AES и считается очень надежным, при использовании генератора псевдослучайных последовательностей с большим периодом и без серьезных уязвимостей. Он работает с блоками данных длиной 128 бит и ключами 128-256 бит. Из-за присутствия в алгоритме операции умножения, реализация на некоторых аппаратных платформах является затруднительной задачей. RC6 как и свой предшественник RC5 – параметризированный алгоритм шифрования с обозначениями RC6-w/r/b, где w – длина машинного слова в битах, r – количество раундов шифрования, b – длина ключа (0-255 байт). В качестве ключей в RC6 используется таблица ключей идентичная той что используется в RC5, но она больше зависит от введенного пользователем ключа. Схема алгоритма выглядит следующим образом(Рис.1). Входные и выходные данные расположены в переменных A, B, C, D. В массиве £[0. .2г + 3] хранится таблица ключей.

Рис.1 Схема работы алгоритма RC6

Для генерации таблицы ключей используется следующий алгоритм [4]:

Входные данные - L[0.. с — 1] - массив полученный из c-слов введенных пользователем в качестве ключа, r - количество раундов.

Выходные данные - S[0. .2г + 3] - таблица ключей.

S[0]=Pw for i=1 to 2r+3 do

S[i]=S[i-1]+Qw

A=B=i=j=0

v=3*max{c,2r+4} for s=1 to v do {

A=S[i]=(S[i]+A+B)<<<3

B=L[j]=(L[j]+A+B)<<<(A+B) i=(i+1) mod (2r+4) j=(j+1) mod c }

Pw = В7Е151631б и Qw = 9Е3779В91б - константы, получаемые при помощи формул:

ф№ <—0<И((/— 1) ♦ 2W)Pw <- Odd^e - 2) * 2W).

Процедура шифрования выглядит следующим образом:

B = B +S[0]

D = D +S[1]

for i = 1 tor

{

|

t |

= (B(2B + 1)) <<< |

lg w |

|

u |

= (D(2D + 1)) <<< |

lg w |

|

A |

= ((A ф t) <<< u) |

+ S[2i] |

|

C |

= ((C ф u) <<< t) + S[2i + 1] (A, B, C, D) = (B, C, D, A) |

|

}

A = A + S[2r +2]

C = C + S[2r +3]

Зашифрованный текст сохраняется в A,B,C,D. В качестве входных данных, поступает открытый текст, сохраненный в A,B,C,D, таблица ключей S[0..2r + 3] и количество раундов г.

Процедура расшифровки выполняется следующим образом:

C = C - S[2r + 3]

A = A - S[2r + 2]

for i = r downto 1 do {

(A, B, C, D) = (D, A, B, C)

u = (D(2D + 1)) <<< 1gw t = (B(2B + 1)) <<< lgw

C = ((C - S[2i + 1]) >>> t) ф u

A = ((A - S[2i]) >>> u) ф t

} D = D - S[1]

B = B - S[0]

В качестве входных данных поступает зашифрованный текст, хранящийся в A,B,C,D, количество раундов г и таблица ключей. Расшифрованный текст так же сохранятся в A,B,C,D.

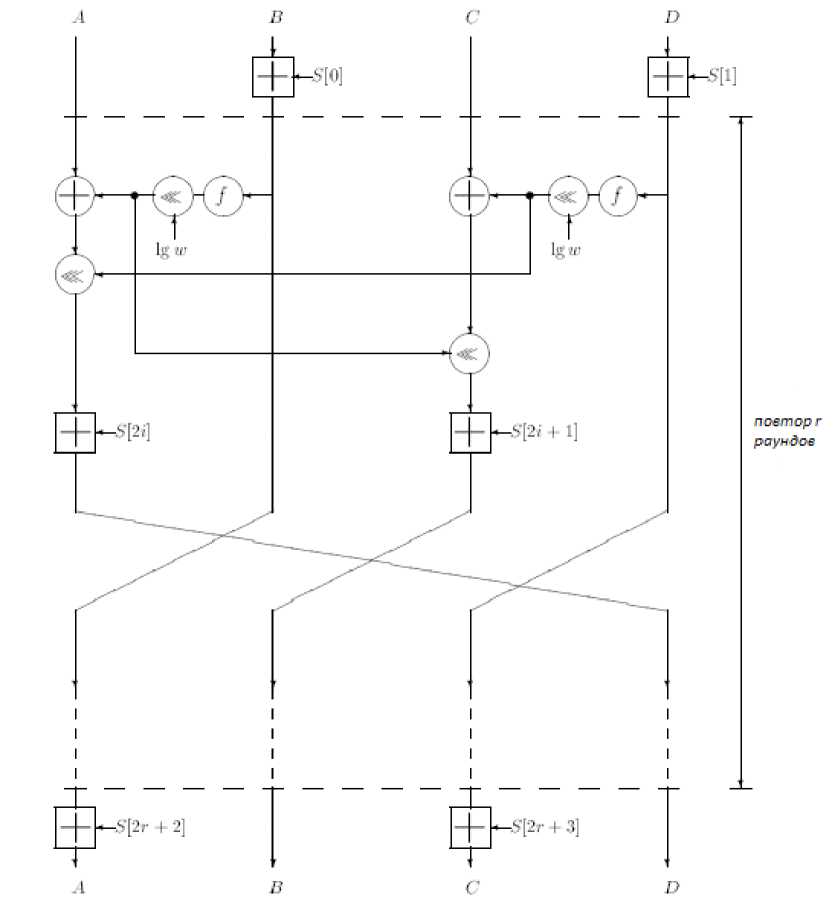

Рассмотрим FPGA фирмы Altera с кодовым названием Arria II GX EP2AGX125. Это кристалл с 118 ПЛБ (программируемый логический блок), работающий на штатной частоте 125 МГц. Этого FPGA будет достаточно для реализации нашего криптоалгоритма, при увеличении числа модулей, необходимо взять кристалл с большим числом ПЛБ.

Схема реализации криптоалгоритма на FPGA полностью выглядит следующим образом (Рис.2):

Рис.2 Схема реализации на FPGA

Код реализации алгоритма шифрования на языке Verilog (синтаксис языка приведен в [2]):

module RC6_encrypt (open_Text, encrypt_Text, S );

( input [7:0] S [0:43]; // т.к. у нас r=20 размерность S равна 44.

input [31:0] open_Text [0:3]; // аналог 32-битных А, B, C, D для хранения открытого текста output [31:0] encrypt_Text [0:3]; // на выходе получаем зашифрованный текст reg [31:0] text [0:3];

assign text=open_Text;

reg [7:0] Skey [0:43];

text[1] = text[1] + Skey[0];

text[3] = text[3] + Skey[1];

reg [7:0]

reg [7:0]

reg [7:0]

reg [31:0] temp32; // буфер для перестановки for(i=0; i<20; i=i+1)

begin t = (text[1] *(2* text[1] + 1)) <<2

u = (text[3] *(2* text[3] + 1)) <<2

text[0] = ((text[0] ^ t) << u) + Skey[2*i]

text[2] = ((text[2] ^ u) << t) + Skey[2*i +1]

temp32 = text [0]; // меняем местами A и B text[0]= text [1];

text[1]=temp32;

temp32 = text [3]; // меняем местами D и B text[3]= text [1];

text[1]=temp32;

temp32 = text [2]; // меняем местами C и B в итоге получаем нужную перестановку text[2]= text [1];

text[1]=temp32;

end text[0] = text[0] + Skey[2*i + 2];

text[2] = text[2] + Skey[2*i + 3];

assign encrypt_Text=text; // передаем на выход зашифрованный текст

)

Модуль для расшифровки выглядит следующим образом:

module RC6_decrypt (open_Text, encrypt_Text, S );

( input [7:0] S [0:43]; // т.к. у нас r=20 размерность S равна 44.

output [31:0] open_Text [0:3]; // аналог 32-битных А, B, C, D для хранения открытого текста input [31:0] encrypt_Text [0:3]; // зашифрованный текст reg [31:0] text [0:3];

assign text=open_Text;

reg [7:0] Skey [0:43];

text[1] = text[1] + Skey[0];

text[3] = text[3] + Skey[1];

reg [7:0]

reg [7:0]

reg [7:0]

reg [31:0] temp32; // буфер для перестановки for(i=20; i=0; i=i-1)

begin temp32 = text[0]; // меняем местами A и B text[0]= text[1];

text[1]=temp32;

temp32 = text[3]; // меняем местами D и B text[3]= text [1];

text[1]=temp32;

temp32 = text[2]; // меняем местами C и B в итоге получаем нужную перестановку text[2]= text[1];

text[1]=temp32;

t = (text [1] *(2*text[1] + 1)) << 2;

u = (text[3] *(2*text[3] + 1)) << 2;

text[2] = ((text[2] - key[2*i + 1]) >> t) л u;

text[0] = ((text[0] - key[2*i]) >> u) л t;

end text[3] = text[3] - key[1];

text[1] = text[1] - key[0];

assign open_Text=text; // передаем на выход открытый текст

)

Заключение

Практические испытания показали, что данная реализация обходит по производительности реализации на архитектурах x86 и ARM. Это объясняется тем что в шифре RC6 очень много битовых операций, которые на FPGA выполняются на порядок быстрее. Так же данную реализацию можно с минимальным числом изменений адаптировать под любой FPGA фирмы Altera. Операцию умножения можно так же заменить на XOR для увеличения производительности. Но в этом случае зашифрованный текст становится уязвимым для дифференциального и частотного криптоанализа. На кристалле Arria II GX EP2AGX125 при частоте 125 MHz показывает скорость примерно равную 917 Mb/sec. Так же данная реализация позволяет масштабировать алгоритм на других платформах. На более развитых по структуре и числу ПЛБ моделях FPGA, можно реализовать параллельное шифрование (расшифровку) данных алгоритмом RC6. При этом, рост производительности в этих операциях будет пропорционален количеству ПЛБ и тактовой частоте.

Список литературы Реализация криптографического алгоритма RC6 на FPGA

- Шнайер Б. Прикладная криптография. 2-е издание, М.: Триумф, 2002, 816 с.

- Спиридонов С.Б. Курс лекций по Вычислительные системы АСОИУ. М.: МГТУ им. Баумана, 2017. 224 c.

- Спиридонов С.Б. Курс лекций по схемотехнике дискретных устройств. М.: МГТУ им. Баумана, 2017. 204 c.

- Дэвид Харрис М. Сара Харрис Л. Цифровая схемотехника и архитектура компьютера, М.: Morgan Kaufman, 2013, 792 с.

- Ronald L. Rivest, M.J.B. Robshaw, R. Sidney, and Y.L. Yin. "The RC6 Block Cipher". Cambridge, M.I.T.: 1998, 21 p.

- Акчурин А.Д., Юсупов К.М. Программирование на языке Verilog. Учебное пособие. Казань, 2016. 90 с.