Управляемый модуль операторами логической свертки

Автор: Лукашевич Тина Витальевна, Сивков Степан Игоревич, Новиков Леонид Григорьевич

Журнал: Спецтехника и связь @st-s

Статья в выпуске: 1, 2013 года.

Бесплатный доступ

В статье рассматривается реализация управляемого модуля обработки сигналов на операторах логической свертки.

Р-ряд, z-ряд, синхронная логическая свертка, оператор логической свертки, управляемый модуль логической свертки

Короткий адрес: https://sciup.org/14967136

IDR: 14967136

Текст научной статьи Управляемый модуль операторами логической свертки

С овременные преобразовательные устройства имеют модульную конструкцию. Каждый модуль состоит из большого числа микросхем, к внутренним элементам которых нет необходимого доступа. В отличие от схем на дискретных компонентах в модулях теряется гибкость управления такими приборами, поскольку нет возможности изменять параметры микросхем. Если ряд элементов с разными значениями или характеристиками объединить в одну микросхему и управлять ими при помощи программируемых ключей, то можно достаточно легко перестраивать параметры всей преобразовательной системы. Поэтому задача создания управляемых операторов логической свертки (ОЛС) является актуальной.

Логические операции с PZ-рядами

Синхронный унитарный сигнал (СУС) ‒ синхронная последовательность единиц, в которой информационная величина представляется в виде Р-ряда (P- prima) или Z-ряда (Z-zero). Информационным параметром является длина (NР) Р-ряда и длина (Nz) Z-ряда.

На дискретной шкале СУС может быть представлен в алгебраической или логической форме, например:

А(p)= Pk + Pm , или А(p) = Pk ∨ Pm , где k , m ‒ показатели степени, определяющие местоположение переменной P в ряду.

Для компактности удобно пользоваться векторной формой записи многочленов, например:

А(p) = А(k,m) = Pk+ Pk+1+ Pk+2+ ... +Pm , где k – начало, m ‒ конец ряда, «,» символ итерации (продолжения) ряда. В результате такого представления преобразование сигналов может быть сведено к преобразованию PZ-рядов, и формализовать логическую обработку сигналов.

Логические схемы в сочетании с синхронными элементами задержки по- зволят выполнять различные операции с унитарными рядами: расширение, ограничения, выделение фронтов, удвоение, селекцию по длине ряда, выборку комбинаций по шаблону, проверку условий, умножение и деление на фиксированный многочлен, преобразование, кодирование и декодирование комбинационных рядов.

При описании синхронных величин удобно использовать запись комбинаций в виде многочлена с фиктивной переменной. Индекс фиктивной переменной показывает местоположение переменной в разрядной сетке логического слова или величину задержки.

Синхронную логическую функцию, определяющую соответствие между логическими выражениями исходных двоичных последовательностей и задержанных по очереди, будем называть синхронной логической сверткой [1]. Для формализации анализа и синтеза синхронных унитарных устройств введен оператор логической свертки:

C(pn+m) = A(pn) Θ В(pn+1),

где A(p) =a0P0+a1P1+a2P2+ ... ‒ входная последовательность, ai ={0,1} – переменная, которая определяет наличие или отсутствие переменной pi в многочлене А(p) , В(p ) =A(p) , p ‒ многочлен задержки входной последовательности, Θ ‒ символ логической операции из множества W[ ∧ , ∨ , ⊕ , ▷ , ◁ ], где ∧ ‒ конъюнкция, ∨ ‒ дизъюнкция, ⊕ ‒ сложение по модулю два, ▷ ‒ прямой запрет, ◁ ‒ обратный запрет.

Из всего многообразия функций логической свертки выделены основные классы функционально полных наборов элементарных логических функций:

Сδ(p) = A(p) ∨ B(p) → СДС, СΚ(p) = A(P) ∧ B(P) → СКС, Cϕ(p) = A(P) ∧ B(P) → СФС, (1)

Cs(p) = A(P) ∧ B(P) → ССС, Cµ(p) = A(P) ⊕ B(P) → СМС.

Синхронная дизъюнктивная свертка (СДС) преобразует синхронный последовательный сигнал – увеличивает количество единичных интервалов СУС на величину К Д (количество последовательно включенных элементов СДС). Синхронная конъюнктивная свертка (СКС) преобразует синхронный последовательный сигнал – уменьшает количество единичных интервалов СУС на величину КК (количество последовательно включенных элементов СКС).

Синхронная свертка по модулю два (СМС) преобразует синхронный последовательный сигнал – выделяет стробы, совпадающие с первыми интервалами FP и FZ единичных и нулевых последовательностей, то есть отмечает (маркирует) все перепады значений входной последовательности.

Синхронная конъюнктивная свертка с инверсией задержанной входной переменной (СФС) преобразует синхронный последовательный сигнал – вырабатывает импульс Fp , совпадающий с первым интервалом последовательности единиц.

Синхронная конъюнктивная свертка с инверсной входной переменной (ССС) выделяет строб FZ , идентифицирует скачок последовательности нулей.

При ограничениях по количеству входов целесообразно создать программируемый модуль, позволяющий реализовать функционально полный набор логических сверток. Если на адресные сигналы каналов мультиплексора подавать задержанную и не задержанную синхронную последовательность, а на информационные входы ‒ управляющие сигналы, то получим модуль, который реализует полный набор логических сверток (1) и любые преобразования синхронной импульсной последовательности. Схемы основных видов свертки и их отклики на синхронный последовательный сигнал приведены в табл. 1.

Управляемый модуль операторов логической свертки

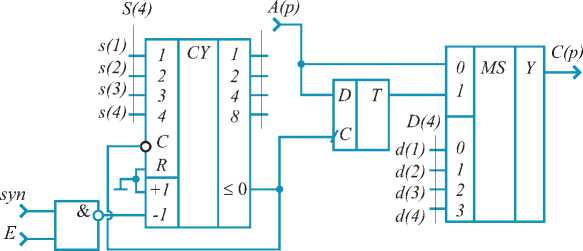

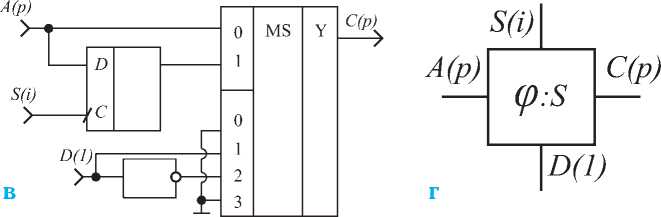

В рассматриваемом модуле логической свертки применены ( рис. 1 ) две функции:

-

□ программирование операторов логической свертки с помощью мультиплексора MS;

-

□ управление частотой синхронизации с помощью преобразователя код-частота на основе СТ ‒ вычитающего счетчика с предустановкой.

Данное схемотехническое решение позволит получить необходимый вид

Таблица 1. Основные виды сверток

|

Вид свертки |

Управляющий код для MS |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

1 |

1 |

1 |

1 |

|

сдс С5(р)= А(р) v В(р) |

1110 |

|||||||||||||

|

Г |

Г |

|||||||||||||

|

скс С,(р)= А(р) л В(р) |

1000 |

|||||||||||||

|

СФС Сф(р)=А(р)лВф) |

0010 |

|||||||||||||

|

ссс Cs(p)=A(p)aB(p) |

0100 |

|||||||||||||

|

СМС |

ОНО |

|||||||||||||

|

Cfl(p)= А(р) ® В(р) |

Рис. 1. Управляемый модуль свертки с реверсивным счетчиком

оператора и заданную кратность сверточного преобразования путем задания периода синхронизации и уменьшения количества однотипных операторов до одного.

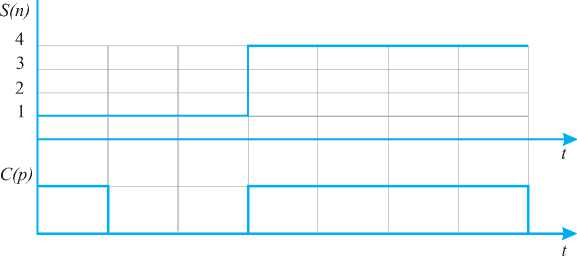

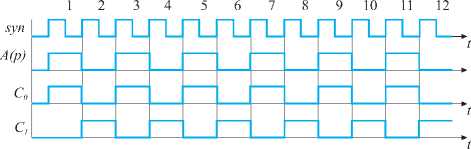

Кодовое управление частой синхронизации в схеме, представленной на рис. 1 , иллюстрируется временными диаграммами ( рис. 2 ). В начале преобразовательного цикла сигналом «р < 0» с выхода счетчика СТ записывается код задания частоты синхронизации и начинается процесс вычитания. При изменении логического уровня «р < 0» цикл повторится. Таким образом, можно получить оптимизацию аппаратных средств для случая последовательного включения однотипных операторов свертки.

Реализация преобразователей

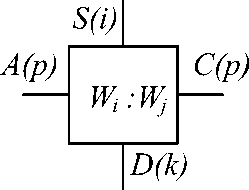

Для конструкторской документации проектируемых устройств введем условно-графическое обозначение (УГО) управляемого модуля логической свертки (УМОЛС) ( рис. 3 ), где А(Р) , С(Р) ‒ вход и выход оператора, D(k) – управ-

Рис. 2. Влияние частоты синхронизации на работу ОЛС

Рис. 3. УГО управляемого оператора логической свертки

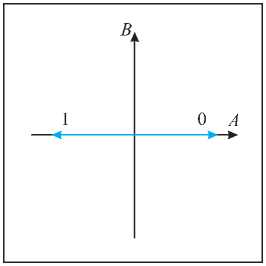

A ,01010101010101010,

X ,00000011111110000, а С ,01010110101010010,

б

Рис. 4. Переходные диаграммы (а), векторная диаграмма (б), принципиальная схема (в), УГО (г) и временные диаграммы однобитового ФИМ (д)

ляющий вход, S(i) – синхронизация, Wi j – управляемые операторы логической свертки.

В качестве примера динамического управления операторами свертки рассмотрим однобитовый фазовый модулятор, выполненный на управляемых операторах { ϕ:s } ( рис. 4 ).

Процедура свертки однобитовой фазоимпульсной модуляции (ФИМ): ‒

Сфим ← A c (Ds + Dϕ)}

Схема ФИМ выполнена на универсальном модуле свертки, где при действии управляющего сигнала D = 0 выполняется процедура { ϕ }, фазовый сдвиг P-рядов А и С равен нулю, а при действии D = 1 – выполняется процедура { s } и P-ряды переменных А и С в будут в противофазе. Аналогичным образом могут быть построены двух- и трехбитовые модуляторы [2].

На основе универсального модуля свертки могут быть построены широтные и фазо-импульсные модуляторы [3], конвейерные модуляторы, иден- тификаторы разделительных стробов, широтные и частотные идентификаторы по уровню «больше» или «меньше» [4], фазовые дискриминаторы и конверторы.

Заключение

На основе УМОЛС можно построить широтные, частотные и фазовые идентификаторы по верхнему и нижнему уровню дискриминации, конверторы, компараторы, экстрематоры, арбитры и другие устройства. В многоконтурных сетях изменять маршруты прохождения рядов.

Таким образом, можно заключить, что представление сигналов в виде PZ-рядов и формирование процедур преобразования PZ-рядов с помощью управляемого модуля логических операторов свертки, представляют собой новое, альтернативное цифровой обработке сигналов, научное направление логической обработки сигналов ■

Список литературы Управляемый модуль операторами логической свертки

- 1,Новиков Л.Г. Синхронная логическая свертка./Сборник научных трудов. -М.: МИФИ, 2005. -Т. 12. -С. 60.

- Сивков С.И., Новиков Л.Г. Фазоимпульсный модулятор на основе конвейерной логической сети./Вестник ЮУрГУ. Сер. Компьютерные технологии, управление, радиоэлектроника, 2012. -№ 17. -С. 165 -167.

- Кревский А.К., Сивков С.И., Новиков Л.Г. Фазо-импульсный модулятор на ОЛС./XII научно-практическая конференция «Дни науки ОТИ НИЯУ МИФИ -2012». Материалы конференции. Озерск, 2012. -Т.2. -С. 15 -16.

- Сивков С.И., Новиков Л.Г. Частотный идентификатор на перекрестной свертке./XV Международная телекоммуникационная конференция молодых ученых и студентов «Молодежь и наука». Тезисы докладов. В 3-х частях. Ч. 3. -М.: НИЯУ «МИФИ», 2012. -С. 101 -102