Архитектура отказоустойчивого запоминающего устройства для бортовых систем управления летательными аппаратами

Автор: Евдокимов А.П., Назаров А.А., Рябцев В.Г.

Журнал: Физика волновых процессов и радиотехнические системы @journal-pwp

Статья в выпуске: 2 т.20, 2017 года.

Бесплатный доступ

В статье решается задача повышения коэффициента технической готовности модулей памяти, значение которого возрастает при уменьшении времени восстановления системы управления при отказе входящих в нее устройств. Предлагается структура модулей памяти со встроенными средствами самотестирования и восстановления работоспособности, что позволит выполнить автоматическую замену разрядов данных основного массива запоминающих ячеек, в которых произошли отказы, на данные, поступающие с выходов запасного массива запоминающих ячеек. Автоматическую реконфигурацию модуля памяти при обнаружении отказа обеспечивают предлагаемые аппаратные и программные средства.

Запоминающее устройство, самотестирование, встроенные средства восстановления работоспособности

Короткий адрес: https://sciup.org/140256000

IDR: 140256000

Architecture of fault-tolerant storage device for onboard control systems of spacecraft

The problem of increasing technical readiness coefficient memory, the value of which increases with decreasing control system recovery time in case of failure of its constituent units. The proposed structure of the memory module with built-in self-test and restore functionality that will allow you to auto-replace bits of data of the main memory cell array, in which there have been failures in the data output from the spare memory cell array. Automatic reconfiguration of the memory module when a fault is detected provides the proposed hardware and software.

Текст научной статьи Архитектура отказоустойчивого запоминающего устройства для бортовых систем управления летательными аппаратами

Основными компонентами микроэлектронных систем управления летательными аппаратами являются запоминающие устройства, которые хранят программы и применяются при выполнении алгоритмов управления. Оперативная память является одним из самых надежных компонентов, потому что производители модулей памяти очень тщательно тестируют свою продукцию прежде, чем она попадет на рынок и в готовые изделия. К надежности бортовых микроэлектронных систем управления летательными аппаратами с продолжительным сроком эксплуатации предъявляются повышенные требования. Для этого часто производят отбраковку элементов с низкой надежностью. Однако, отбраковка потенциально ненадежных запоминающих устройств (ЗУ) по результатам их диагностического контроля [1–5] или прогнозирования качества [6–8] является часто малоэффективной. В связи с этим целесообразно увеличивать коэффициент технической готовности, значение которого возрастает при уменьшении времени восстановления системы управления при отказе входящих в нее устройств.

В процессе полета могут возникать электростатические разряды, учет и устранение кото- рых является весьма проблематичным [9; 10]. В микросхемах памяти под воздействием статического электричества, миграции электронов из-за высокой проводимости окислов, туннельного эффекта и т. д. со временем могут возникать отказы и сбои из-за нестабильности зарядов, которые могут привести к катастрофам при длительных полетах летательных аппаратов. Если при тестировании будут обнаружены неработоспособные модули, то их следует заменить на исправные модули. Однако при этом затрачивается время на поиск аналогичного модуля памяти и на проверку валидности таймингов, значение которых указанно в SPD. Значительные затраты времени на восстановление бортовой системы управления могут привести к непоправимым последствиям.

Запоминающие устройства, в которых применяются корректирующие коды типа ECC (Error Check&Correction/Error Correction Code ) , способны автоматически исправлять любые одиночные ошибки и обнаруживать любые двойные. До тех пор, пока оперативная память функционирует более или менее нормально, противостояние энтропии и помехозащитных кодов решается в пользу последних. Однако при полном или частичном выходе одного или нескольких моду

лей памяти из строя, корректирующих способностей контролирующих кодов недостаточно и оперативная память начинает работать крайне нестабильно.

Мажоритарное резервирование требует дополнительного введения нескольких устройств целиком, что увеличивает вес изделия, что нежелательно для авиакосмических систем.

Известна система с анализом возможности замены строк и столбцов встроенной памяти на запасные, которая содержит средства встроенного самотестирования (BIST, Built-In Self Test), средства встроенного анализа восстановления работоспособности (BIRA), коммутаторы кодов адреса, операций и данных, основной массив запоминающих ячеек, запасные строки и столбцы ячеек, дешифраторы строк и столбцов ячеек [11]. Недостатком данной системы являются ограниченные функциональные возможности, которые вызваны ограниченным числом запасных запоминающих ячеек, что не позволяет восстановить работоспособность при многократных отказах.

Известна также интегральная микросхема, содержащая массив запоминающих ячеек, средства анализа избыточности встроенной памяти, встроенные средства самотестирования и ремонта, которые состоят из контроллера самотестирования, генераторов кодов адреса и данных, мультиплексоров кодов операций, адреса и данных, компаратора, встроенных средств самовосстановления, демультиплексора и регистра регистрации ошибок [12]. Недостатком данной микросхемы является ее ограниченные возможности, не позволяющие выполнить ремонт, если отказы компонентов привели к неработоспособному состоянию одного или нескольких разрядов данных.

Целью работы является разработка архитектуры отказоустойчивого запоминающего устройства за счет применения средств автоматического восстановления работоспособности при многократных отказах компонентов в бортовых системах управления летательными аппаратами и других системах критического применения, для которых необходимо применять отказоустойчивые цифровые устройства.

Для достижения данной цели необходимо решить следующие задачи:

-

– разработать структуру средств встроенного самотестирования и восстановления работоспособного состояния;

-

– разработать структуру блока автоматического восстановления работоспособности запоминающего устройства при многократных отказах ее компонентов;

-

– разработать структуру конфигураторов входных и выходных данных;

-

– разработать структуру микроконтроллера для управления процессом самотестирования и восстановления работоспособности;

-

– разработать программы тестов для выполнения самотестирования микросхем памяти;

– выполнить моделирование запоминающего устройства для проверки возможности автоматического восстановления работоспособности при многократных отказах.

В модулях памяти современных микропроцессорных систем управления в настоящее время широко применяется код Хэмминга ( n , к ) , корректирующий одиночную ошибку и обнаруживающий двойные ошибки. Применение кодов, исправляющих ошибки, требует реализации схем, работающих в реальном масштабе времени.

Пусть в к информационных битах m i , m 2 , .„, mk добавлено r проверочных бит, чтобы сформировать кодовое слово длиной n = к + r . Каждый проверочный бит формируется независимо от остальных проверочных битов и образуется за счет линейной комбинации информационных ресурсов:

С = ha m i Ф h i2 m 2 Ф ... Ф h i k m k ,

С2 = h2imi Ф h22m2 Ф^Ф h2kmk, cr = hr 1 mi Ф hr2m2 Ф ... Ф hrkmk.

Кодовое слово, считанное из памяти n -битным вектором V = ( V i , v 2 , ^ , v n ) , считается правильным если выполняется условие:

HVT = 0, где VT – транспонированный вектор V; H – проверочная матрица. Суммирование выполняется по модулю 2. Проверочная матрица H представляется в виде

H = P I r|, где P — двоичная матрица размерности r x к, а Ir — единичная матрица размерности r x r.

Первые k бит кодового слова представляют собой информационные биты, r – контрольные. Слово, считанное из памяти, может отличаться от записанного слова.

Если U – кодовое слово, записываемое в память компьютера, а V – полученный вектор,

то E = V - U = ( e i ,e 2,..., e n ) называется вектором ошибок. Проверка считанного слова заключается в вычислении синдрома ошибки:

S = HV T = VH T = ( U + E ) ■ H T .

Если S – нулевой вектор, то считается, что ошибок нет. В противном случае синдром определяет вектор ошибки. Синдром является суммой тех столбцов h матрицы H , которым соответствуют ошибки. Если столбец hi нулевой, ошибка в этой позиции кодового слова не окажет влияния на синдром и не позволит обнаружить ошибку. Если два столбца матрицы H совпадают, то одиночные ошибки в каждой из этих позиций кода дают один и тот же синдром.

Схема устройства обнаружения и коррекции ошибок памяти состоит из формирователя контрольных разрядов, буферов данных, формирователя синдрома, дешифратора синдрома и корректора ошибок. К информационным разрядам данных добавляются контрольные разряды, сформированные согласно коду Хэмминга. Данные через первый буфер поступают для записи на входы микросхем памяти. Считаные данные предварительно поступают для контроля на входы формирователя синдрома. Дешифратор синдрома формирует сигнал «Исправимая ошибка», который обычно применяется для запуска обработчика прерываний, фиксирующего количество и интенсивность возникновения одиночных ошибок. Сигнал «Неисправимая ошибка», формируемый дешифратором синдрома, используется для активизации аппаратного прерывания «Ошибка памяти».

С помощью кодов Хэмминга может быть исправлена только однократная ошибка, но работоспособность памяти с несколькими отказами восстановить невозможно.

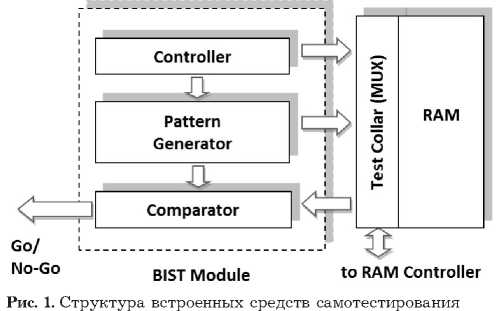

Известна структура встроенных средств самотестирования (Built-in Self diagnosis, BIST)

полупроводниковых запоминающих устройств, приведенная на рис. 1.

Общий подход BIST для микросхем памяти включает внедрение в микросхему дополнительных схем для генерации тестов, синхронизации и сравнения ответных реакций с эталонными данными. Типовая структура микросхемы памяти со встроенными средствами самотестирования содержит контроллер, генератор кодов адреса и данных, компаратор данных и коммутаторы, обеспечивающие подключение к массиву запоминающих ячеек сигналов в рабочем или тестовом режимах [11].

Встроенное самотестирование является методом разработки дополнительных аппаратных и программных средств, которые могут выполнять самотестирование, используя собственные компоненты, чтобы уменьшить зависимость от дорогостоящего внешнего автоматизированного тестового оборудования. Реализация встроенного самотестирования значительно снижает стоимость и повышает процент покрытия неисправностей, так как проверка производится на рабочих частотах и не требуется внешнего тестового оборудования, стоимость которого, как правило, во много раз выше, чем стоимость самих модулей памяти. Тестирование может выполняться за более короткое время, так как есть возможность параллельного тестирования нескольких компонентов изделия [12; 13].

При модификации архитектуры BIST необходимо обеспечить оперативное переключение тестового процесса в нормальный режим работы микросхемы. Степень покрытия возможных отказов должна увеличиваться при увеличении периода эксплуатации микросхемы, при этом аппаратные расходы должны быть как можно меньше, чтобы не увеличивать стоимость реализации новой архитектуры.

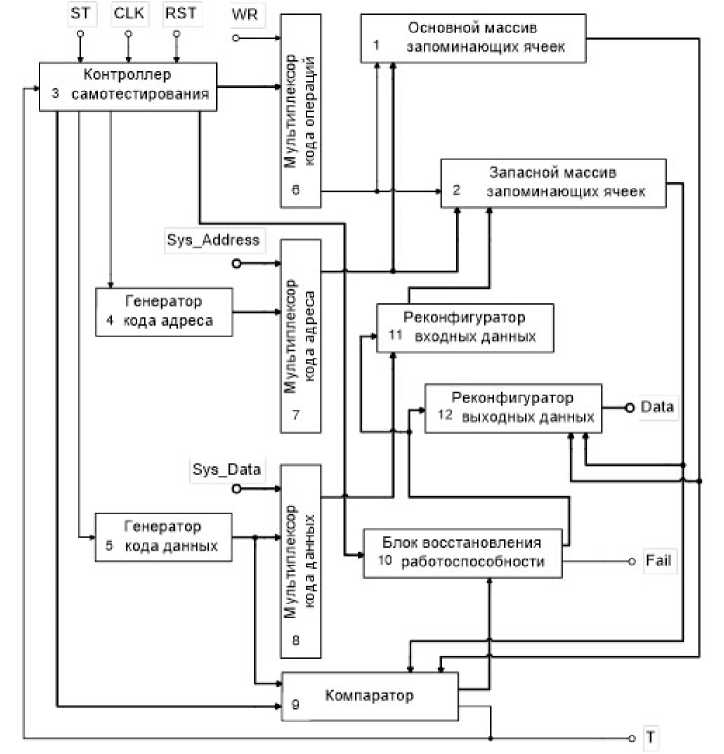

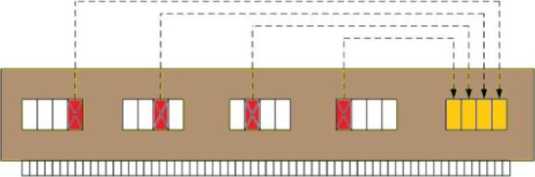

С целью обеспечения восстановления работоспособности запоминающего устройства при многократных отказах ее компонентов в его состав добавлены блок восстановления работоспособности и запасной массив запоминающих ячеек, сформированный в виде нескольких разрядов данных, что позволит записывать, хранить или считывать данные, предназначенные для хранения в одном или нескольких разрядах данных, которые отказали. Структурная схема запоминающего устройства с автоматизированным восстановлением работоспособности при многократных отказах приведена на рис. 2.

Рис. 2. Структурная схема запоминающего устройства с автоматизированным восстановлением работоспособности при многократных отказах

Полупроводниковое запоминающее устройство содержит основной массив запоминающих ячеек, контроллер самотестирования, генераторы кодов адреса и данных, мультиплексоры кодов операций, адреса и данных, компаратор, реконфигураторы входных и выходных данных [14]. На входы контроллера самотестирования от микропроцессора подаются сигнал запуска самотестирования ST, синхросигналы CLK и сигнал установки устройства в исходное состояние RST. Мультиплексоры кодов операций, адреса и данных предназначены для передачи сигналов WR, Sys_Address, Sys_Data в рабочем состоянии устройства и кодов операций, адреса и данных в режиме самотестирования.

Реконфигуратор входных данных обеспечивает переключение данных на входы запасного массива запоминающих ячеек тех разрядов данных, которые отказали в основном массиве запоминающих ячеек. Реконфигуратор выходных данных переключает на выходную шину устройства Data данные с выходов запасного массива запоминающих ячеек вместо отказавших раз- рядов данных основного массива запоминающих ячеек.

Блок восстановления работоспособности запоминающего устройства обеспечивает восстановление работоспособности устройства, если кратность отказов не превышает количества предусмотренных резервных информационных разрядов. Если количество отказавших разрядов данных основного массива запоминающих ячеек больше предусмотренного резерва, то восстановление работоспособности невозможно и на выходе устройства формируется сигнал Fail (неудача).

Разработан встроенный микроконтроллер восстановления работоспособности модулей памяти, который обеспечит самотестирование и автоматическое восстановление работоспособности модулей памяти при многократных отказах ее компонентов.

Запасной массив запоминающих ячеек позволяет записывать, хранить и извлекать данные, предназначенные для хранения в одном или нескольких битах данных, которые отказали в ос-

от блока з

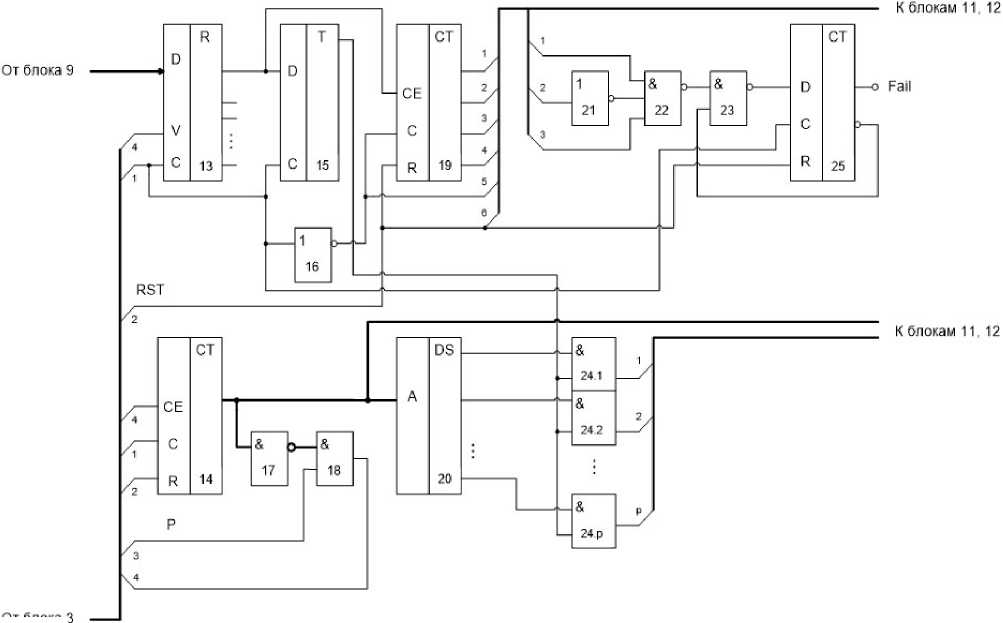

Рис. 3. Структурная схема блока восстановления работоспособности модуля памяти

новном массиве памяти. При обнаружении многократных отказов реконфигурация структуры модуля памяти будет обеспечиваться автоматически за счет добавленных новых аппаратных и программных средств [15–17].

Структура блока восстановления работоспособности показана на рис. 3, которая содержит регистр сдвига 13 , счетчик позиций битов 14 , D-триггер 15 , логические элементы 16 – 18 , 21 – 23 , счетчик числа отказов 19 , дешифратор 20 позиций битов, группу логических элементов 24 .1– 24 .p и D-триггер 25 .

В регистр 13 из компаратора 9 заранее вносится вектор отказов, сформированный после выполнения операции самотестирования устройства. После подачи сигнала Р (Ремонт) регистр 13 переключается в режим сдвига вправо и число отказов запоминается счетчиком 19 . Код позиции каждого бита вектора отказов запоминается счетчиком 14 , дешифруется дешифратором 20 и поступает на входы элементов 24 .1– 24 .p. Состояния счетчика 19 используются для управления работой реконфигуратора входных данных 11 и реконфигуратора выходных данных 12 .

Учитывая большую емкость микросхем памяти, которые выпускаются промышленностью целесообразно тестовые воздействия и эталонные реакции формировать микропрограммным способом [17–20].

Формат микрокоманд и микроопераций встроенного микроконтроллера состоит из следующих полей: кода микрокоманды; поля рабочих микроопераций записи (W), считывания (R), сравнения (А) и ремонта (Р); кода микроопераций адреса; кода микроопераций данных и кода адреса перехода.

Для формирования тестов используются следующие микрокоманды:

NOOP – отсутствие операции, обеспечивает переход к следующей микрокоманде;

JANN – переход к команде, адрес которой записан в поле адреса перехода, если текущий адрес ячейки памяти не равен адресу конечной ячейки;

JANG – переход к команде, адрес которой записан в поле адреса перехода, если текущий адрес ячейки памяти не равен адресу начальной ячейки;

JUMP – безусловный переход к команде, адрес которой записан в поле адреса перехода;

JKNZ – условный переход к команде, адрес которой записан в поле адреса перехода, если при сравнении считанных данных с эталонными значениями обнаружено несовпадение кодов;

STOP – остановка выполнения теста.

Программа теста march_C на языке Prover приведена ниже [18–21].

|

00000 |

NOOP, A:=G, |

T:=0 |

|

00001 |

JANN, 00001, |

W, A:=A+1 |

|

00010 |

A:=G |

|

|

00011 |

r |

|

|

00100 |

a, T:=not T |

|

|

00101 |

JANN, 00011, |

W, A:=A+1, T:=not T |

|

00110 |

A:=G, T:=not |

T |

|

00111 |

r |

|

|

01000 |

a, T:=not T |

|

|

01001 |

JANN, 00111, |

W, A:=A+1, T:=not T |

|

01010 |

A:=N, T:=not |

T |

|

01011 |

r |

|

|

01100 |

a, T:=not T |

|

|

01101 |

JANG, 01011, |

W, A:=A-1, T:=not T |

|

01110 |

A:=N, T:=not |

T |

|

01111 |

r |

|

|

10000 |

a, T:=not T |

|

|

10001 |

JANG, 01111, |

W, A:=A-1,T:=not T |

|

10010 |

A:=G, T:=not |

T |

|

10011 |

r |

|

|

10100 |

a |

|

|

10101 |

JANN, 10011, |

A:=A+1 |

|

10110 |

STOP |

При выполнении теста march_C происходит 10 n циклов обращения к массиву ячеек памяти: 5 n циклов записи и 5 n циклов считывания. По состоянию напряжения на выходе T идентифицируется состояние микросхемы. При наличии высокого уровня напряжения на выходе T работоспособность микросхемы восстановлена, но для более надежной работы системы управления она подлежит замене при проведении профилактических работ.

При проектировании архитектуры отказоустойчивого запоминающего устройства обеспечивается получение высоких диагностических свойств формируемых тестов. При этом уменьшается емкость программ тестов за счет использования аппаратно-микропрограммного способа формирования тестов, который сочетает высокое быстродействие с небольшими аппаратными затратами. Например, продолжительность тестирования запоминающего устройства емкостью 640 Мбит и временем цикла обращения равным 20 нс составляет 1 с.

Модули памяти с ECC коррекцией позволяют обнаружить и восстановить только отказы информационных разрядов, а контрольные разряды не подлежат коррекции. Тогда, например, для 64 информационных разрядов допускается одиночные отказы, а для 8-ми контрольных разрядов нет. В этом случае вероятность безотказ- ной работы модуля с ECC будет равна единице минус сумма вероятностей двойного отказа 64 информационных разрядов и вероятности одиночного отказа одного из 8-ми контрольных разрядов.

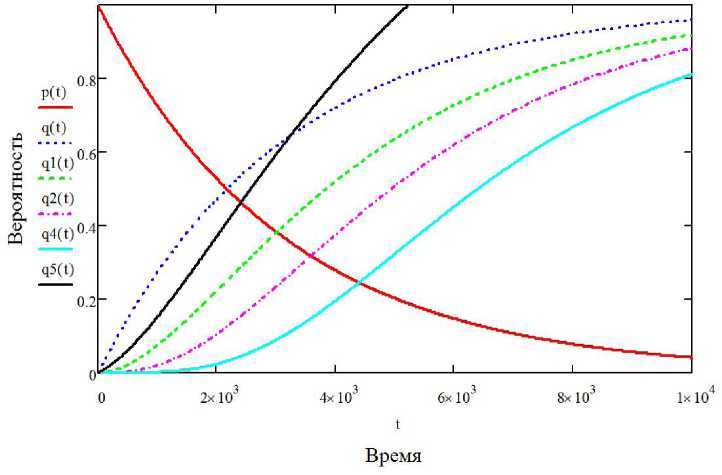

Если интенсивность отказов одного разряда запоминающего устройства X = 1 ■ 10 5 , тогда для устройства, имеющего m inf информационных разрядов, вероятность безотказной работы p ( t ) = e - t X m inf , вероятность отказа q ( t ) = (1 - p ( t )) 1 . Для запоминающего устройства с возможностью выполнения одного ремонта вероятность отказа q 1( t ) = (1 - p ( t )) 2 , для устройств с возможностями выполнения двух, трех и четырех ремонтов вероятности отказов вычисляются по формулам соответственно:

q2(t) = (1 - p(t))3, q3(t) = (1 - p(t))4, q4(t) = (1 - p(t))5.

Графики изменения вероятностей безотказной работы модулей памяти приведены на рис. 4.

На рис. 4 приняты следующие обозначения: q ( t ) – вероятность отказа модуля памяти без использования предложенного метода; q 1( t ), q 2( t ) и q 4( t ) – вероятности отказов при выполнении 1-го, 2-х и 4-х ремонтов; p ( t ) – вероятность исправной работы модуля памяти без ремонта; q 5( t ) – вероятность двойного отказа 64 информационных разрядов и одиночного отказа одного из 8-ми контрольных разрядов модуля памяти.

В результате анализа приведенных выше графиков установлено, что при выполнении четырех автоматических ремонтов после 4 тысяч часов работы вероятность возникновения отказа модуля памяти уменьшается в 3,7 раза по сравнению с модулем, ремонт которого не выполняется.

В настоящее время выполнена разработка VHDL-моделей основных компонентов устройства и проведена верификация проекта [15]. В модель 16-ти разрядного запоминающего устройства добавлено 4 разряда запасного массива запоминающих ячеек. Проведена верификация проекта при ситуации, когда отказали 4, 7, 10 и 13 разряды основного массива запоминающих ячеек, они были автоматически заменены на 1, 2, 3 и 4 разряды запасного массива запоминающих ячеек. Пример замены четырех отказавших разрядов на запасные приведен на рис. 5.

Восстановление работоспособности происхо-

Рис. 4. Графики изменения вероятностей возникновения отказов модуля памяти

Избыточный чип памяти

Рис. 5. Пример замены четырех отказавших разрядов на запасные

дило автоматически по командам встроенного микроконтроллера. Проведенный эксперимент подтвердил способность нового технического решения восстанавливать работоспособность запоминающего устройства при четырехкратных отказах.

Серийно изготавливать запоминающие устройства со встроенными средствами самотестирования и восстановления работоспособности при многократных отказах могут фирмы Apacer Technology Inc, Corsair Memory, IBM, Kingston Technology, Micron Technology и другие. Фирма Apacer входит в пятерку крупнейших в мире производителей модулей памяти, которые по оценкам независимых экспертов являются лучшими по производительности, надежности и ценности для конечного пользователя. Поскольку цифровые данные играют все более важную роль в нашей повседневной жизни, Apacer стремится поставлять на рынок самые новаторские решения. Несмотря на то, что модули памяти присутствуют на рынке уже на протяжении многих лет, Apacer не перестает совершенствовать продукты в данном сегменте. Потребителями отказоустойчивых запоминающих устройств мо- гут быть крупные производители оборудования, ориентированного на рынок промышленного и специального применения, в том числе для авиакосмических систем.

Работа выполнена при финансовой поддержке гранта РФФИ (проект 16-08-00393).

Список литературы Архитектура отказоустойчивого запоминающего устройства для бортовых систем управления летательными аппаратами

- Мишанов Р.О., Пиганов М.Н. Исследовательские испытания интегральных микросхем//Известия Самарского научного центра РАН. 2017. Т. 18. № 4(7). С. 1406-1409.

- Анализ причин низкой надежности и установка диагностического неразрушающегося контроля интегральных стабилизаторов/Р.О. Мишанов //Сборник научных трудов SWorld. 2015. Т. 3. Вып. 1(38). С. 42-48.

- Способ диагностического неразрушающего контроля микросхем КМОП-типа/М.Н. Пиганов //Сборник научных трудов SWorld. 2014. Т. 5. Вып. 3(36). С. 65-72.

- Piganov M.N., Mishanov R.O. Technology of diagnostic for non-destructive control of the bipolar integrated circuits//2nd International scientific symposium «Sense. Enable. SPITSE. 2015»: Symposium Proceedings. St. Petersburg. 2015. P. 38-41.

- Apparatus diagnostic for non-destructive control chip CMOS-type/S.V. Tyulevin //European science and technology: materials of the VIII international research and practice conference. Germany, Munich, 2014. P. 398-401.

- Piganov M., Tyulevin S., Erantseva E. Individual prognosis of quality indicators of space equipment elements//The Experience of Designing and Application of CAD Systems in Microelectronics (CADSM 2015): Proceeding XIII International Conference. Ukraine, Lviv. 2015. P. 367-371.

- Mishanov R., Piganov M. Individual forecasting of quality characteristics by an extrapolation method for the stabilitrons and the integrates circuits//The Experience of Designing and Application of CAD Systems in Microelectronics (CADSM 2015): Proceedings XIII International Conference. Ukraine, Lviv. 2015. P. 242-244.

- Тюлевин С.В., Пиганов М.Н., Еранцева Е.С. К проблеме прогнозирования показателей качества элементов космической аппаратуры//Надежность и качество сложных систем. 2014. № 1(5). C. 9-17.

- Костин А.А., Пиганов М.Н. Расчет помех в цепях бортовой аппаратуры космических аппаратов, вызванных электростатическими разрядами//Известия Самарского научного центра РАН. 2012. Т. 14. № 4(5). С. 1376-1379.

- Костин А.В., Пиганов М.Н., Бозриков В.С. Экспериментальное исследование, измерение и анализ помех в цепях бортовой аппаратуры космических аппаратов, вызванных электромагнитным полем электростатического разряда//Надежность и качество сложных систем. 2015. № 4(16). С. 46-55.

- Patent USA. Redundancy Analysis for Embedded Memories with Built-In Self Test and Built-In Self Repair. N6067262, Int.Cl.G11C 7/00. May 23, 2000.

- Patent USA. Built-In Spare Row and Column Replacement Analysis System for Embedded Memories. N6304989, Int.Cl.G01R 31/28. Oct.16, 2001.

- Utkina T.Yu., Ryabtsev V.G. Method and mean of computer's memory reliable work monitoring//Proceeding of IEEE East-West Design & Test Symposium 2009 (EWDTS'09). (Moscow, 18-21 Sep. 2009). Kharkiv: Khnure, 2009. P. 505-512.

- Architecture of Built-In Self-Test and Recovery Memory Chips/T.Yu. Utkina //Proceedings of East-West Design & Test Workshop (EWDTW'2012). (Kharkov, Ukraine, 14-17 Sep. 2012). Kharkov: Khnure, 2012. Р. 307-310.

- Almadi М.K., Ryabtsev V.G., Utkina T.Yu. Automatic operability restoration of semiconductor memory's modules during multiple faults//European Journal of Engineering and Technology. 2015. Vol. 3. № 5. Р. 72-79.

- Almadi M.K., Ryabtsev V.G. Features of decision support's program at choice of tests optimized sequence for semiconductors memory diagnosing//Radio Electronics & Informatics. 2008. № 1. P. 84-87.

- Almadi M., Moamar D., Ryabtsev V. New methods and tools for design of tests memory//Proceedings of East-West Design & Test Workshop (EWDTW'10). (Sevastopol, 9-12 Sep. 2011). Kharkiv: Khnure, 2011. Р. 319-325.

- Almadi M.K., Ryabtsev V.G. New infrastructure for memory tests design//Proceedings of the International Workshop Critical Infrastructure Safety and Security (CrISS-DESSERT 2011). (Kirovograd, 11-13 May 2011). P. 434-440.

- Almadi M., Moamar D., Ryabtsev V. Methodology of algorithms synthesis of memory test diagnosing//Proceedings of IEEE East-West Design & Test Symposium 2010 (EWDTS'10). (St. Petersburg, 17-20 September 2010). P. 366-370.

- Almadi M.K., Ryabtsev V.G., Kudlaenko V.M. Automation of program's test designing march FD//Management Information System and Devises. 2006. № 136. P. 71-77.

- Ryabtsev V.G., Kudlaenko V.M., Movchan Y.U. Method of estimation diagnostic properties of the test family march//Proceeding of East-West & Test International Workshop (EWDTW'04). (Yalta-Alushta, Criema, 23-26 September 2004). P. 220-224.