Бортовая микропроцессорная система управления с повышенной сбоеустойчивостью

Автор: Удалов Д.В.

Журнал: Сибирский аэрокосмический журнал @vestnik-sibsau

Рубрика: Авиационная и ракетно-космическая техника

Статья в выпуске: 1 т.16, 2015 года.

Бесплатный доступ

Современные инновационные тенденции развития космического приборостроения связаны с применением микропроцессорных технологий в бортовой аппаратуре. Поэтому в состав аппаратуры вводятся микропроцессорные системы управления, осуществляющие непосредственное управление прибором на основании внутренних алгоритмов, что позволяет перейти к распределенному принципу управления, в основе которого лежит идея о локализации функций управления приборами, находящимися на борту, внутри самих приборов. В частности, при создании системы преобразования и управления нового поколения для электрореактивной двигательной установки в АО «НПЦ «Полюс» (г. Томск) разработана бортовая микропроцессорная субсистема обмена и управления, за счет интегрирования которой в указанную систему удалось не только улучшить ее массогабаритные показатели, но и расширить функциональные возможности. Однако рост требований к космическим аппаратам в целом приводит к необходимости совершенствования и систем управления бортовой аппаратурой. Выполнение этих требований невозможно без применения современных интегральных схем со сверхбольшой степенью интеграции, изготовленных по нанометровым технологическим нормам. Как известно, такие схемы, выполненные по субмикронным технологиям, в отличие от микронных обладают более высокой чувствительностью к одиночным эффектам, вызванным воздействием тяжелых заряженных частиц космического пространства, что, в свою очередь, обусловливает необходимость принятия ряда специальных мер по обеспечению стойкости систем управления. Рассмотрены способы повышения сбоеустойчивости микропроцессорных систем управления бортовой аппаратурой космических аппаратов. Показаны пути решения проблем, связанных с выбором электронных компонентов, схемотехнических и архитектурных решений для обеспечения стойкости к одиночным эффектам, вызванным тяжелыми заряженными частицами космического пространства. Предложена к реализации архитектура микропроцессорной системы управления с расширенными функциональными возможностями, высоким быстродействием и повышенной сбоеустойчивостью.

Космический аппарат, бортовая микропроцессорная система, сверхбольшие интегральные схемы, тяжелые заряженные частицы, сбоеустойчивость, одиночные эффекты

Короткий адрес: https://sciup.org/148177397

IDR: 148177397 | УДК: 629.7.05.03

Satellite-borne microprocessor control system with improve upset tolerance

Modern innovative trends in the development of space equipment are associated with the use of microprocessor technology in onboard hardware. Therefore, control systems, direct control of the device based on internal algorithms are introduced as the parts of the equipment microprocessor. That allows you to go to a distributed control principle on board the spacecraft, which is based on the idea of the localization of the control functions on board, inside the devices themselves. In particular, the establishment of a power processing unit of the new generation for electric propulsion system in SC “Scientific&Industrial Centre “Polyus” (Tomsk) developed satellite-borne microprocessor digital interface and control unit, by integrating in which said system is not only able to improve weight and overall dimensions but also to expand functionalities. However, the growth requirements for space vehicles in general leads to the need to improve onboard microprocessor control system.These requirements are not possible without the use of modern integrated circuits with very large-scale integration level produced by nanometer technology standards. It is known that such schemes are made of submicron technology, unlike micron are more sensitive to single effects caused by exposure to heavy charged particles of space, which, in turn, necessitates the adoption of a number of special measures to ensure the stability of control systems. This article discusses the ways to increase upset immunity microprocessor control systems onboard equipment spacecraft. The ways of solving the problems associated with the selection of electronic components, circuit design and architectural solutions for resistance to single effects caused by heavy charged particles of space are shown. We offer to implement the architecture of a microprocessor control system with advanced features, high performance and enhanced upset immunity.

Текст научной статьи Бортовая микропроцессорная система управления с повышенной сбоеустойчивостью

Введение. Современные тенденции развития космического приборостроения связаны с применением микропроцессорных технологий. В частности, при создании системы преобразования и управления (СПУ) нового поколения для электрореактивной двигательной установки [1] в АО «НПЦ «Полюс» (г. Томск) разработана бортовая микропроцессорная субсистема обмена и управления (СОУ) [2], за счет интегрирования которой в СПУ удалось не только улучшить массогабаритные показатели, но и расширить функциональные возможности последней. Основными задачами СОУ являются сбор и первичная обработка телеметрических данных с датчиков, обмен информацией с бортовым вычислительным комплексом и управление электрореактивной двигательной установкой.

Актуальность работ. Рост требований к космическим аппаратам в целом приводит к необходимости совершенствования и систем управления бортовой аппаратурой.

Наиболее актуальными требованиями, предъявляемыми сейчас к интегрируемым микропроцессорным системам управления, являются внедрение современного интерфейса Space Wire, обновление программного обеспечения в процессе эксплуатации, в том числе на орбите, локальная обработка и накопление данных, работа в автоматическом режиме, обеспечение стойкости к тяжелым заряженным частицам, повышение надежности и улучшение массогабаритных характеристик. Выполнение их невозможно без применения современных интегральных схем со сверхбольшой степенью интеграции, изготовленных по нанометровым технологическим нормам. Как известно, такие схемы, выполненные по субмикронным технологиям, в отличие от микронных, обладают более высокой чувствительностью к одиночным эффектам, вызванным воздействием космического излучения [3]. Это, в свою очередь, обусловливает необходимость принятия ряда специальных мер по обеспечению стойкости систем управления к одиночным эффектам.

В настоящее время в АО «НПЦ «Полюс» ведутся работы по созданию микропроцессорной системы управления СОУ-2М с повышенной сбоеустойчиво-стью, что позволит на базе только отечественных электрорадиоизделий производить функционально законченные, высокопроизводительные и стойкие к одиночным эффектам устройства.

Предложенная к реализации архитектура обладает расширенными функциональными возможностями и высоким быстродействием, разрабатывается на основе решений, использованных и опробованных в СОУ. Сравнение основных технических характеристик и примененных методов обеспечения сбоеустойчивости СОУ и СОУ-2М показывает преимущество последней.

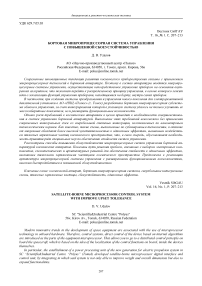

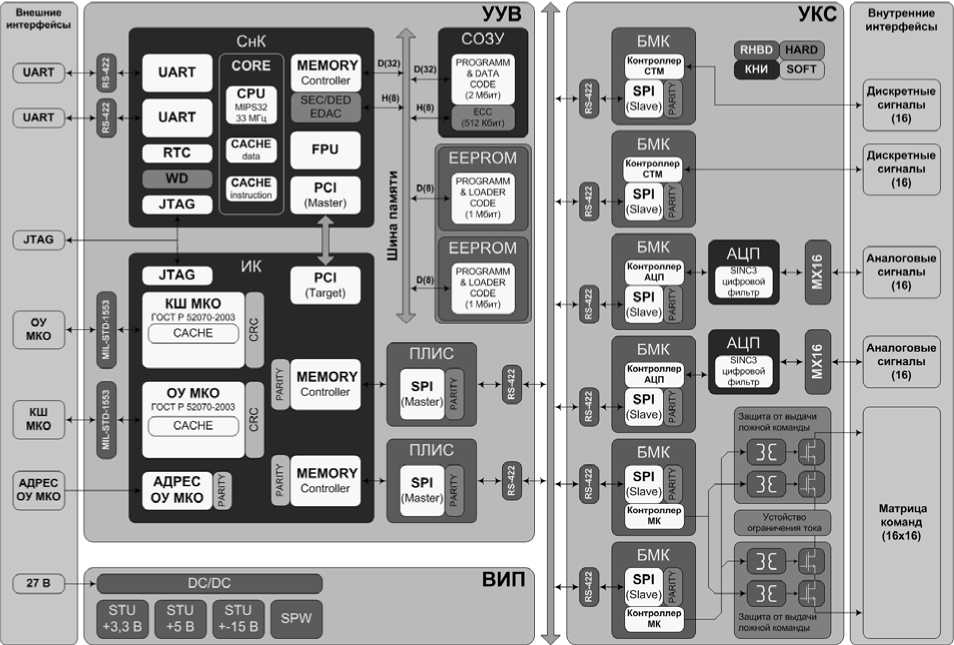

Субсистема обмена и управления СОУ. СОУ построена по двухканальной схеме «ненагруженного резерва» и состоит из двух одинаковых модулей. Выбор активного из них осуществляется подачей на него напряжения питания. Каждый модуль СОУ (рис. 1) состоит из устройства управления и вычисления (УУВ), вторичного источника питания (ВИП), а также устройства коммутации и сопряжения (УКС).

Устройство управления и вычисления СОУ. УУВ (рис. 2) является ядром СОУ и управляет всей системой. Основные сверхбольшие интегральные схемы, входящие в состав УУВ, – система на кристалле (СнК), интерфейсный контроллер (ИК) и программируемые логические интегральные схемы (ПЛИС).

СнК состоит из процессора с архитектурой MIPS32, сопроцессора вещественной арифметики (FPU), контроллера памяти, интерфейсов UART и контроллера шины PCI. Контроллер памяти имеет встроенный контроллер корректирующих кодов (SEC/DED), позволяющий исправлять одиночные и обнаруживать двойные ошибки, вызванные одиночными событиями [4–6].

ИК обеспечивает подключение специализированных устройств к шине PCI. В состав ИК входят два резервированных контроллера мультиплексного канала обмена (МКО) [7] и резервированный контроллер памяти, посредством которого реализовано взаимодействие с ПЛИС [8].

На базе ПЛИС выполнен контроллер резервированного последовательного синхронного интерфейса (SPI) для организации канала связи между УУВ и УКС. Данные, передаваемые по интерфейсу SPI, защищены битом четности.

Вторичный источник питания СОУ. ВИП (рис. 2) обеспечивает гальваническую развязку и формирование вторичных напряжений питания УУВ и УКС по входной бортовой шине «27 В».

HARD контроллер1

SOFT

[(Slave)

Контроллер

JTAG цифровой

Устойство

SPI

[(Slave)

SPI Is

I - ■- л

Контроллер

SPI Е

I J J

Гконтролпер

[Контроллер

Й1

Внутренние интерфейсы

Дискретные сигналы (16)

Аналоговые сигналы (16)

Аналоговые сигналы (16)

Матрица команд (16x16)

Внешние интерфейсы

UART

UART

ВИП

Дискретные сигналы (16)

УУВ

Ё

SPI (Master)

АДРЕС ТЁ ОУ МКО

УКС

Защита от выдачи

Ё MEMORY

< Controller

MEMORY Controller

SPI I (Master) ■

Контроллер

SINC3 цифровой

Защита от выдачи ложной команды

CPU MIPS32 33 МГц

RTC

FPU

(1 Мбит)

(1 Мбит)

Г SPI К

UART

UART

MEMORY

Controller

SEC/DED EDAC

D<32)

WD

JTAG

PCI (Master)

D<32)

(512 Кбит)

( CACHE ) 8

JTAG

КШ MKO

ГОСТ P 52070-2003

( CACHE )

ОУ MKO ГОСТ P 52070-2003

PCI (Target)

АДРЕС

ОУ MKO

КШ MKO

ОУ

MKO "

БМК

ChK

CORE I

СОЗУ

RHBD ► <

КНИ

БМК

EEPROM

EEPROM

БМК

АЦП

АЦП

БМК

ПЛИС

ПЛИС

БМК

БМК

DC/DC

STU *3,3 8

STU +5 В

STU +-15B

SPW

Рис. 1. Структурно-функциональная схема СОУ

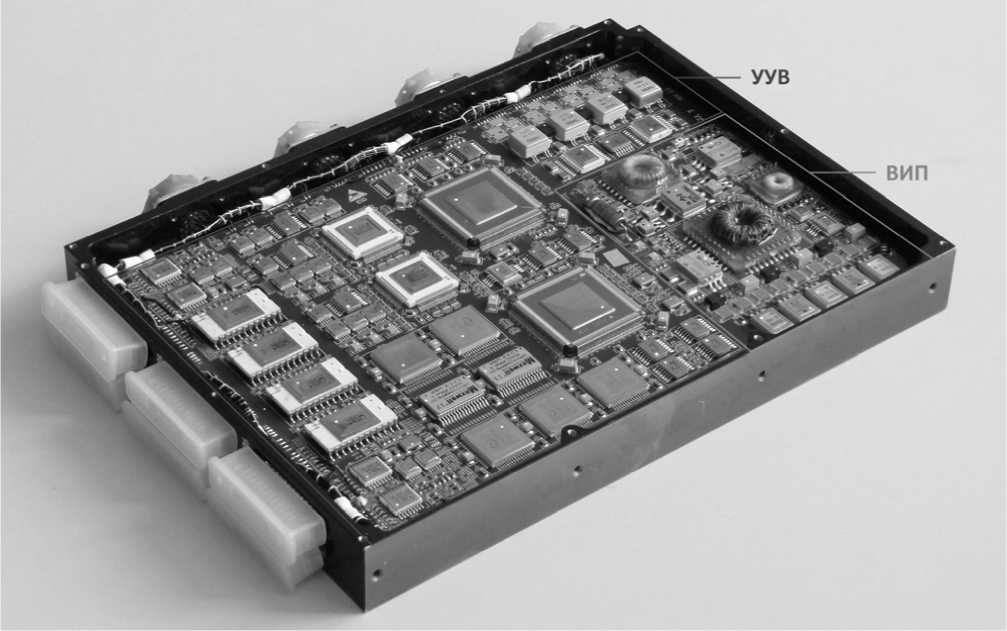

Устройство коммутации и сопряжения СОУ. УКС (рис. 3) является устройством сопряжения УУВ с датчиками и объектами управления СПУ. Основные функции, выполняемые УКС, – сбор и обработка информации с аналоговых и сигнальных датчиков, а также формирование матричных команд управления силовыми устройствами СПУ.

Для выполнения указанных функций в УКС введены соответствующие контроллеры, реализованные на базовых матричных кристаллах (БМК) и подключенные к сетевому интерфейсу SPI.

Контроллер аналоговой телеметрии (АТМ) состоит из двух независимых каналов измерения, работающих синхронно. Результаты синхронных измерений можно использовать для вычисления мгновенной мощности. Каждый канал представляет собой мультиплексированную систему сбора информации, которая состоит из мультиплексора 16×1, 24-разрядного ∑∆–АЦП, аппаратного цифрового фильтра и устройства системной калибровки. Каждый канал обрабатывает 16 аналоговых сигналов.

Контроллер сигнальной телеметрии (СТМ) осуществляет сбор сигнальной телеметрии и также имеет два независимых канала измерения дискретных сигналов, работающих синхронно. Каждый канал снимает показания с 16 сигнальных датчиков и осуществляет программную цифровую фильтрацию собранных данных. Каждый из датчиков может быть типа «неза-питанный контакт» или «открытый коллектор».

Контроллер матричных команд (МК) формирует сигналы управления матрицей команд 16×16 (256 матричных команд), которая подключена к бортовой шине питания «27 В». Ток коммутации каждого ключа матрицы составляет 2 А.

На программно-аппаратном уровне СОУ обеспечивает невыдачу ложной команды в случае отказа или одиночного сбоя как в силовом ключе, так и в цепях управления. Каждый ключ матрицы команд резервирован от короткого замыкания. Длительность матричных команд задается программно и может варьироваться от 50 до 250 мс. Сторожевой таймер контроллера МК аппаратно ограничивает длительность матричной команды на уровне 250 мс в случае сбоя или неисправности. Трансформаторы обеспечивают гальваническую развязку цепей управления от силовых цепей и объектов управления.

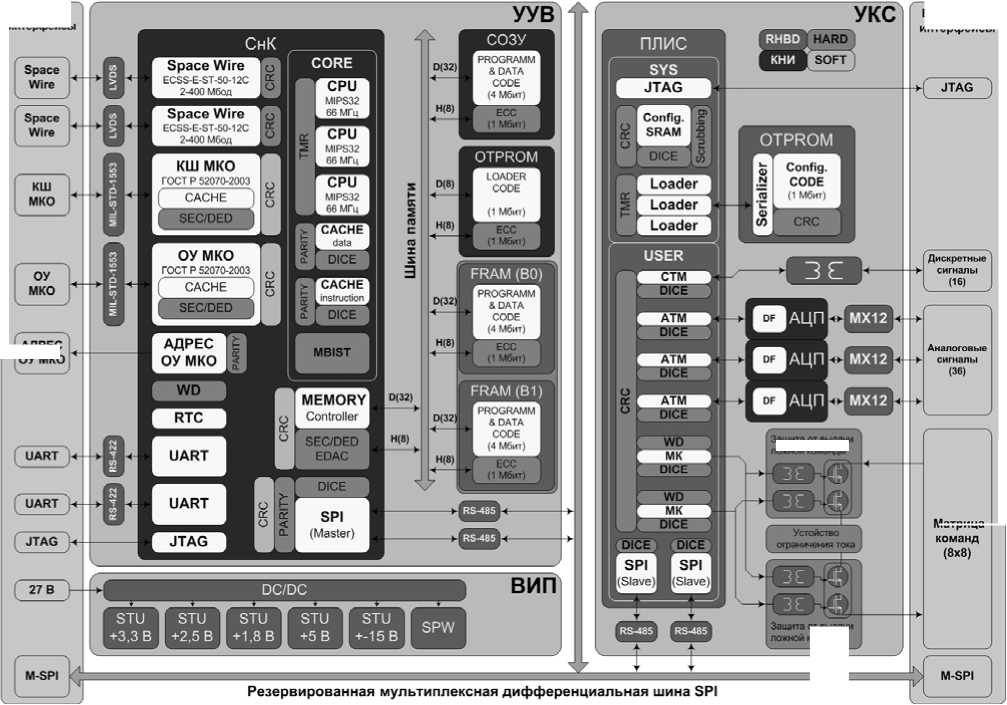

Субсистема обмена и управления СОУ-2М. СОУ-2М (рис. 4) унаследовала свой структурный состав от СОУ. Она также построена по двухканальной схеме «ненагруженного резерва» и состоит из двух одинаковых модулей. Выбор активного из них осуществляется подачей на него напряжения питания. Каждый модуль СОУ-2М состоит из устройства управления и вычисления, вторичного источника питания и устройства коммутации и сопряжения.

Устройство управления и вычисления СОУ-2М. УУВ СОУ-2М построено на базе модифицированной СнК, в которой был реализован целый ряд мер по парированию одиночных сбоев. Так, используется троированное микропроцессорное ядро с архитектурой MIPS32 и тактовой частотой 66 МГц, контроллер памяти с контроллером корректирующих кодов (SEC/DED) [9], кэш-инструкций и данных, реализованный на DICE-ячейках (Dual Inter-locked Storage Cell) с контролем четности, все регистры процессора также реализованы на DICE-ячейках [10; 11].

Рис. 2. Внешний вид УУВ и ВИП

Рис. 3. Внешний вид УКС

В состав СнК также входят два резервированных контроллера МКО, соответствующие ГОСТ Р 52070–2003 [7], два контроллера Space Wire, соответствующие стандарту ECSS-E-ST-50-12C [12], два контроллера UART, контроллер интерфейса SPI [13; 14] и сопроцессор вещественной арифметики FPU.

Для обеспечения толерантности к тиристорному эффекту кристалл СнК выполнен по технологии «кремний на изоляторе» (КНИ) с проектными нормами 240 нм [15].

В состав УУВ СОУ-2М входит статическое запоминающее устройство (СОЗУ) с объемом 4 Мбита для данных и 1 Мбит для корректирующих кодов [9; 16]. СОЗУ также выполнено по технологии КНИ с проектными нормами 240 нм.

В качестве загрузочного используется однократно программируемое постоянное запоминающее устройство (ПЗУ) с ячейками antifuse. Объем его составляет 1 Мбит для данных и 1 Мбит для корректирующих кодов. Загрузочное ПЗУ выполнено по технологии КНИ с проектными нормами 180 нм.

В состав УУВ СОУ-2М входит энергонезависимое постоянное запоминающее устройство (ЭПЗУ) типа F-RAM, разбитое на два независимых банка, каждый из которых имеет объем 4 Мбита для данных и 1 Мбит для корректирующих кодов. В ЭПЗУ записано системное программное обеспечение, которое можно обновить по каналу МКО или Space Wire в процессе эксплуатации на орбите.

Вторичный источник питания СОУ-2М. ВИП СОУ-2М обеспечивает гальваническую развязку и формирование вторичных напряжений питания УУВ и УКС по входной бортовой шине «27 В».

Устройство коммутации и сопряжения СОУ-2М. В УКС СОУ-2М для повышения сбоеустойчивости были модифицированы интерфейс связи с УУВ и контроллеры устройств сопряжения. Для реализации их функций вместо БМК используется сбоеустойчивая ПЛИС с логической емкостью 50 тыс. вентилей. Данная ПЛИС выполнена на объемном кремнии с проектными нормами 180 нм. Для обеспечения стойкости к одиночным событиям все триггеры и элементы памяти в ПЛИС реализованы на DICE-ячейках. Кроме того, в рабочем режиме ПЛИС проводит верификацию конфигурационной памяти и в случае ошибки автоматически выполняет реконфигурацию.

В качестве конфигурационного ПЗУ используется однократно программируемое ПЗУ с ячейками antifuse. Объем конфигурационного ПЗУ составляет 1 Мбит.

Для обеспечения стойкости к одиночным событиям все функциональные узлы, выполненные на ПЛИС, резервированы.

Используемые методы обеспечения сбоеустойчи-вости и основные технические характеристики СОУ и СОУ-2М приведены в таблице.

Внешние интерфейсы

Внутренние интерфейсы

Матрица зашита от выдачи команды

Рис. 4. Структурно-функциональная схема СОУ-2М

АДРЕС

ОУ МКО

защита от выдачи

ПОЖИОЙ КОМАНДЫ

Сравнение основных характеристик и применяемых методов повышения сбоеустойчивости СОУ и СОУ-2М

|

Параметр |

СОУ \ |

СОУ-2М |

|

Общие |

||

|

Год разработки |

2012 |

2014 |

|

Габариты и масса (один канал) |

270×195×30 мм, 1,2 кг |

265×195×20 мм, 0,9 кг |

|

Питание |

23–31 В (6 Вт) |

23–31 В (6 Вт) |

|

ЭРИ иностранного производства |

28LV010RPFS-20 |

Отсутствуют |

|

Процессор |

||

|

Реализация |

5890ВЕ1Т |

«Обработка-10» |

|

Архитектура |

КОМДИВ (MIPS32) |

КОМДИВ (MIPS32) |

|

Производительность |

22 MIPS |

53 MIPS |

|

Методы снижения сбоев |

КНИ |

КНИ, TMR, PARITY, DICE |

|

Системное ОЗУ |

||

|

Тип |

SRAM |

SRAM |

|

Объем |

2 Мбит (64К×32+ECC) |

4 Мбит (128К×32+ECC) |

|

Методы снижения сбоев |

КНИ, SEC/DED |

КНИ, SEC/DED |

|

Загрузочное ПЗУ |

||

|

Тип |

EEPROM |

ANTIFUSE |

|

Объем |

2×256 Кбит (2×32К×8) |

1 Мбит (128К×8+ECC) |

|

Перезапись при эксплуатации |

Да |

Нет |

|

Методы снижения сбоев |

DOUBLE, CRC |

КНИ, SEC/DED, CRC |

|

Системное ПЗУ |

||

|

Тип |

EEPROM |

FRAM |

|

Объем |

1536 Кбит (192К×8) |

2×4 Мбит (2×128К×32+ECC) |

|

Перезапись при эксплуатации |

Да |

Да |

|

Методы снижения сбоев |

CRC |

DOUBLE, SEC/DED, CRC |

|

Внешние интерфейсы |

||

|

Реализация |

5890ВГ1Т |

«Обработка-10» |

|

МКО (ГОСТ Р 52070–2003) |

2 (ОУ, КШ, МШ) |

1 (ОУ), 1 (КШ, МШ) |

|

Space Wire (ECSS-E-ST-50-12C) |

Нет |

2 (2–400 Мбод) |

|

Методы снижения сбоев |

КНИ, CRC |

КНИ, SEC/DED, CRC |

|

Отладочные интерфейсы |

||

|

UART (RS-422) |

2 (115 Кбод) |

2 (115 Кбод) |

|

JTAG (IEEE 1149.1) |

2 (СНК и ПЛИС) |

2 (СНК и ПЛИС) |

|

Межблочный интерфейс |

||

|

Реализация |

2×5576ХС2Т (ПЛИС) |

«Алмаз-2» (ПЛИС) |

|

Протокольный уровень |

Дублированный SPI |

Резервированный SPI |

|

Физический уровень |

2×4×RS-422 (1 Мбод) |

2×4×RS-485 (10 Мбод) |

|

Методы снижения сбоев |

DOUBLE, PARITY |

REDUNDANCY, TMR, DICE, CRC |

|

Аналоговый интерфейс |

||

|

Аналоговые входы |

4×8 (13 бит) |

3×12 (16 бит) |

|

Цифровая фильтрация |

4×SINC3 |

3×SINC3 |

|

Методы снижения сбоев |

КНИ |

КНИ, DICE, CRC |

|

Сигнальный интерфейс |

||

|

Сигнальные входы |

2×16 («НК», «ОК») |

2×8 («НК», «ОК») |

|

Гальваническая развязка |

Нет |

Да (250 В) |

|

Методы снижения сбоев |

PARITY |

DICE, CRC |

|

Матричные команды |

||

|

Матричные выходы |

16×16 (2 А, 27В) |

8×8 (2 А, 27 В) |

|

Ограничение тока |

Да (2 А) |

Да (2 А) |

|

Гальваническая развязка |

Да (250 В) |

Да (250 В) |

|

Методы снижения сбоев |

REDUNDANCY, PARITY, WD |

REDUNDANCY, DICE, WD, CRC |

Заключение. Использование оригинальных архитектурных решений, методов парирования сбоев, а также перспективных ЭРИ отечественного производства позволило разработать микропроцессорную систему управления с повышенной устойчивостью к внешним воздействующим факторам космического пространства.

Список литературы Бортовая микропроцессорная система управления с повышенной сбоеустойчивостью

- Ермошкин Ю. М. Основы теории и расчета электрореактивных двигательных установок: учеб. пособ./Сиб. гос. аэрокосмич. ун-т. Красноярск. 2003. 159 c

- Удалов Д. В., Пухтий С. Б., Седнев Ю. С. Бортовая микропроцессорная субсистема управления для электрореактивной двигательной установки//Электронные и электромеханические системы и устройства: сб. науч. тр./ОАО «НПЦ «Полюс». Томск, 2011. С. 139-147

- Santarini M. Cosmic radiation comes to ASIC and SOC design. EDN. 5/12/2005 . URL: http://edn.com/article/CA529381.html (дата обращения: 20.12.2013)

- Филипчук Е. В., Пахомов С. И. Теория информации и помехоустойчивое кодирование. М.: МИФИ, 1989. 118 c

- Hsiao M. Y. A Class of Optimal Minimum Odd-Weight-Column SEC-DED Codes//IBM J. Res. Develop. 1970. Т. 14. P. 395-401

- Хемминг Р. В. Численные методы. М.: Наука, 1972. 400 c

- ГОСТ Р 52070-2003. Интерфейс магистральный последовательный системы электронных модулей. М.: Госстандарт России, 2003

- ПЛИС для космических применений. Архитектурные и схемотехнические особенности/В. Телец //Электроника: наука, технология, бизнес. 2005. № 6. C. 44-48

- Краснюк А. А., Петров К. А. Особенности применения помехоустойчивого кодирования в СУБ-100 на микросхемах памяти для космических систем//Микроэлектроника. 2012. Т. 41, № 6. С. 450-456

- Юдинцев В. Радиационно стойкие интегральные схемы. Надежность в космосе и на земле//Электроника: наука, технология, бизнес. 2007. № 5. C. 72-77

- Mayer D. C., Lacoe R. C. Designing Integrated Circuits to Withstand Space Radiation Vol. 4, № 2. URL: http://aero.org/publications/crosslink/summer2003/06.html (дата обращения: 20.05.2014)

- ECSS-E-50-12C. SpaceWire -Links, nodes, routers and networks. European Cooperation for Space Standardization (ECSS), 2008

- SPI Block Guide V03.06, FreeScale Semiconductor . URL: http://freescale.com/files/microcontrollers/doc/ref_manual/S12SPIV3.pdf (дата обращения: 20.05.2014)

- MICROWIRE™ Serial Interface. National Semiconductor Application Note 452, Abdul Aleaf, Jan. 1992 . URL: http://national.com/an/AN/AN-452.pdf (дата обращения: 20.05.2014)

- Romanko Th., Clegg B. SOI eases radiation-hardened ASIC design . URL: http://eetimes.com/showArticle.jhtml?articleID=165700727 (дата обращения: 20.05.2014)

- Calin T., Nicolaidis M., Velazco R. Upset hardened memory design for submicron CMOS technology//IEEE Transactions on Nuclear Science. 1996. Vol. 43(6). P. 2874-2878