Исследование нагрузочной способности микросхем

Автор: Еранцева Е.С., Шопин Г.П., Пиганов М.Н., Андрусенко В.С.

Журнал: Физика волновых процессов и радиотехнические системы @journal-pwp

Статья в выпуске: 3 т.23, 2020 года.

Бесплатный доступ

В статье авторы предложили новое устройство для определения нагрузочной способности микросхем. Устройство для определения нагрузочной способности микросхем относится к области микроминиатюризации и технологии радиоэлектронной аппаратуры и может быть использовано для контроля параметров микросхем при их производстве. Устройство содержит генератор прямоугольного напряжения, испытуемую микросхему, повторитель, элементы нагрузки, коммутатор, элемент И, компаратор, счетчик импульсов, источник опорного напряжения, одновибратор, реверсивный счетчик импульсов, дешифратор, индикатор. Техническим результатом при реализации заявленного решения являются повышение точности и достоверность определения нагрузочной способности микросхем; преимуществами устройства по сравнению с известными - возможность работы с микросхемами серий ТТЛ, ТТЛШ и МОП, определение нагрузочной способности микросхем в двух режимах работы без изменения состава его блоков, обеспечение автоматического режима работы и адаптированность к смене испытуемых микросхем и элементов нагрузки 8-1…8-k.

Нагрузочная способность, интегральная микросхема, устройство определения, режим работы, точность, достоверность, контроль

Короткий адрес: https://sciup.org/140256321

IDR: 140256321 | УДК: 621.382+621.317.799 | DOI: 10.18469/1810-3189.2020.23.3.74-81

Research the load capacity of microcircuits

The device for the definition of the integrated circuits load-driving capability is offered. Device for determining the output capability of microcircuits refers to the field of microminiaturization and the technology of radio electronic equipment and can be used to control the parameters of microcircuits during their production. The device contains a rectangular pulse generator, an integrated circuit that is being tested, a repeater, load, a switch, an AND gate, a comparator, a pulse counter and a voltage reference, a vibrator, a reversible pulse counter, a decoder, and an indicator. Technical result when implementing the disclosed solution is high accuracy and reliability of determining load capacity of microcircuits. The proposed device allows increasing accuracy and reliability of defining circuit’s load-driving capacity. It also allows testing of TTL, Schottky-TTL, and MOSFET circuits. There are two switchable operating modes for testing fan-out for logical high and low levels. It is easy to replace a circuit that is being tested and load.

Текст научной статьи Исследование нагрузочной способности микросхем

Конкурентоспособность выпускаемых отечественной промышленностью изделий микроэлектроники на данном этапе определяется в первую очередь их качеством. В последние годы уделяется большое внимание разработке систем управления качеством, которые обеспечивают требуемый уровень качества изделий при минимальных затратах. Важным звеном этой системы является подсистема контроля качества. Сложившаяся практика контроля качества изделий микроэлектроники, в первую очередь интегральных микросхем (ИМС) и микросборок (МСБ), не удовлетворяет возрастающим требованиям. Быстрый рост функциональной сложности ИМС и МСБ, расширение областей их применения делают проблему обеспечения требуемого уровня качества особо актуальной [1].

Наибольшее распространение в бортовой РЭА получили цифровые интегральные микросхемы. Они имеют большую номенклатуру параметров, которые определяют надежность и эффективность функционирования аппаратуры [2–11].

Важнейшим параметром цифровых микросхем является нагрузочная способность как параметр выхода микросхемы, характеризуемый быстродействием и выходным током драйвера, определяющим количество подключаемых входов микросхем.

1. Анализ вариантов известных устройств

В работе [12] предложен вариант устройства, которое позволяет повысить точность определения нагрузочной способности микросхем.

Устройство содержит генератор прямоугольного напряжения, испытуемую микросхему, вольтметр, элементы нагрузки, коммутатор, элемент И, компаратор, счетчик импульсов, источник опорного напряжения.

Для повышения достоверности определения нагрузочной способности микросхем было разработано более совершенное устройств [13].

Это устройство содержит генератор прямоугольного напряжения, испытуемую микросхему, рабочую микросхему, вольтметр, элементы нагрузки, коммутатор, элемент И, компаратор, счетчик импульсов, источник опорного напряжения.

Особенности физических процессов при контроле нагрузочной способности рассмотрены в [14].

Однако достоверность определения нагрузочной способности микросхем в ряде случаев не удовлетворяет разработчиков аппаратуры.

Целями работы являются повышение точности и достоверности определения нагрузочной способности цифровых микросхем и упрощение устройства контроля.

2. Разработка устройства контроля

Для повышения точности и достоверности контроля и упрощения конструкции было разработа-

[м^^е © Еранцева Е.С. и др., 2020

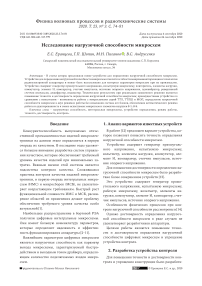

Рис. 1. Устройство для определения нагрузочной способности микросхем

Fig. 1. Device for determining the load capacity of microcircuits

но устройство, блок-схема которого приведена на рис. 1.

Устройство содержит источник опорного напряжения 1 , генератор прямоугольного напряжения 2 , испытуемую микросхему 3 , повторитель 4 , компаратор 5 , элемент И 6 , одновибратор 7 , элементы нагрузки 8 -1… 8 -k, коммутатор 9 , реверсивный счетчик импульсов 10 , дешифратор 11 и индикатор 12 .

В устройстве последовательно соединены генератор прямоугольного напряжения 2 и элемент И 6 , а также источник опорного напряжения 1 и компаратор 5 , выход которого подключен к управляющему входу источника опорного напряжения 1 и ко второму входу элемента И 6 .

Вход повторителя 4 и сигнальный вход коммутатора 9 объединены и подключены к выходной клемме испытуемой микросхемы 3 . Выход повторителя 4 связан со вторым входом компаратора 5 .

Вход одновибратора 7 подключен также к выходу компаратора 5 , а выход – к вычитающему входу реверсивного счетчика импульсов 10 , суммирующий вход которого подключен к выходу элемента И 6 .

Каждый из выходов реверсивного счетчика импульсов 10 подключен к одноименным входам коммутатора 9 и дешифратора 11. Каждый из выходов коммутатора 9 подключен к входу одно- именного элемента нагрузки 8-1…8-k. Каждый из выходов дешифратора 11 подключен к одноименному входу индикатора 12.

Устройство позволяет определять нагрузочную способность испытуемой микросхемы 3 по изменению высокого уровня (первый режим) и по изменению низкого уровня (второй режим) ее выходного сигнала.

3. Принцип работы устройства

В соответствии с первым режимом устройство работает следующим образом. Выходное напряжение испытуемой микросхемы 3 поступает на вход повторителя 4 и сигнальный вход коммутатора 9 . Последний первоначально находится в состоянии, когда элементы нагрузки 8 -1… 8 -k отключены от выхода испытуемой микросхемы 3 . Компаратор 5 сравнивает выходное напряжение повторителя 4 (оно практически совпадает с выходным напряжением испытуемой микросхемы 3 ) с выходным напряжением источника опорного напряжения 1 . Последнее совпадает с минимально допустимым значением напряжения высокого уровня (логической «1») выходного сигнала испытуемой микросхемы 3 . На выходе компаратора 5 формируется логическая «1», если первое из сравниваемых напряжений превышает второе, в противном случае – логический «0».

В случае использования исправной испытуемой микросхемы 3 при первоначальном состоянии коммутатора 9 выходное напряжение повторителя 4 превышает напряжение источника опорного напряжения 1 и на выходе компаратора 5 формируется логическая «1». Она поступает на второй вход элемента И 6 , разрешая прохождение с его первого входа на выход импульсов высокого уровня генератора прямоугольного напряжения 2 . Выходные импульсы элемента И 6 поступают на вход реверсивного счётчика импульсов 10 . На его выходах формируются цифровые сигналы, код которых несет информацию о числе этих импульсов. «Вес» каждого разряда реверсивного счетчика импульсов 10 , начиная со второго, в два раза выше предыдущего. Сигнал с каждого из выходов реверсивного счётчика импульсов 10 поступает на одноимённый вход коммутатора 9 .

Коммутатор 9 , в соответствии с меняющимся кодом его входных сигналов, подключает элементы нагрузки 8 -1... 8 -k к выходу испытуемой микросхемы 3 , равномерно наращивая нагрузку. «Весовые» соотношения элементов нагрузки 8 -1... 8 -k совпадают с «весовыми» соотношениями одноименных разрядов реверсивного счетчика импульсов 10 .

При этом с каждым новым переключением коммутатора 9 значение напряжения высокого уровня выходного сигнала испытуемой микросхемы 3 в связи с уменьшением сопротивления нагрузки (и возрастанием ее тока) уменьшается. До тех пор, пока это напряжение остается больше выходного напряжения источника опорного напряжения 1 (в течение всех рабочих циклов), на выходе компаратора 5 сохраняется логическая «1», поддерживающая процесс вычисления нагрузочной способности.

В противном случае на выходе компаратора 5 формируется логический «0», свидетельствующий о том, что значение выходного напряжения исследуемой микросхемы 3 вышло за пределы нормы и значение нагрузочной способности, зафиксированное реверсивным счетчиком импульсов 10 в последнем рабочем цикле, должно быть уменьшено на единицу. Для выполнения этого с выхода компаратора 5 на управляющий вход источника опорного напряжения 1 и вход одновибратора 7 поступает логический перепад с высокого уровня («1») на низкий («0»).

При этом выходное напряжение источника опорного напряжения 1 возрастает и фиксируется на большем (от первоначального значения) уровне.

Его значение зависит от типа логики испытуемой микросхемы.

Это исключает в дальнейшем повторное (ложное) поступление импульса на вход реверсивного счетчика импульсов 10 в последнем рабочем цикле.

Одновременно с этим на выходе одновибратора 7 формируется импульс высокого уровня. Он поступает на инвертирующий вход реверсивного счетчика импульсов 10 , уменьшая записанное в нем число на единицу.

Реверсивный счетчик импульсов 10 формирует код, который дешифратор 11 преобразует во входной код индикатора 12 , производя тем самым запись числа n1, определяющего нагрузочную способность по первому режиму.

Для обеспечения второго режима работы устройства, позволяющего определять нагрузочную способность испытуемой микросхемы 3 по изменению низкого уровня ее выходного сигнала, необходимо:

- первый вход компаратора 5 подключить к выходу повторителя 4, а второй вход - к выходу источника опорного напряжения 1;

– значение выходного напряжения источника опорного напряжения 1 установить равным максимально допустимому значению напряжения низкого уровня (логического «0») выходного сигнала испытуемой микросхемы 3.

4. Исследование нагрузочной способности

При этом с каждым новым переключением коммутатора 9 значение напряжения низкого уровня выходного сигнала испытуемой микросхемы 3 увеличивается. До тех пор пока это напряжение остается меньше выходного напряжения источника опорного напряжения 1 (в течение всех рабочих циклов), сохраняется процесс вычисления нагрузочной способности. Также выполняется ее коррекция на единицу. Выходное напряжение источника опорного напряжения 1 при этом убывает и фиксируется на меньшем (от первоначального значения) уровне.

Индикатор 12 отображает число n2, определяющее нагрузочную способность по второму режиму. В остальном работа всех блоков устройства в обоих режимах одинакова [15].

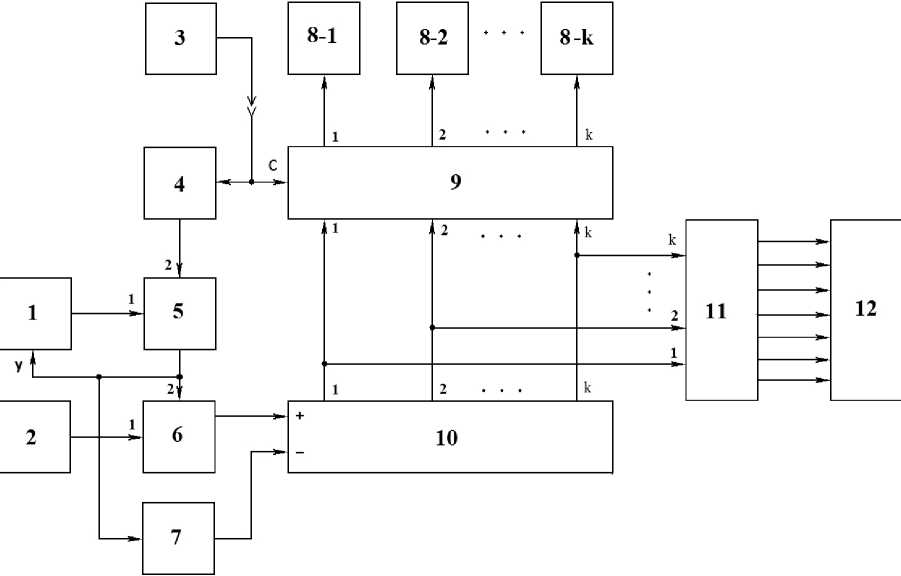

Для исследования нагрузочной способности микросхем были использованы микросхемы с ТТЛ-логикой. Схема подключения нагрузок к исследуемой микросхеме приведена на рис. 2.

Рис. 2. Схема подключения нагрузок к исследуемой микросхеме

Fig. 2. Scheme of connecting loads to the investigated microcircuit

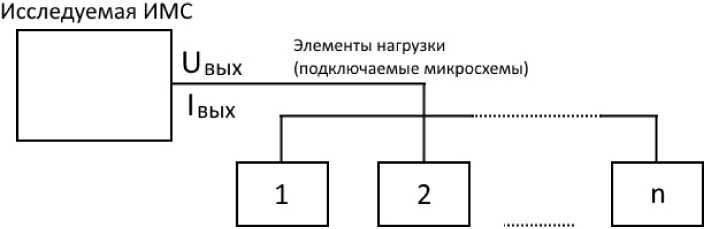

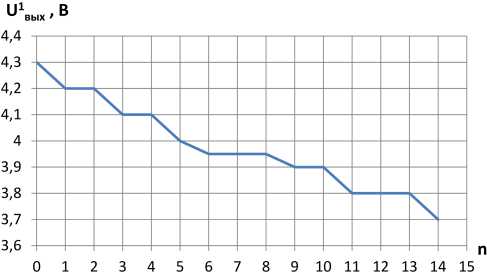

Рис. 3. Зависимость выходного напряжения высокого уровня от числа нагрузок

Fig. 3. Dependence of the high-level output voltage on the number of loads

Рис. 5. Зависимость выходного тока низкого уровня от числа нагрузок

Fig. 5. Dependence of the low-level output current on the number of loads

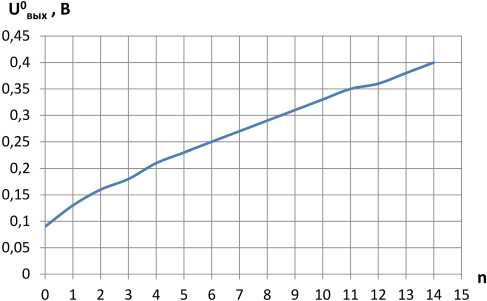

Рис. 4. Зависимость выходного напряжения низкого уровня от числа нагрузок

Fig. 4. Dependence of the low-level output voltage on the number of loads

Рис. 6. Зависимость выходного тока высокого уровня от числа нагрузок

Fig. 6. Dependence of the high-level output current on the number of loads

Влияние числа подключенных нагрузок n на выходное напряжение высокого уровня (уровень логической «1») микросхемы К155ЛИ1 приведено на рис. 3. С ростом n напряжение U 1 падает. Напряжение низкого уровня (уровень логического «0») возрастает (рис. 4). Зависимости I 0 вых и I 1 вых от числа нагрузок приведены на рис. 5 и 6.

Для сравнения на рис. 7 и 8 показаны зависимости U 1 вых и U 0 вых микросхемы К555ЛЕ1 от числа подключенных нагрузок n .

Установлено, что с увеличением числа нагрузок возрастает температура корпуса микросхемы (табл.).

Проведенные исследования показали, что при контроле нагрузочной способности испытуемой цифровой ИМС необходимо учитывать не только число входов элементов нагрузки, подключенных к ее выходу, но и величину предельного выходного тока. С увеличением числа подключенных входов элементов нагрузки возрастает выходной ток микросхемы. Он не должен сильно приближаться к значению выходного тока короткого замыкания испытуемой микросхемы. При этом предполагается, что при подключении элементов нагрузки уровень логической «1» не опускается ниже определенного высокого уровня, а уровень логического «0» не превышает определенный низкий уровень.

Рис. 7. Зависимость выходного напряжения высокого уровня микросхемы К555ЛЕ1 от числа нагрузок

Fig. 7. Dependence of the high-level output voltage of the K555LE1 microcircuit on the number of loads

Рис. 8. Зависимость выходного напряжения низкого уровня микросхемы К555ЛЕ1 от числа нагрузок

Fig. 8. Dependence of the low level output voltage of the K555LE1 microcircuit on the number of loads

Табл. Влияние числа нагрузок n на температуру корпуса при f = 1 кГц и t с = 25 C

Table. Influence of the number of loads n on the case temperature at f = 1 kHz and t с = 25 C

|

n |

U 0 |

U 1 |

t k , C |

n |

U 0 |

U 1 |

t k , C |

|

0 |

0,05 |

3,79 |

25 |

18 |

0,225 |

3,57 |

30 |

|

1 |

0,06 |

3,73 |

25 |

19 |

0,23 |

3,57 |

31 |

|

2 |

0,075 |

3,69 |

25 |

20 |

0,24 |

3,55 |

32 |

|

3 |

0,085 |

3,67 |

26 |

21 |

0,245 |

3,54 |

33 |

|

4 |

0,095 |

3,65 |

26 |

22 |

0,255 |

3,53 |

34 |

|

5 |

0,105 |

3,63 |

26 |

23 |

0,26 |

3,52 |

34 |

|

6 |

0,120 |

3,63 |

26 |

24 |

0,27 |

3,52 |

34 |

|

7 |

0,130 |

3,63 |

26 |

25 |

0,257 |

3,52 |

35 |

|

8 |

0,140 |

3,62 |

27 |

26 |

0,285 |

3,52 |

35 |

|

9 |

0,150 |

3,62 |

27 |

27 |

0,295 |

3,52 |

35 |

|

10 |

0,160 |

3,61 |

27 |

28 |

0,3 |

3,52 |

35 |

|

11 |

0,165 |

3,60 |

28 |

29 |

0,305 |

3,51 |

35 |

|

12 |

0,175 |

3,59 |

28 |

30 |

0,315 |

3,5 |

35 |

|

13 |

0,185 |

3,59 |

28 |

31 |

0,325 |

3,5 |

35 |

|

14 |

0,195 |

3,58 |

28 |

32 |

0,335 |

3,5 |

35 |

|

15 |

0,2 |

3,58 |

28 |

33 |

0,34 |

3,5 |

35 |

|

16 |

0,21 |

3,58 |

28 |

34 |

0,35 |

3,5 |

35 |

|

17 |

0,22 |

3,58 |

29 |

35 |

0,355 |

3,5 |

35 |

Это характерно не только для ТТЛ-микросхем, но и ИМС типа ТТЛШ, МОП, КМОП.

Таким образом, при определении нагрузочной способности микросхем важное значение имеет правильный выбор максимально допустимого значения их выходного тока. Это значение является дополнительным диагностическим критерием. Если уровень этого тока взять «низким», то это приведет к получению заниженного значения нагрузочной способности, если «высоким» - к повышению риска выхода ИМС из строя.

Как показали исследования, отдельные образцы ИМС имеют значение нагрузочной способности значительно выше среднего уровня и могут работать при «сильных» выходных токах.

Исходя из вышеприведенного, можно сделать вывод о необходимости проведения дополнительных исследований нагрузочной способности микросхем различного типа, т. к. на данный момент отсутствует статистически значимые данные о ее уровне и последующей надежности ИМС.

Заключение

Предложено устройство контроля микросхем, которое обеспечивает более высокие значения точности и достоверности определения их на- грузочной способности. При этом упрощена конструкция устройства контроля. Устройство обеспечивает возможность контроля в двух режимах работы и адаптированность к смене испытуемых микросхем. Установлено, что с ростом числа подключенных нагрузок выходное напряжение высокого уровня ИМС падает, а напряжение низкого уровня – возрастает. При этом возрастает температура корпуса микросхемы. Показано, что при контроле ИМС необходимо учитывать не только число входов элементов нагрузки, подключенных к ее выходу, но и величину предельного выходного тока. Возрастающий выходной ток не должен сильно приближаться к значению тока короткого замыкания испытуемой микросхемы. Максимально допустимое значение выходного тока ИМС предложено использовать в качестве дополнительного диагностического критерия.

Список литературы Исследование нагрузочной способности микросхем

- Тюлевин С.В., Пиганов М.Н. Методика и установка диагностического контроля полупроводниковых диодов // Современные направления теоретических и прикладных исследований: сб. науч. тр. по мат-лам междунар. конф. Одесса, 2008. Т. 4. С. 62–67.

- Сергеев В.А., Тетенькин Я.Г. Измерение теплового сопротивления цифровых интегральных схем по изменению частоты колебаний кольцевого генератора // Измерительная техника. 2018. № 2. С. 46–50. DOI: https://doi.org/10.32446/0368- 1025it.2018-2-46-50.

- Forecasting models generation of the electronic means quality / R.O. Mishanov [et al.] // CEUR Workshop Proceedings. 2017. Vol. 1904. P. 124–129.

- Сергеев В.А., Тетенькин Я.Г. Определение тепловых параметров цифровых микросхем по температурным зависимостям времени задержки сигнала // Автоматизация процессов управления. 2015. № 3 (41). С. 89–96.

- Тюлевин С.В., Пиганов М.Н., Еранцева Е.С. К проблеме прогнозирования показателей качества элементов космической аппаратуры // Надежность и качество сложных систем. 2014. № 1 (5). C. 9–17.

- Сергеев В.А., Юдин В.В. Контроль качества цифровых интегральных микросхем по параметрам матрицы тепловой связи // Известия вузов. Электроника. 2009. № 6. С. 72–78.

- Piganov M.N., Mishanov R.O. Technology of diagnostic for non-destructive control of the bipolar integrated circuits // 2nd International Scientific Symposium «Sense. Enable. SPITSE. 2015»: Symposium Proceedings. Saint Petersburg, 2015. P. 38–41.

- Mishanov R.O., Piganov M.N. Individual forecasting of quality characteristics by an extrapolation method for the stabilitrons and the integrates circuits // The Experience of Designing and Application of CAD Systems in Microelectronics (CADSM 2015): Proceedings XIII International conference. Ukraine, Lviv, 2015. P. 242–244. DOI: https://doi.org/10.1109/CADSM.2015.7230846.

- Федоров В.К., Сергеев Н.П., Кондрашин А.А. Контроль и испытания в проектировании и производстве радиоэлектронных средств. М.: Техносфера, 2015. 504 с.

- Apparatus diagnostic for non-destructive control chip CMOS-Type / S.V. Tyulevin [et al.] // European Science and Technology: Materials of the VIII International Research and Practice Conference. Germany, Munich, 2014. P. 398–401.

- Piganov M.N., Tyulevin S.V., Erantseva E.S. Individual prognosis of quality indicators of space equipment elements // The Experience of Designing and Application of CAD Systems in Microelectronics (CADSM 2015): Proceeding XIII International Conference. Ukraine, Lviv, 2015. P. 367–371. DOI: https://doi.org/10.1109/CADSM.2015.7230878.

- Устройство для определения нагрузочной способности микросхем / М.Н. Пиганов [и др.]: патент РФ № 2613573; заявл. 28.10.2015; опубл. 17.03.2017; бюл. № 8.

- Устройство для определения нагрузочной способности микросхем / М.Н. Пиганов [и др.]: патент РФ № 2613568; заявл. 14.12.2015; опубл. 17.03.2017; бюл. № 8.

- Разработка устройства для определения нагрузочной способности микросхем / С.В. Тюлевин [и др.] // Физика волновых процессов и радиотехнические системы. 2017. Т. 20, № 1. С. 49–52.

- Устройство для определения нагрузочной способности микросхем / М.Н. Пиганов [и др.]: патент РФ № 2723968; заявл. 02.07.2019; опубл. 18.06.2020; бюл. № 17.