Ячейка памяти QSRAM

Автор: Тюрин С.Ф.

Журнал: Вестник Пермского университета. Математика. Механика. Информатика @vestnik-psu-mmi

Рубрика: Информатика. Информационные системы

Статья в выпуске: 1 (28), 2015 года.

Бесплатный доступ

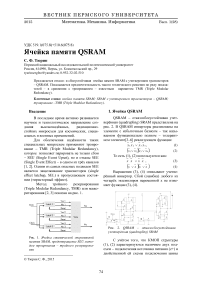

Предлагается отказо- и сбоеустойчивая ячейка памяти SRAM с учетверением транзисторов - QSRAM. Показывается предпочтительность такого технического решения по ряду показателей - в сравнении с троированием - известным вариантом TMR (Triple Modular Redundancy).

Ячейка памяти sram, sram с учетверением транзисторов - qsram, троирование -tmr (triple modular redundancy)

Короткий адрес: https://sciup.org/14729967

IDR: 14729967 | УДК: 519.1(075.8)+510.6(075:8)

Quadrupling SRAM cell

In the work it is proposed quadrupling SRAM cell - QSRAM cell. It is described the simulation of the QSRAM cell by N1 Multisim system.

Список литературы Ячейка памяти QSRAM

- Donald С. Mayer, Ronald С. Lacoe. Designing IntegratedCircuits to Withstand Space Radiation. Vol. 4, № 2. Crosslink. URL http://www.aero.org/publications/crosslink/su mmer2003/06.html (дата обращения: 20.10.2013).

- Юдинцев В. Радиационно-стойкие интегральные схемы. Надёжность в космосе и на земле // Электроника, Наука, Технология. Бизнес: журнал. 2007. № 5. С. 72-77. ISSN 1992-4178. URL: ht^://www.electromcs.ru/ffles/articlej3df70/article_ 592_363.pdf (дата обращения: 27.09.2013).

- Тюрин С.Ф. Надёжность систем автоматизации: учеб. пособие. Перм. нац. исслед. политехи, ун-т. Пермь: Изд-во ПНИПУ, 2012. 262 с.

- Тюрин С.Ф., Морозов А.Н. Отказоустойчивая ячейка памяти с использованием функционально-полных толерантных элементов//Вестник Пермского университета. Серия: Математика. Механика. Информатика. 2012. №4. С. 68-75.

- Тюрин С.Ф. Логические элементы с избыточным базисом//Вестник Пермского университета. Серия: Математика. Механика. Информатика. 2013. № 3(22). С. 91-105.

- Тюрин С.Ф., Плотникова А.Ю. Концепция "зеленой" логики//Вестник Пермского национального исследовательского политехнического университета. Электротехника, информационные технологии, системы управления. 2013. № 58. С. 61-73.

- N1 Multisim. URL: http://sine.ni.com/np/app/main/p/docid/nav-98/lang/ru/(дата обращения: 27.09.2013).