Методика проектирования сети-на-кристалле с парированием сбоев и отказов

Автор: Суворова Елена Александровна

Журнал: Известия Самарского научного центра Российской академии наук @izvestiya-ssc

Рубрика: Информатика, вычислительная техника и управление

Статья в выпуске: 1-2 т.18, 2016 года.

Бесплатный доступ

Возможность парирования (mitigation) сбоев и отказов становится одним из основных требований как для сети-на-кристаллах (СенК) аэрокосмического применения, так и для встраиваемых систем изготавливаемых с использованием малых проектных норм. Наряду с данным требованием для этих классов систем, как правило, существуют достаточно жесткие требования по площади, энергопотреблению. В статье рассматриваются существующие подходы к структурному проектированию СенК с парированием отказов, их ограничения. Предлагается методика проектирования структуры реконфигурируемой СенК с возможностью парирования сбоев и отказов, которая позволяет учесть особенности технологии производства и условий эксплуатации при реализации конкретного проекта.

Системы-на-кристалле (снк), сети-на-кристалле (сенк), реконфигурируемые сенк, парирование сбоев и отказов

Короткий адрес: https://sciup.org/148204408

IDR: 148204408 | УДК: 004.7

The approach for development of NOCs with fault mitigation

The ability of fault’s mitigation become one of the main requirements of NoC’s for aerospace applications and embedded systems manufactured using thin design rules. Along with this requirement there are other requirements for area, power consumption exist. In this paper we consider existing approaches to NoCs with fault mitigation development. We propose an methodology for development of NoC with support of QoS and fault mitigation. This methodology allow to take into account the specific of design process and operating conditions in the implementation of a concrete project.

Текст научной статьи Методика проектирования сети-на-кристалле с парированием сбоев и отказов

IP-блоками. Такие линии связи имеют большую длину. Для систем аэрокосмического применения вследствие этого вероятность искажения сигнала в них в результате внешних воздействий, а также вследствие ускоренного старения является ощутимой по сравнению с более короткими линиями внутри IP-блока. Для встраиваемых систем, изготавливаемых по малым проектным нормам, на характеристиках длинных линий связи в значительной степени сказываются вариации технологического процесса и ускоренное старение. Поэтому для того класса систем также необходимо парировать ошибки на длинных линиях.

В этой статье мы рассматриваем существующие подходы к парированию сбоев и отказов в СенК на структурном уровне, их достоинства и недостатки применительно к рассматриваемым областям применения (методы выявления отказов и сбоев не рассматриваются). Мы предлагаем методику проектирования реконфигурируемой СенК с механизмами парирования сбоев и отказов для аэрокосмических применений и встраиваемых систем, изготавливаемых по малым проектным нормам.

Подходы к проектированию СенК, в которых предусмотрено парирование сбоев и отказов. В основе подходов к проектированию СенК, в которых предусмотрено парирование сбоев и отказов, лежит реконфигурирование структуры связей между компонентами и перенаправление потоков данных в обход отказавших компонентов и линий связи. Система может включать в себя некоторое количество дополнительных связей и резервных компонентов. Потоки данных могут перенаправляться по резервным или основным связям в обход отказавших компонентов.

Как правило, существуют жесткие ограничения на дополнительные аппаратные затраты, поэтому, подходы, основанные на использовании дополнительных линий связи, накладные расходы на реализацию которых невелики, получили наибольшее распространение. К этим подходам относится группа подходов, основанных на использовании резервных путей. Подходы могут применяться для СенК с регулярной и произвольной структурой. Все маршрутизаторы с использованием дополнительных линий связи объединяются в кольцо. В случае выхода из строя части основных связей сохраняется возможность передачи данных с использованием этого кольца. Временные характеристики доставки данных при этом ухудшаются. Для того, что- терминальный узел может подключаться к нескольким бы парировать отказы линий связи между терминаль- маршрутизаторам.

ными узлами и маршрутизаторами, каждый

Таблица 1. Методы парирования ошибок для рассматриваемых технологий

|

СнК аэрокосмического применения |

180 nm |

130 nm |

90 nm |

|

СнК встраиваемых систем |

40 nm |

32 nm, 28 nm |

14 nm |

|

линии связи |

иногда защита от сбоев, путем кодирования для длинных линий связи |

защита от сбоев, путем кодирования для длинных линий связи |

защита от сбоев, путем кодирования для длинных линий связи и для средних линий связи |

|

элементы памяти |

коды Хемминга для памяти настроек, программ (других кодов) |

коды Хемминга для памяти настроек, программ (других кодов), защита буферов, динамически обновляемой памяти (как правило, биты паритета), выборочная защита управляющих автоматов |

коды Хемминга для памяти настроек, программ (других кодов), защита бу-феров, динамически обновляемой памяти (как правило, биты паритета), выборочная защита управляющих автоматов |

|

элементы комбинационн ых схем |

защита не используется |

выборочная защита схем, функционирующих на высоких частотах |

выборочная защита схем |

Данные подходы ориентированы на СенК, в которых наиболее вероятен выход из строя линий связи, а не маршрутизаторов В рамках других подходов обходные пути реализуются непосредственно внутри маршрутизаторов. Реализуются непосредственные связи между некоторыми портами, функционирование которых наиболее важно для функционирования СенК. Эти подходы используются в тех случаях, когда вероятность отказов и сбоев маршрутизаторов выше, чем вероятность отказов линий связи [4]. К недостаткам этих подходов можно отнести достаточно существенное ухудшение времени доставки данных при выходе из строя компонентов.

Существует также группа подходов, основанная на использовании резервных маршрутизаторов (или коммутаторов). Данная группа подходов связана с большими аппаратными затратами. Они зависят от количества резервных маршрутизаторов, включаемых в систему. Однако при использовании этих подходов, как правило, при выходе из строя основных компонентов время доставки данных ухудшается не значительно. Подходы этой группы отличаются друг от друга способами распределения резервных маршрутизаторов в структуре СенК. В ряде СенК со связями на базе двумерной решетки добавляется ряд или столбец резервных маршрутизаторов [5]. В рамках другого подхода маршрутизаторы разделяются на группы (например, по 4 маршрутизатора, расположенных рядом). В каждую группу добавляется один или несколько резервных маршрутизаторов [6].

В ряде подходов используется резервирование для отдельных частей маршрутизаторов, ошибки в которых наиболее вероятны. Например, оно может выполняться для буферов [7]. В рамках этих подходов в ряде случаев используется комбинирование исправных ресурсов буферов с исправными линиями связи. В результате при выходе из строя отдельных компонентов количество путей передачи данных через маршрутизатор сокращается, но некоторая его часть продолжает функционировать. Эти подходы связаны с меньшими аппаратными затратами, чем резервирование на уровне маршрутизаторов, но характеристики передачи данных для них зачастую сравнимы с достижимыми для подходов резервирования маршрутизаторов [8, 9]. Все рассмотренные подходы ориентированы на парирование ошибок в отдельных элементах СенК, отказы и сбои в которых наиболее критичны для конкретных СенК. Предлагаемый подход ориентирован на проектирование различных СенК, позволяет учесть особенность их структуры, технологических библиотек, условия эксплуатации.

Предлагаемый метод проектирования реконфигурируемой СенК, с парированием сбоев и отказов. В [10] нами был предложен подход к проектированию реконфигурируемой структуры СенК без поддержки парирования ошибок. Данная структура обеспечивает возможность реконфигурации графа связей между узлами (поддерживаются регулярные и не регулярные графы связей), количества виртуальных каналов. Предлагаемая нами реконфигурируемая система была ориентирована на возможность использования для проектных норм, начиная с 180-120 нм, с использованием которых уже могут быть построены СнК, включающие 10-20 терминальных узлов. Базовый вариант предлагаемой реконфигурируемой структуры ориентирован на реализацию в условиях довольно жестких технологических ограничений на допустимую длину линий связи, количество пересечений линий связи, что позволяет использовать его для аэрокосмических применений. Расширенные варианты структуры могут быть использованы для встраиваемых систем, с большим количеством узлов, реализуемых по меньшим проектным нормам. Это достигается за счет того, что количество портов и связей в сетевой структуре, параметры блоков буферизации заданы параметрически, допустимые значения параметров определяются исходя из возможностей технологии.

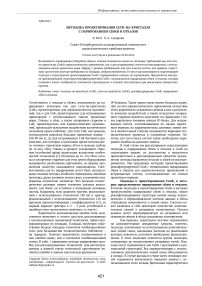

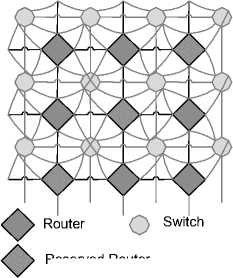

Предлагаемая нами система включает в себя три основных типа блоков: терминальные узлы, маршрутизирующие коммутаторы, коммутаторы каналов. Терминальные узлы подключаются только к маршрутизирующим коммутаторам. Маршрутизирующие коммутаторы могут связываться напрямую или через коммутаторы каналов, в зависимости от заданной конфигурации. Базовый вариант структуры связей NoC представлен на рис. 1. Здесь ромбы соответствуют маршрутизирующим коммутаторам, восьмиугольники соответствуют коммутаторам каналов. На рис. 1б представлен фрагмент базового варианта структуры, в котором показано подключение одного терминального узла (обозначен прямоугольником) к маршрутизатору. В этой структуре к каждому s-port подключено 2 или 3 канала связи. В один момент времени активным будет только один из них. Текущая конфигурация системы в рамках одного кристалла определяется перечнем активных каналов и настройкой коммутаторов каналов. Маршрутизирующие коммутаторы за счет непосредственных связей между собой образуют двумерную решетку. Другие структуры могут быть получены за счет включения в структуру связей коммутаторов каналов.

Router

оммутатор оммутатор

Switch а)

Контроллер Маршрутизатор порта

Контроллер порта

Контроллер порта

Контроллер порта

Терминальный узел

б)

Рис. 1. Вариант структуры межсоединений между маршрутизаторами и терминальными узлами

Возможна динамическая конфигурация данной структуры. Различные части структуры могут быть сконфигурированы независимо друг от друга. Результирующий граф связей может иметь регулярную структуру (например, соответствовать тору на базе двумерной решетки или бинарному дереву), нерегулярную структуру или гибридную структуру с регулярными и нерегулярными фрагментами. Количество топологий, которые можно построить на базе предлагаемой реконфигурируемой структуры, зависит от количества портов маршрутизирующих коммутаторов и коммутаторов каналов, количества линий связи и структуры связей между коммутаторами, использования или не использования виртуальных каналов. Базовый вариант, представленный на рисунке может быть настроен как двухмерная решетка, тор на базе двумерной решетки, трехмерная решетка, тор на базе трехмерной решетки, различные баньян сети, дерево.

Предложенный нами подход к формированию структуры обладает рядом преимуществ по сравнению с другими проектами реконфигурируемых СенК [11-

-

1 4]. В этих структурах топологические коммутаторы (функциональные аналоги коммутаторов каналов, используемых в предложенном нами варианте) расположены непосредственно в портах (перед портами) маршрутизирующих коммутаторов. В предложенном нами коммутаторы каналов расположены как отдельные блоки в структуре связей. Это позволяет, при проектировании СенК:

-

- использовать их для сокращения геометрической длины линий связи между блоками; (коммутатор каналов включает в себя кросскоммутатор, состоящий из элементов комбинационной схемы и может включать FIFO–элементы памяти. Элементы комбинационной схемы выступают в роли усилителей сигнала (повторителей). Геометрическая длина линий связи сокращается за счет их наличия по сравнению с вариантом, в котором коммутатор канала отсутствует. Элементы памяти позволяют управлять достижимой длительностью периода сигнала тактирования.)

-

- управлять размерами crossbarв коммутаторах каналов - в случае наличия жестких технологических ограничений могут использоваться коммутаторы каналов с небольшим количеством портов, распределенные в структуре связей

-

- управлять размерами блока мультиплексирования линий связи в коммутаторах каналов и маршрутизаторах

Эти черты являются очень важными при наличии жестких технологических ограничений, т.к. они позволяют обеспечивать требуемые ограничения по длине линий связи, длительности периода сигнала тактирования, размеру блоков мультиплексирования и кросскоммутаторов.

В этой статье мы предлагаем метод построения СенК парированием сбоев и отказов на основе рассмотренного выше подхода к проектированию структуры СенК. Для этого данный подход дополнен рядом существенных черт. Предлагаемый метод ориентирован на различные технологии производства в рамках рассматриваемой группы технологий, поэтому для компонентов системы должны быть предусмотрены различные варианты защиты (табл. 2). Реализация этого достигается с использованием параметризации RTL модели.

Рассмотрим свойства компонентов СенК (линий связи, коммутаторов каналов, маршрутизаторов) с точки зрения парирования ошибок. Для определенной технологии и условий эксплуатации вероятность отказов в длинных линиях связи между терминальными узлами, маршрутизаторами, коммутаторами каналов зависит от их длины и разрядности. Необходимость парирования отказов для конкретной технологии может быть определена по табл. 1. Как можно видеть из этой таблицы для различных технологий из рассматриваемого перечня требуются разные способы защиты.

В качестве основного механизма защиты линий связи нами выбран механизм на основе битов паритета и, соответственно, механизмы проверки паритета. Этот механизм позволяет очень точно локализовать места возникновения ошибок в графе связей; его реализация возможна в отсутствии буферов (в случае, если буфер пришлось отключить из-за возникшей ошибки) , накладные расходы на его реализацию невелики (дополнительная площадь компонентов СенК не превосходят 1%). Однако данный механизм не обеспечивает защиту в случае возникновения помех на нескольких битовых линиях, входящих в состав линии данных. Если для используемой технологии и условий эксплуатации необходимо парирование таких помех, то пре- дусмотрена возможность использования кода Хеммин-га или специализированных помехоустой-чивых кодов, применяемых к отдельным флитам. В этом случае для их использования, также как и для механизма на основе битов паритета, не требуется буферизация. Дополнительные линии и блоки коди-рования/проверки в структуре компонентов СенК при использовании этих типов кодирования располагаются так же, как и для механизма на основе битов паритета. Выбор конкретного варианта механизма осуществляется за счет параметризации RTL модели. Кроме того, могут включаться мажоритарные схемы для сигналов управления, резервный набор линий данных (и/или механизмы, обеспечивающие снижение разрядности канала данных при выходе из строя части линий). Включение / отключение данных механизмов осуществляется на уровне RTL модели СнК параметрически. Схемы контроля располагаются в портах маршрути-заторов и коммутаторов каналов за блоками мультиплексирования линий связи. Это позволяет минимизировать накладные расходы на реализацию (они находятся в пределах 3% при коэффициенте дублирования 3).

Блоки буферизации (используются в коммутаторе каналов и маршрутизаторе). Для блоков буферизации в зависимости от используемой технологии также могут использоваться различные способы парирования ошибок. Поскольку в предлагаемой нами NoC может использоваться режим коммутации на лету, способ на основе CRC не подходит. В зависимости от выбранной технологии могут использоваться биты паритета, кодирование Хемминга. Для блоков буферизации могут использоваться другие механизмы парирования отказов, чем для линий связи.

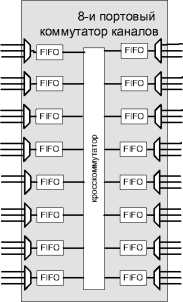

Коммутатор каналов включает в себя блоки мультиплексирования соединений (комбинационные схемы) и буфера для каждого порта, а также кросскоммутатор между портами (комбинационная схема). Для всех рассматриваемых технологий требуется парирование ошибок в буферах. Для комбинационных схем требуется парирование только для самых тонких из рассматриваемых технологий. Буфера маленькие (2-4 флита), поэтому отключаются целиком при выходе из строя. Обход кросскоммутатора не делается. Это не рационально, т.к. вероятность выхода из строя мала: в нем только элементы комбинационной схемы, которые наиболее устойчивы к сбоям и отказам, количество портов мало (это обеспечивается подходом к формированию СенК вцелом).

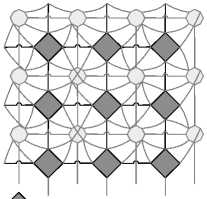

Если кросскоммутатор все-таки выходит из строя, то данные будут передаваться в обход, по другим кросскоммутаторам. Предлагаемый нами подход ориентирован на использование коммутаторов каналов с относительно небольшим количеством портов. Такие блоки имеют относительно небольшую площадь. В структуре СенК они могут группироваться. В группу может быть включен один или несколько резервных коммутаторов каналов (их количество определяется на этапе проектирования системы в зависимости от количества коммутаторов в группе, планируемой технологии производства и условий эксплуатации). Использование этого подхода позволяет в разы сократить загрузку остальной части системы в случае выхода из строя одного из коммутаторов и площадь, занимаемую резервными коммутаторами каналов.

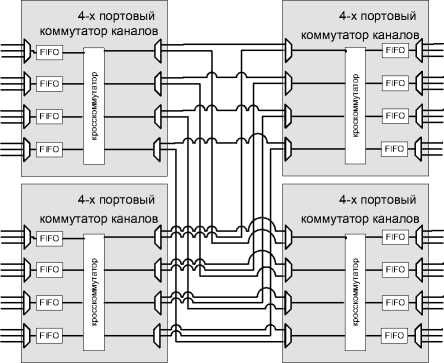

Рис. 2. Пример варианта замены одного 8-и портового коммутатора каналов на группу из 4-х коммутаторов с 4-мя портами

Например, если необходим коммутатор каналов с 8 входами/выходами, то в структуре может быть поставлена группа из 4-х коммутаторов каналов по 4 входа / выхода (рис. 2). Площадь этой группы и временные задержки передачи данных для нее будут таким же, как и для 8-и портового коммутатора. Количество и размер блоков FIFO в группе тот же самый, что и в исходном коммутаторе. Суммарная площадь всех кросскоммутаторов в группе такая же, как и площадь 8-и портового корсскоммутатора. Группа включает в себя дополнительные мультиплексоры, но их площадь пренебрежимо мала. Данные передаются через дополнительные линии связи и дополнительный кросскоммутатор. Однако задержки в этих линиях связи пренебрежимо малы, т.к. линии короткие. Суммарные задержки в двух 4-х портовых кросскоммутаторах равны задержкам в одном 8-и портовом кросскоммутаторе. Благодаря мультиплексорам в каждом порту группа коммутаторов может передавать данные как неблокирующий коммутатор. Однако вероятность возникновения ошибки в каждом из коммутаторов группы в 4 раза ниже, чем в 8-и портовом коммутаторе. Если один из коммутаторов выйдет из строя, остальные могут продолжать корректное функционирование. Это позволяет существенно снизить количество перенаправляемых в случае возникновения ошибки потоков данных, загрузку ими остальных элементов СенК. Добавление в группу одного резервного коммутатора для парирования одной ошибки увеличит ее площадь в 1,25 раза. Если же используется один 8-и портовый коммутатор, то включение резервного коммутатора увеличит площадь в 2 раза. Таким образом, выигрыш по площади от использования этого подхода на данном примере 1,6 раза.

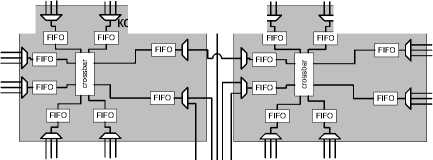

Маршрутизатор. Рассмотрим механизмы парирования ошибок в структуре маршрутизаторов. Маршрутизатор включает в себя блоки мультиплексирования соединений (комбинационные схемы) и буфера для каждого порта, контроллеры портов, выполняющие маршрутизацию пакетов (конечные автоматы, включающие в себя элементы памяти и комбинационные схемы), а также кросскоммутатор между портами (комбинационная схема). В маршрутизаторах могут использоваться буфера существенно большего размера, чем в коммутаторах каналов. Поэтому для них предусмотрены механизмы частичного отключения в случае выхода из строя отдельных ячеек. Для маршрутизаторов каналов также может использоваться подход включения резервного маршрутизатора в группу. Однако, поскольку маршрутизаторы имеют существенно большую площадь, чем коммутаторы каналов, он не является основным. Для систем, в которых накладные расходы на реализацию этого подхода являются неприемлемыми, используется включение дополнительного ряда (рядов) маршрутизаторов. Однако в отличие от подхода, предложенного в [6], добавляются не горизонтальные ряды, а ряды, расположенные по диагонали; при используемой структуре связей это позволяет сократить количество перенастраиваемых маршрутизаторов в случае выхода из строя одного маршрутизатора в 2 раза (за счет сокращения среднего расстояния между вышедшим из строя маршрутизатором и резервным маршрутизатором). На рис. 3 представлен пример размещения резервных маршрутизаторов (выделены штриховкой). Терминальный узел подключается к нескольким соседним маршрутизаторам.

Reserved Router

Рис. 3. Пример размещения резервных маршрутизаторов

Методика формирования структуры СенК.

-

1. В соответствии с используемой технологией, условиями эксплуатации и геометрическими размерами блоков терминальных узлов определить механизмы защиты для линий связи из указанного выше набора.

-

2. В соответствии с используемой технологией, условиями эксплуатации определить механизмы парирования ошибок в буферах.

-

3. В соответствии с наборами приложений, для которых планируется использование СенК, требуемыми пропускными способностями каналов, требуемыми вариантами графов связей определить базовый вариант структуры.

-

4. В соответствии с используемой технологией, условиями эксплуатации и с учетом площадей блоков определить допустимое количество портов коммутатора каналов, определить необходимость резервирования

-

5. В соответствии с используемой технологией и условиями эксплуатации определить необходимое количество резервных маршрутизаторов, включить их в состав системы

-

6. В соответствии с используемой технологией и условиями эксплуатации определить количество маршрутизаторов, к которым должен быть подключен терминальный узел. Подключить терминальные узлы к требуемому количеству маршрутизаторов. Для подключения терминального узла выбираются ближайшие к нему маршрутизаторы.

коммутаторов каналов. Если в базовом варианте структуры коммутаторы каналов имеют большее количество портов, заменить их на группы. Если определена необходимость резервирования, то включить в группы резервные коммутаторы каналов.

Проверка парирования ошибок в предложенной модели. В настоящее время существует довольно большое количество САПР, позволяющих осуществить моделирование влияния ошибок на функционирование СнК, СвК. Наибольшее распространение получили Synopsys TetraMAX ATPG, Mentor Graphics TessentFastScan, Mentor Graphics TessentTestKompress, Cadence Verifault, Cadence Encounter True-Time ATPG, SyntestTurboFault, Winterlogic Z01X. Данные инструменты в основном поддерживают одинаковый перечень возможных ошибок, схему их внедрения. Рассмотрим особенности их функционирования на примере инструментария CadenceVeriFault [15].В качестве входных данных для него могут использоваться списки связей, полученные в результате логического и физического синтеза. Поддерживаются следующие типы ошибок:

-

- константный 0;

-

- константная 1;

-

- обрыв линии связи;

-

- образование моста между линиями связи.

Данный инструментарий позволяет выбрать нужные типы ошибок и выбрать область проекта (СнК), в которой они могут происходить. Перед осуществлением процесса моделирования данный инструментарий создает копию исходной модели, в заданные области которой инжектирует указанные типы ошибок. После этого осуществляется моделирование исходной версии модели и версии с инжектированными ошибками на заданных пользователем тестовых векторах и вычисляется процент выявления ошибок для данного пользовательского теста. Отдельно определяются ошибки, которые являются ненаблюдаемыми и ошибки, которые потенциально наблюдаемы, но не были выявлены в ходе тестирования. Однако данный инструментарий не позволяет моделировать ситуацию возникновения ошибки в процессе функционирования модели. Это связано с тем, что инструментарий, как и большинство существующих в настоящее время САПР, ориентирован прежде всего на моделирование производственных дефектов, а не ошибок, возникающих уже в ходе функционирования системы.

В настоящее время существует ряд подходов, позволяющих устранить этот недостаток. Большинство из них ориентировано на внедрение в модель устройства специализированных блоков, которые искажают состояние элементов памяти уже в ходе функционирования модели [16]. Способы внесения искажений могут быть различными. Наиболее распространены подход, при котором специализированные блоки записывают в память системы искаженные значения, обращаясь к ним через основную коммуникационную систему, и подход, при котором для внесения искажений используются специализированные функции САПР, такие как nc_force (Cadence) или прямые обращения к компонентам модели по их иерархическим именам (применимо только в тех случаях, когда модель написана на Verilog). К недостаткам данных подходов можно отнести необходимость включения в модель (RTL, список связей) специализированных компонентов, что может привести к привнесению в нее функциональных ошибок. Также в рамках этих подходов ошибки могут вноситься только в элементы памяти, они не могут вноситься в элементы комбинационных схем и линии связи.

Для устранения этих недостатков нами был разработан подход, в рамках которого модели ошибок встраиваются непосредственно в модели библиотечных компонентов. В модель компонента встраивается два счетчика, обеспечивающих определение времени возникновения ошибки и продолжительности ее действия. Правила подсчета могут быть различными, тип правила задается параметрически. Компоненты могут быть разделены на группы, для каждой из которых могут быть определены типы возможных ошибок и вероятности их возникновения. Использование этого подхода позволяет в частности осуществить моделирование коротких перепадов напряжения (глитчей) на выходах отдельных компонентов. Это позволяет промоделировать ошибки не только в самих компонентах, но и в линиях связи, подключенных к их выходам. Встраивание моделей ошибок необходимо осуществлять однократно для каждой технологической библиотеки, с которой планируется работать. Параметры моделей ошибок вынесены в отдельный пакет и могут изменяться для каждого конкретного проекта в соответствии с планируемыми для него условиями эксплуатации.

Для проверки предложенной методики были сконфигурированы RTL-модели, включающие в себя от 4-х до 16-и маршрутизирующих коммутаторов и от 16 до 64-х коммутаторов каналов. В качестве терминальных узлов были использованы генераторы и приемники пакетов данных. Они обеспечивают заданную пользователем загрузку сети (задается параметрически) и проверку результатов передачи данных. Был выполнен логический синтез с использованием Cadence RTL Compiler. Далее было осуществлено моделирование с использованием Cadence Verifault и библиотеки модифицированных моделей библиотечных компонентов, обеспечивающих возможность внесения ошибок. Моделирование выполнялось при загрузке СенК от 40% до 90%. В ходе моделирования рассматривалась вероятность возникновения soft ошибок от 10-12 до 10-6, вероятность возникновения hard-ошибок от 10-15 до 10-12; указанные диапазоны вероятностей были выбраны на основе данных, приведенных в [16]. В ходе моделирования не возникло ситуаций взаимоблокировок пакетов. Количество недоставленных пакетов и ошибочных пакетов не превысило 3% от общего количества передаваемых пакетов при вероятности soft errors = 10-6, вероятности hard errors = 10-12, и менее 1% при вероятности soft errors = 10-12, вероятности hard errors = 10-15.

Выводы: рассмотрены источники возникновения ошибок в СенК аэрокосмического применения и в СенК для встраиваемых применений, изготавливаемых по малым проектным нормам. Рассмотрены методы парирования ошибок. Предложен метод проектирования структуры СенК, при котором парирование сбоев и отказов осуществляется за счет динамического реконфигурирования. В отличие от существующих подходов он ориентирован на применение для различных технологий из рассматриваемого перечня за счет поддержки различных механизмов парирования ошибок. Для проверки результатов использовано имитационное моделирование. Предложен подход к имитационному моделированию, позволяющий моделировать поведение системы в условиях динамически возникающих ошибок с использованием инструментария Cadence Verifault, базовый вариант которого ориентирован на моделирование системы в условиях наличия только статических ошибок. Такой подход может быть использован также в сочетании с инструментарием Syn-opsys и других разработчиков.

Исследования выполнены при финансовой поддержке Министерства Образования и Науки Российской Федерации научно-исследовательской работы, выполняемой в рамках базовой части государственного задания в 2016 году.

Список литературы Методика проектирования сети-на-кристалле с парированием сбоев и отказов

- Cota, E. Reliability, Availability and Serviceability of Networks-on-Chip/E. Cota, A. de Morais Amory, M. S. Lubaszewski. -Springer, 2012, 209 p.

- Jafri, S. Energy-aware fault-tolerant network-on-chips for addressing multiple traffic classes/S. Jafri, L. Guang, A. Hemani et al.//Microprocessors and Microsystems. 2013. Vol. 37, issue 8. P. 811-822.

- International Technology Roadmap for Semiconductors (ITRS), 2013. -Режим доступа: http://www.itrs2.net/2013-itrs.html

- Koibuchi, M. A lightweight fault-tolerant mechanism for network-on-chip/M. Koibuchi, M. Hiroki, A. Hideharu et al.//in Proceedings of the international symposium on networks-on-chip (NOCS). 2008. P. 13-22.

- Chang, Y.C. On the design and analysis of fault tolerant NoC architecture using spare routers/Y.C. Chang, C.T. Chiu, S.Y. Lin et al.//in Proceedings of the Asia and South pacific design automation conference (ASPDAC). 2011. P. 431-436.

- Ren, Y. A fault tolerant NoC architecture using quad-spare mesh topology and dynamic reconfiguration/Y. Ren, L. Liu, S. Yin et al.//Journal of Systems Architecture. 2013. Vol. 59. P. 482-491.

- Liu, C. A resilient on-chip router design through data path salvaging/C. Liu, L. Zhang, Y. Han et al.//in Proceedings of the Asia and South Pacific design automation conference (ASPDAC). 2011. P. 437-442.

- Fick, D. Vicis: a reliable network for unreliable silicon/D. Fick, A. De Orio, J. Hu et al.//in Proceedings of the ACM/IEEE design automation conference (DAC). 2009. P. 812-817.

- Kakoee, M.R. ReliNoC: a reliable network for priority-based on-chip communication/M.R. Kakoee, V. Bertacco, L. Benini//in Proceedings of the design, automation and test in Europe conference (DATE). 2011. P. 1-6.

- Суворова, Е.А. Методы проектирования реконфигурируемых коммуникационных систем для сетей на кристалле, разрабатываемых по 3D технологии/Е.А. Суворова, Ю.Е. Шейнин, Н.А. Матвеева//Известия Самарского научного центра Российской академии наук. 2014. Том 16, №6(2). С. 605-611.

- Stensgaard, M.B. ReNoC: A Network-on-Chip Architecture with Reconfigurable Topology/M.B. Stensgaard, J. Sparso//Proceedings of Second ACM/IEEE International Symposium. 7-10 April 2008. P. 55-64.

- Marculescu, R. Key Research Problems in NoC Design: A Holistic Perspective/R. Marculescu, Hu Jingcao; U.Y. Ogras//Hardware/Software Codesign and System Synthesis, CODES+ISSS '05, Third IEEE/ACM/IFIP International Conference. Sept. 2005. P. 69-74.

- Modarressi, M. Power-Aware Mapping for Reconfigurable NoC Architectures/M. Modarressi, H. Sarbazi-Azad//Proceedings of the 25th International Computer Design Conference. 7-10 Oct. 2007. P. 417-422.

- Ogras, U.Y. Application-Specific Network-on-Chip Architecture Customization via Long-Range Link Insertion/U.Y. Ogras, R. Marculescu//Proceedings of IEEE/ACM International Conference on Computer-Aided Design. 6-10 Nov. 2005. P. 246-253.

- Verifault-XL® User Guide/Cadence Inc. 2014. 220 p.

- Yaghini, P.M. Investigation of transient fault effects in synchronous and asynchronous Network on Chip router/P. M. Yaghini, A. Eghbal, H. Pedram et al.//Journal of Systems Architecture. 2011. V. 57. P. 61-68.