Моделирование влияния резервирования на энергопотребление самосинхронных схем

Автор: Каменских А.Н.

Журнал: Вестник Пермского университета. Математика. Механика. Информатика @vestnik-psu-mmi

Рубрика: Информатика. Информационные системы

Статья в выпуске: 4 (31), 2015 года.

Бесплатный доступ

Вектор развития микро-, а скорее уже наноэлектроники направлен в сторону постоянного уменьшения базового напряжения питания, однако современные методы проектирования позволяют не только снижать базовое напряжение, но и варьировать рабочее напряжение питания. Вычислительные системы с адаптивным питаниям позволяют существенно увеличить энергоэффективность вычислительной техники. Важной задачей для построения таких систем является получение данных о динамике характеристик вследствие масштабирования входных параметров как экспериментальных, так и с помощью средств моделирования. Так как вычислительные системы с адаптивным питанием приобретают такое важное свойство как устойчивость к сбоям источника питания, то необходимо также оценить возможность их повсеместного внедрения в аппаратуру для критических областей применения. Такая аппаратура, как правило, проектируется с пассивной отказоустойчивостью. В статье приводятся данные моделирования отказоустойчивых самосинхронных полных сумматоров в системе схемотехнического моделирования.

Самосинхронная схемотехника (ссс), надежность, отказоустойчивость, избыточные базисы, устойчивость, энергоэффективность, энергонадежность

Короткий адрес: https://sciup.org/14730016

IDR: 14730016 | УДК: 004.05

The simulation of influence of redundancy on energy-consumption

The development of microelectronics is focused on reduction of energy-consumption. However, modern designing techniques allows not only reduce value of supply voltage but also make it dynamic to control performance and energy-consumption. Energy-modulated approach greatly reduce energy-efficiency of a computing system. Important task in the development of energy-modulated approach is to receive test&simulation results for different circuits. Computing systems with energy-modulation becomes tolerant to faults in power supply. Thus, we should analyze how it can be implemented in computing systems for critical fields of application. Fault-tolerant techniques of synthesis is often used in such computing systems. One of the base technique in energy-modulated computing is use of a self-timed circuit. In this paper the simulation results for fault-tolerant self-timed full adder is presented.

Текст научной статьи Моделирование влияния резервирования на энергопотребление самосинхронных схем

Благодаря свойству функционирования независимо от задержек, а значит и от условий среды, а также заметно меньшему энергопотреблению, по сравнению с синхронными аналогами, самосинхронная схемотехника стала активно развиваться для применения в мобильной вычислительной технике (ВТ) и в ВТ для критических систем применения. Эти свойства были использованы при построении вычислительных систем с адаптивным питанием [1].

В таких системах быстродействие и энергопотребление выступают в роли динамических параметров. Если нет необходимости в высоком быстродействии, происходит снижение напряжения питания и операции выполняются медленно. Однако такой подход ведет к увеличению вероятности сбоя [2, 3], поэтому возникает потребность в совершенствовании методов повышения надежности, с учетом специфики самосинхронных схем. По- вышение надежности цифрового устройства неизбежно связано с увеличением числа транзисторов, т. е., как правило, ведет и к росту энергопотребления, и к снижению частоты работы. В статье приводятся и анализируются результаты моделирования отказоустойчивых самосинхронных схем, спроектированных с применением различных методов резервирования.

1. Моделирование схем и показатели оценки

В самосинхронной схемотехнике быстродействие зависит от условий, в которых работает устройство, в основном от напряжения питания и температуры. В связи с этим был предложен показатель для оценки энергопотребления – мощность, приведенная к единице частоты [4], так как операции производятся в один такт конвейера, то по сути этот показатель отражает затраты электроэнергии на операцию:

I -и

P _ 1 CC C CC

F F

.

Замеры будут производиться на моделях самосинхронного сумматора в четырех возможных реализациях – самосинхронная, отказоустойчивая самосинхронная с резервированием каждого транзистора, отказоустойчивая самосинхронная с резервированием сетей подключения общей шины и шины питания, самосинхронное мажоритирование.

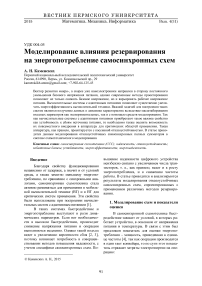

Моделирование выполнено в программном продукте NI MultiSim с использованием транзисторов моделей 2N7000 и BST122. Так как блоки спейсера и индикации не меняются, то потребление тока будем измерять для всей схемы в целом, при циклическом режиме работы. Оценка дается для двух схем, в первой (мажоритарная функция) резервирование транзисторного уровня не требует декомпозиции. Исходная реализация функции сложения по модулю два (S) представлена на рис. 1 [5].

Рис. 1. Самосинхронный двоичный сумматор

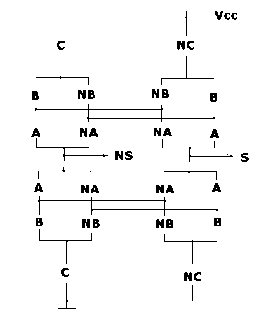

Резервирование транзисторного уровня осуществляется по функции f 1 2 _ x i x i v x i x i , т.е. каждый транзистор заменяется цепочкой транзисторов (рис. 2).

Рис. 2. Резервирование транзистора по функции f 1 2 _ x i x i v x i x i

2. Оценка энергопотребления и быстродействия

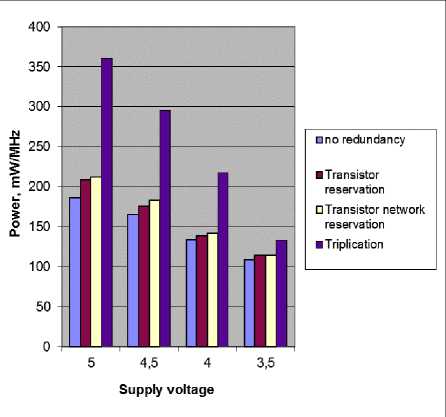

Из-за ограничений описаний моделей переключения в ходе моделирования останавливаются при снижении напряжения питания ниже 3.5В (при исходных 5В). Кроме того, схема нормально функционирует при любом числе последовательно соединенных транзисторов. В табл. 1–2 приведены результаты моделирования отдельно для каждого элемента. На рис. 3 данные из табл. 2 представлены в виде диаграммы, которая позволит оценить влияние резервирования и изменения напряжения на энергопотребление.

Таблица.1. Параметры потребления электроэнергии для мажоритарного элемента

|

№ |

Напряжение, В |

Ток, мА |

Задержка, нс |

Приведенная мощность, мВт/МГц |

|

1 |

5 |

93 |

291 |

135.32 |

|

2 |

4.5 |

63 |

393 |

111.42 |

|

3 |

4 |

39 |

582 |

90.79 |

|

4 |

3.5 |

20 |

1002 |

70.14 |

|

5 |

5 |

83 |

337 |

139.86 |

|

6 |

4.5 |

57 |

455 |

116.71 |

|

7 |

4 |

35 |

674 |

94.36 |

|

8 |

3.5 |

18 |

1166 |

73.46 |

|

9 |

5 |

85 |

335 |

142.38 |

|

10 |

4.5 |

57 |

457 |

117.22 |

|

11 |

4 |

35 |

670 |

93.80 |

|

12 |

3.5 |

18 |

10 |

73.21 |

Таблица 2. Параметры потребления электроэнергии для элемента сложения по модулю два

|

№ |

Напряжение, В |

Ток, мА |

Задержка, нс |

Приведенная мощность, мВт/МГц |

|

1 |

5 |

109 |

360 |

196.20 |

|

2 |

4.5 |

76 |

484 |

165.53 |

|

3 |

4 |

47 |

710 |

133.48 |

|

4 |

3.5 |

29 |

1067 |

108.30 |

|

5 |

5 |

88 |

474 |

208.56 |

|

6 |

4.5 |

63 |

619 |

175.49 |

|

7 |

4 |

39 |

889 |

138.68 |

|

8 |

3.5 |

22 |

1485 |

114.35 |

|

9 |

5 |

90 |

471 |

211.95 |

|

10 |

4.5 |

66 |

615 |

182.66 |

|

11 |

4 |

40 |

887 |

141.92 |

|

12 |

3.5 |

22 |

1480 |

113.96 |

|

13 |

5 |

175 |

412 |

360.50 |

|

14 |

4.5 |

120 |

546 |

294.84 |

|

15 |

4 |

69 |

801 |

217.87 |

|

16 |

3.5 |

31 |

1230 |

133.46 |

Рис. 3. Зависимость энергопотребления на единицу частоты от напряжения питания и выбранного метода резервирования

Разница в энергопотреблении между резервированием единичного транзистора и всей цепочки подключения минимальна и укладывается в погрешность измерений. В то же время, схема с мажоритарным резервированием стабильно потребляет больше энергии на один МГц [6].

Выводы

В этой статье проанализирована первая составляющая – влияние различных методов обеспечения пассивной отказоустойчивости на энергопотребление устройства.

Умные вычислительные системы, в том числе и управляющие своим энергопотреблением, являются одним из ведущих направлений развития электроники, так современные процессоры Intel уже используют этот механизм, однако все еще в сочетании с синхронной архитектурой [7]. Самосинхронная схемотехника дает неоспоримые преимущества в виде широкого диапазона работоспособности, тесты самосинхронных устройств подтвердили их работу на ультранизком напряжении питания, а также возможность работы при сверхнизких температурах. Таким образом, самосинхронная схемотехника становится базовым решением для вычислительных систем с адаптивным питанием. При этом для отказоустойчивых систем развитие происходит в том же направлении, ведь резкое падение напряжения можно рассматривать и как неисправность в работе устройства, а значит, появление устойчивости к этим неисправностям повысит надежность. При этом необходимо учитывать взаимное влияние энергосбережения и надежности.

Список литературы Моделирование влияния резервирования на энергопотребление самосинхронных схем

- Yakovlev A. Energy-modulated computing//Design, Automation & Test in Europe Conference & Exhibition (DATE), 2011. IEEE, 2011. С. 1-6

- Mukhopadhyay S., Mahmoodi-Meimand H., Roy K. Modeling and estimation of failure probability due to parameter variations in nano-scale SRAMs for yield enhancement//VLSI Circuits, 2004. Digest of Technical Papers. 2004 Symposium on. IEEE, 2004. С.64-67

- Mehta N. An ultra-low-energy, variation-tolerant FPGA architecture using component-specific mapping: дис. California Institute of Technology, 2013

- Степченков Ю.А., Петрухин В.С., Дьяченко Ю.Г. Опыт разработки самосинхронного ядра микроконтроллера на базовом матричном кристалле//Нано-и микросистемная техника. 2006. №. 5. С. 29-36.

- Tyurin S.F., Kamenskih A.N. RESEARCH INTO THE RESERVATION OF LOGIC FUNCTIONS AT TRANSISTOR-LEVEL//In the World of Scientific Discoveries/V Mire Nauchnykh Otkrytiy. 2014. Т. 58. № 10.

- Kamenskih A.N., Tyurin S.F. Advanced approach to development of energy-aware and naturally reliable computing systems//Young Researchers in Electrical and Electronic Engineering Conference (EICon-RusNW), 2015. IEEE NW Russia. IEEE, 2015. С. 75-77

- Сергей Пахомов. Особенности настройки систем с процессором Intel Core i7. URL: http://compress.ru/Article.aspx?id=19828 (дата обращения: 01.08.2015)