Проектирование кодера PZ-сигналов методом регистрового автомата

Автор: Романова Анастасия Александровна, Сивков Степан Игоревич, Новиков Леонид Григорьевич, Кревский Андрей Константинович

Рубрика: Краткие сообщения

Статья в выпуске: 4 т.16, 2016 года.

Бесплатный доступ

В последнее время для передачи информации используются различные принципы кодирования. Все они обладают своими достоинствами и недостатками. Быстрая передача информации позволяет значительно сократить время выполнения преобразования, объем памяти, количество используемых логических элементов. В данной работе показан новый принцип кодирования, основанный на распознавании PZ-рядов согласно их частоте, фазе, длине. На основе работы маркеров, выполняющих различные действия над сигналом, построен регистровый автомат. Для иллюстрации работы маркеров построен цифровой автомат. Подробно рассмотрен принцип проектирования кодера, методом регистрового автомата. Применение такого кодера позволит оптимизировать обработку информации только по изменению входного сигнала. В качестве пакета моделирования использовались программы Active HDL, в котором получены временные диаграммы, и Quartus. Приведены блок-схемы всех устройств и схемы моделирования.

Цифровой автомат, регистровый автомат, кодер, pz-сигнал

Короткий адрес: https://sciup.org/147155148

IDR: 147155148 | УДК: 004.312.26 | DOI: 10.14529/ctcr160418

The design of the coder PZ-signal method register-based automaton

Recently, using different principles of coding for information transmission. They all have their advantages and disadvantages. Fast transmission of information allows to reduce considerably the run time of the conversion, the amount of memory, number of used logic elements. This paper shows a new principle of coding is based on the recognition of the PZ-series according to their frequency, phase, length. Based on the work of markers to perform operations on the signal, constructed a register-based automation. To illustrate the operation of the markers of the digital automation. In detail the design principle of the encoder using the method of register of the automation. The use of such a coder will optimize the processing of information only at the change of the input signal. As the simulation package programs were used Active HDL, in which the received waveforms, and Quartus. The following is the block diagram of all devices and circuits modeling.

Текст краткого сообщения Проектирование кодера PZ-сигналов методом регистрового автомата

Вопрос о компактном представлении информации привлекает внимание уже несколько десятилетий. Проблемами передачи, преобразования и экономного кодирования занимались такие ученые как К. Шеннон, Д. Хаффман, П. Говард, Д. Виттер, Д. Клири, Я. Уиттен, Р. Нил, Ф. Рубин, М. Шиндлер, Э. Моффат, А. Хаар. Несмотря на многообразие алгоритмов, методов, программных и аппаратных реализаций, вопрос о быстрой и качественной обработке информации остается актуальным. Быстрая передача информации позволяет значительно сократить время выполнения преобразования, объем памяти, количество используемых логических элементов. Основными характеристиками, влияющими на выбор определенного метода, являются эффективность кодирования, коэффициент сжатия, степень соответствия сигнала исходному. Также влияет на выбор кодера его вычислительная мощность, стоимость оборудования [2].

1. Построение цифрового автомата

Для сжатия и быстрой передачи информации используются различные принципы кодирования информации такие, как префиксный, арифметический, ассоциативный. Применение специальных приемов повышения производительности в методе арифметического кодирования позволяет упростить хранение данных, но ведет к снижению эффективности кодирования. Преимущества префиксного кодирования: простота и высокая производительность, а недостатки – невозможность создать код целой длины, что ведет к ухудшению эффективности. В методе ассоциативного кодирования код генерируется с учетом длины совпадения, но накладываются ограничения на объем обрабатываемой информации. Предлагаемый метод кодирования заключается в распознавании PZ-рядов согласно их частоте, фазе, длине и другим параметрам [3].

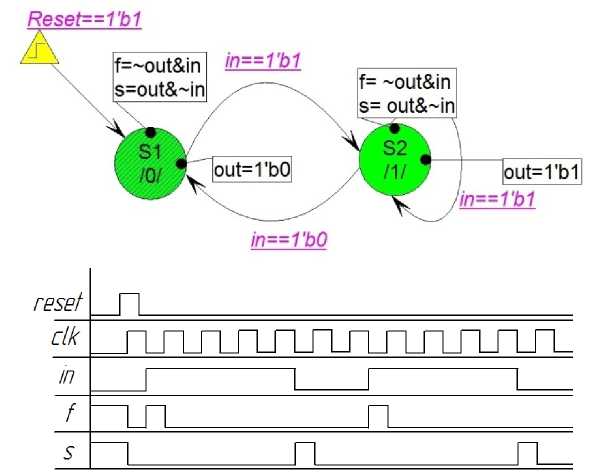

Для исполнения данного принципа можно использовать маркеры, работа которых базируется на простых логических операциях таких, как логическое сложение и умножение, сложение по модулю два. Маркеры дают возможность выполнять различные действия над сигналом: выделять фронт и срез, выделять границы сигнала, изменять длину сигнала. Для иллюстрации работы маркеров построим цифровой автомат, который будет выделять фронт и срез сигнала [1].

Рис. 1. Автомат модуля fsm и временные диаграммы

2. Построение регистра

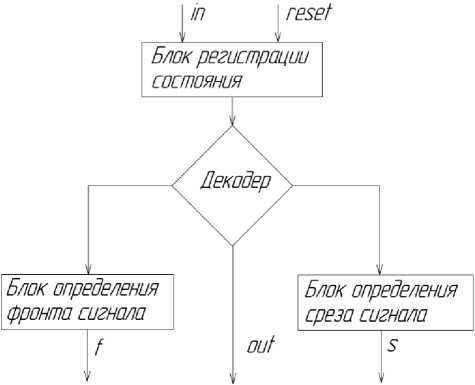

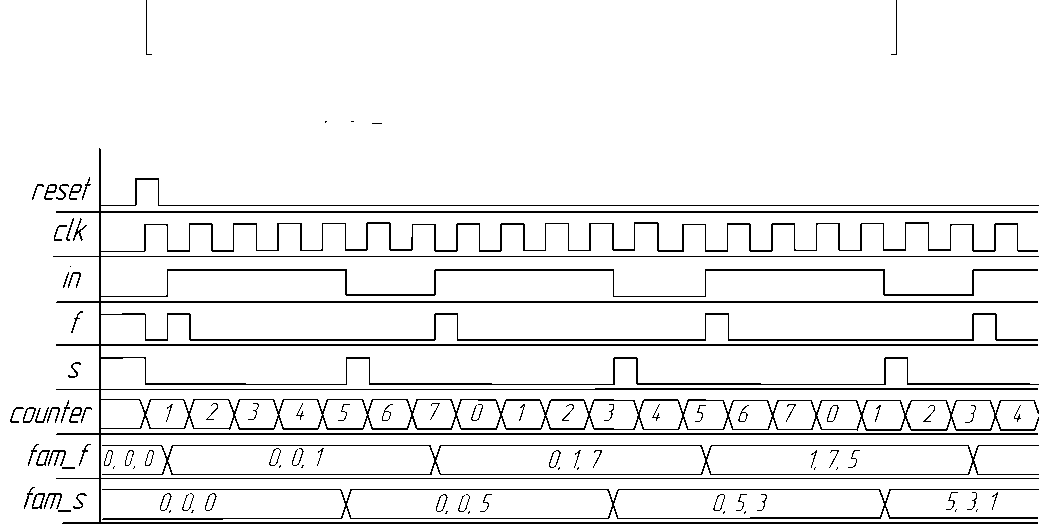

На основе маркеров, описанных в виде цифрового автомата, можно реализовать систему кодирования, работающую по принципу регистрового автомата. На рис. 2 представлена его функциональная схема и временная диаграмма. Блок регистрации состояния выполнен на основе мультиплексора и регистра, представленного в виде D-триггера. При появлении входного

Рис. 2. Блок-схема и временная диаграмма регистра сигнала при условии, что начальное состояние автомата нулевое, мультиплексор меняет свое состояние на противоположное и сохраняет его в регистре. Затем сигнал поступает на декодер, который фиксирует фронт или срез сигнала.

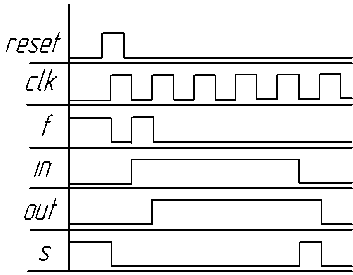

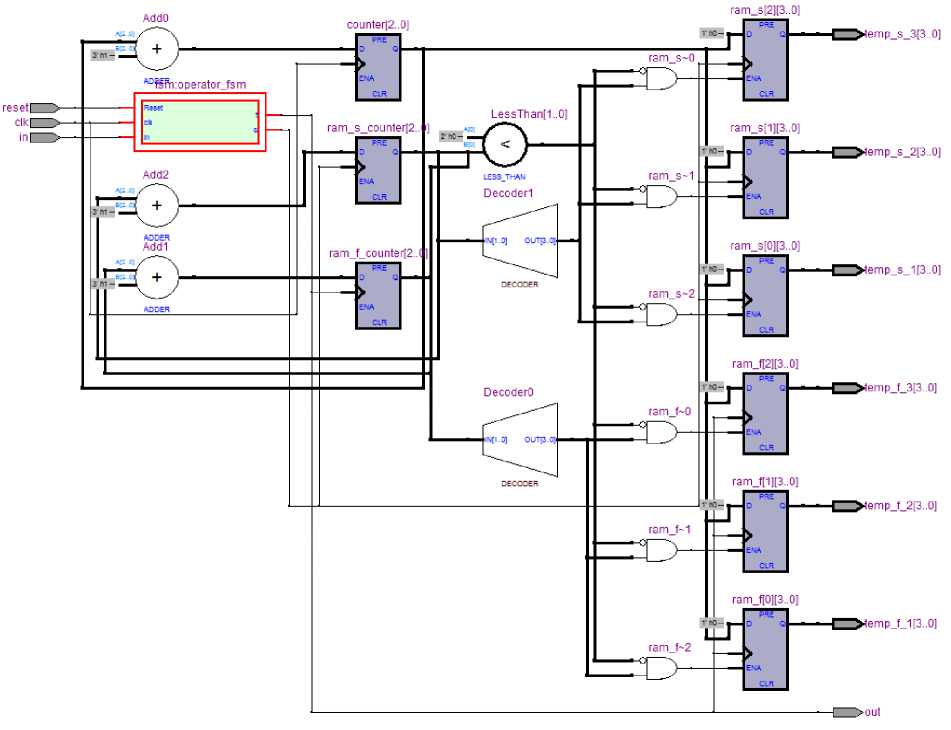

Пр и пост упл ении высо к ог о ур о вня си г на л а з ап ускается процесс регистрации сигнала в б л оке о п р е де л ения фр он т а сиг н ала. Данный блок выполнен при помощи м ул ь т ипл е ксор а, н а в ы х оде к о т ор о го р а спол о жен р е гистр. Данный элемент позволяет синхрониз ир о вать вы хо дн о й с иг н ал с вхо дн ы м . Пр и пост упл ени и низ к о г о уро в ня сиг н ала в блоке определения среза сигнала н ач ина ет ся про це сс ре г и ст р ац ии среза входного сигнала. Присутствие двух р ег истр о в о бр аз у ю т з а де рж ку на по л так т а дл я в сей схемы. Схема моделирования построенн о го р е г ис т р а приведена на рис. 3.

DecoderO

Рис. 3. Схема моделирования регистрового автомата

3. Построение кодера

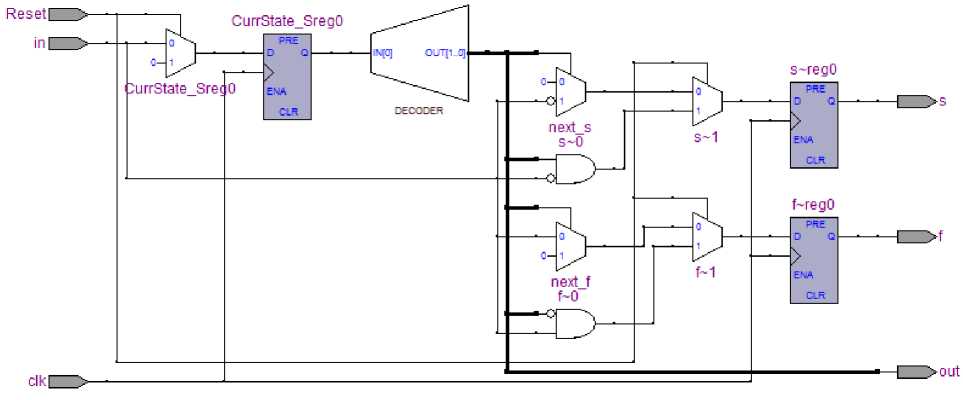

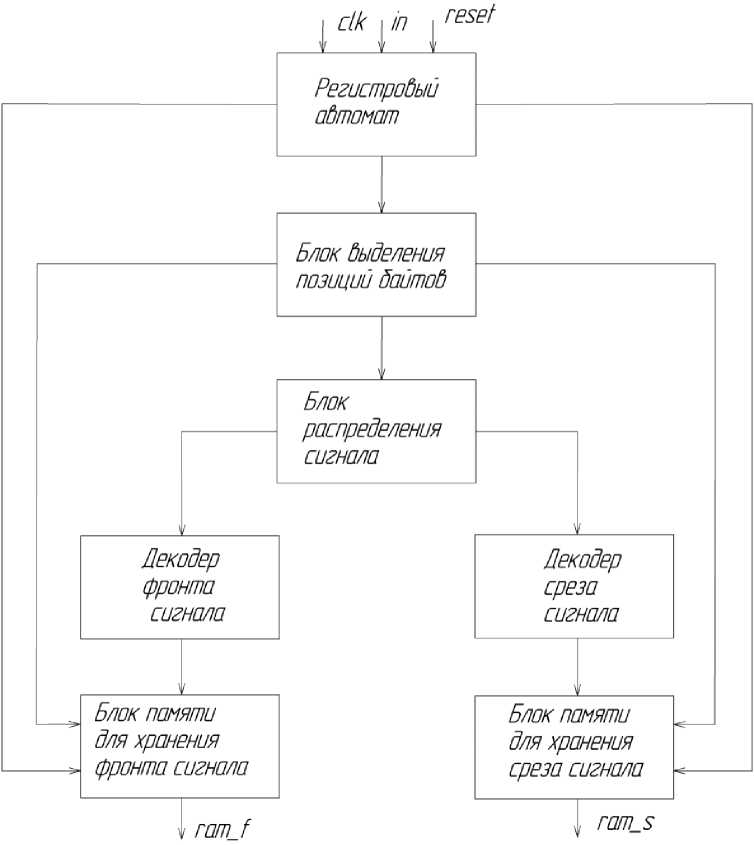

Р аз ра бота н ный к оде р с остои т из нескольких блоков, представленных на ри с. 4. Схема моде л и ров а н ия к одера п ри веде н а на ри с . 5.

Б л ок рег и ст ро во го автом ат а предназначен для выделения фронта и ср е з а входного сигнала in.

Блок вы д еле н и я п ози ц ии байтов состоит из сумматора и счетчика. Сумм а тор фик с и ру е т н о мер та к т а , к о гд а выд еле н фрон т и ли с ре з с игн а ла . С че тчи к выделяет позиции байтов входного си гнала. Пос ле н е го р а с полож е ны два сумматора, которые позволяют выделить п ози ц и и б а й тов в моме н т фик с аци и зн а ч е ни я с че тчика, и передают в блоки памяти для выделе н и я фрон та/с р е за сигнала.

Б л ок р а спред еления си гнал а со с т о ит из элемента LessThan, который определяет дальнейшее распределение сигнала. П ри появлении высокого уровня сигнала в деко д ер ф ронт а по сту п ает сиг н ал о выде лени е ф р онта, при низком уровне, в декодер среза сигн а л а – о выделении среза.

Блоки памяти для хранени я фронта/среза сигнала выполнены из стандар тных яче е к па мяти , с о е дине нных парал ле ль н о и пр едставленных в виде одного блока. Для кор р е кт ног о м оде л ир о в ания рег и ст ро во го автом ат а не обходима двухуровневая память для записи сч е тны х им пул ьсо в f и s. Данные о мес т о п о ло жении позиций фронта и среза приходят с блоков р ег и ст р о в о го авт о мат а и выде л ения по з иц ий бай т о в.

Для за п и с и к оли чес тв а п озиций используется глубина буфера записи, ко то ра я оп ре д ел яе тс я дли те льн о с тью в хо д н ого с и гн а ла и час тотой с ме ны сос тояни й . Обычн о глубину буфера принимают равной 75 % от ис х од н ой д ли ны, п ри 100 % глубине буфера (т. е. равной входному сигналу) г а ра н ти рована за п и с ь б е з потерь.

Рис. 4. Схема и временная диаграмма кодера

Рис. 5. Схема моделирования кодера

Заключение

Применение такого кодера позволит оптимизировать обработку информации только по изменению входного сигнала.

Реализация кодера на ПЛИС позволит упростить процесс разработки систем управления и обработки информации.

Список литературы Проектирование кодера PZ-сигналов методом регистрового автомата

- Крушный, В.В. Синтез цифровых управляющих автоматов/В.В. Крушный. -Снежинск: НИЯУ «МИФИ», 2010. -136 с.

- Шелухин, О.И. Сжатие аудио и видео информации: учеб. пособие/О.И. Шелухин, А.В. Гузеев. -М.: МТУСиИ, 2012. -87 с.

- Sivkov, S.I. Method of Identification and Diagnostics of Pulsed System Using Discrete Signal Convolution/S.I. Sivkov, L.G. Novikov, D.M. Mikhaylov//Journal of Theoretical and Applied Information Technology. -2014. -№ 3. -P. 844-850.