Разработка кластерного теста для электронного модуля с JTAG интерфейсом

Автор: Гречишников Владимир Михайлович, Бутько Алексей Дмитриевич, Лавров Андрей Юрьевич

Журнал: Известия Самарского научного центра Российской академии наук @izvestiya-ssc

Рубрика: Механика и машиностроение

Статья в выпуске: 6-2 т.17, 2015 года.

Бесплатный доступ

В работе рассмотрена возможность повышения тестового покрытия электронных модулей за счёт использования программных моделей, написанных на языке Python. Приведен пример реализации кластерного теста для диагностики электронного модуля ввода-вывода данных самолета.

Метод граничного сканирования, jtag-интерфейс, кластер

Короткий адрес: https://sciup.org/148204264

IDR: 148204264 | УДК: 681.518.5

Cluster development test for electronic module with JTAG port

The paper considers the possibility of increasing the test coverage of the electronic circuit boards through the use of modules written in Python. Example of realization of the functional test for the diagnosis of the electronic module I / o data of the aircraft «SuperJet 100».

Текст научной статьи Разработка кластерного теста для электронного модуля с JTAG интерфейсом

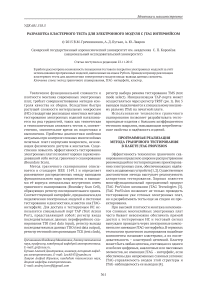

регистр выбора режима тестирования TMS (test mode select). Инициализация TAP-порта может осуществляться через регистр TRST (ри. 1). Все 5 выводов подключаются к специальному внешнему разъему JTAG на печатной плате.

Использование технологии граничного сканирования позволяет разрабатывать тестопригодные изделия с большим коэффициентом тестового покрытия, повышающим потребительские свойства и надёжность изделий.

ПРОГРАММНАЯ РЕАЛИЗАЦИЯ МЕТОДА ГРАНИЧНОГО ТЕСТИРОВАНИЯ В ПАКЕТЕ JTAG PROVISION

Эффективность технологии граничного сканирования определило широкое распространение рекомендаций по тестопригодному проектированию электронных схем, обеспечивающих надёжность создаваемых устройств [1, 2]. Существенным достоинством метода выступает реализуемость алгоритмов тестирования. Хорошо известен многофункциональный программный продукт JTAG ProVision компании JTAG Tecnologies [3]. JTAG ProVision позволяет не только проводить тестирование уже готовых электронных плат, но и разрабатывать тесты еще на стадии их проектирования.

При высокой плотности монтажа компонентов сложных многослойных электронных плат часто бывает невозможно обеспечить прямой доступ к тестируемым ИС и тестовый сигнал вынужден проходить через электронные компоненты не имеющие JTAG-интерфейса. В терминах технологии граничного сканирования подобные компоненты называют кластерами, а их последовательность – кластерной цепочкой. Кластер может быть любая цепочка, состоящая из одного или более цифровых, аналоговых или пассивных элементов, не имеющих JTAG - интерфейс, если обеспечены два непременных схемных условия: JTAG-управляемость входов этой структуры и JTAG-наблюдаемость ее выходов [4].

ESC

■»BSC

BSR

РЕГИСТРЫ

4* BSC

TDI ■ (Data In)

TAP -контроллер (ПАО]

Функциональное ■ ядро ■ микросхемы

TCK

(Clock) — TMS ■

(Contlol) ■ TR5T (Reset)

{мреТРО

(Data Out)

Рис. 1. BS-микросхема с элементами граничного сканирования

Как показывает практика, включение тестов для кластеров позволяет повысить тестовое покрытие изделия. Даже если на тестируемой плате всего один компонент, поддерживающий периферийное сканирование, он может быть окружен всевозможными кластерами, которые легко можно продиагностировать.

ПРОБЛЕМЫ, ВОЗНИКАЮЩИЕ ПРИ ТЕСТИРОВАНИИ ЭЛЕКТРОННЫХ ПЛАТ С КЛАСТЕРАМИ

Программный пакет JTAG ProVision позволяет построить и реализовать тест даже в том случае, когда отсутствует прямой доступ к JTAG-компонентам. В работе описан классический подход на основе генерации модели компонента и функциональный подход, заключающийся в разработке собственного тестового модуля, написанного на языке Python.

Широкие возможности программного пакета JTAG ProVision позволяет использовать оба принципа тестирования при диагностике электронного модуля ввода-вывода данных самолета. Модуль предназначен для обеспечения достоверности выдаваемых данных за счет сравнения данных, подготовленных различными вычислительными устройствами и способен принимать и выдавать информацию по линиям связи.

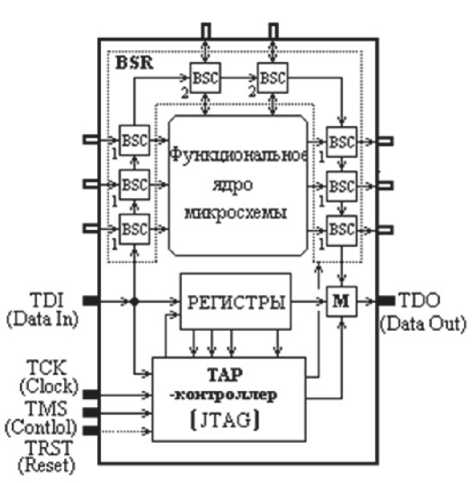

В состав электронной платы включены три ПЛИС Altera Cyclone III, имеющие JTAG-интерфейс и выводы, позволяющие подключить TAP-контроллер, связанный с компьютером. Используя встроенные возможности JTAG ProVision, были разработаны тесты для диагностируемой платы, однако вследствие наличия в схеме кластерных цепочек ряд тестов выполнить не удалось. В процессе разработки тестов было установлено, что цифровые сигналы, формируемые микросхемой D5, невозможно напрямую подать на D2, так как D2 связана с D5 только выходами. Чтобы послать на неё тестовый вектор, были использованы буферные микросхемы D17–D21, соединённые с входом микросхемы D5 и внешними выводами электронного модуля на разъеме X1(рис. 2). Соединением определённых выводов разъёма Х1 можно подать сигналы на вход D2 по пяти каналам из буферных микросхем. С выхода D2 сигнал напрямую возвращается на микросхему D5, где и происходит сравнение его с исходным тестовым вектором.

Рис. 2. Связь микросхемы D2 по пяти каналам через разъем Х1

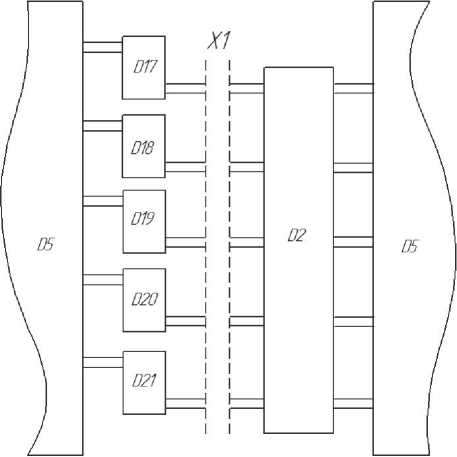

В качестве примера рассмотрим передачу сигнала по второму каналу. Из микросхемы D5 сигнал поступает на вторую буферную микросхему D18. Выходы D18 имеют внешние выводы на разъёме X1 (№52 и 114). На этот же разъём выведены входные контакты микросхемы D2 (№223 и 161). Таким образом, соединив выходные контакты D18 с соответствующими им входными с микросхемы D2, как показано на рис. 3, можно передать тестовый вектор с D5 на D2.

ПРИМЕР ПОСТРОЕНИЯ КЛАСТЕРНОГО ТЕСТА

Программное обеспечение JTAG ProVision позволяет включать в тесты внешние модули представляющие собой программы написанные на языке высокого уровня Python 3. Для этого в состав пакета включен специальный модуль JFT, реализующий программный интерфейс доступа к контролируемым компонентам. Модуль импортируется стандартной командой Python 3,

Рис. 3. Схема тестирования кластера по второму каналу

import JFT, после чего все его возможности доступны из программного пакета. Предустановленные библиотеки с функциями позволяют использовать названия или номера выводов JTAG компонентов и устанавливать или считывать с них значения, записывая их при необходимости в переменные, а также оперировать сразу группами выводов.

Разработанный модуль представляет собой функциональное описание кластера. Алгоритм цифровой обработки входного и выходного сигналов программируется для каждого канала в отдельности, а затем объединяется между собой в последовательность тестов. Ниже показан фрагмент модуля, содержащий функцию обработки сигналов по второму каналу.

На вход подается исходный тестовый вектор, а с выхода считывается результирующий вектор. Идентичность результирующего и исходного векторов указывает на отсутствие дефектов кластера. Различие векторов указывает на дефект в линии связи кластера и JTAG-микросхемы, тип которого позже может быть идентифицирован. Текст программного модуля для второго канала приведен ниже.

-

# Подпрограмма, для передачи и приёма тестового вектора

def Test(vector):

-

# обнуление счётчика ошибочно принятых символов тестового вектора

err = 0

-

# цикл для последовательной передачи символов тестового вектора

for x in range (0, len(vector)):

-

# разбивка тестового вектора на отдельные символы

v=int(vector[x])

-

# передача конкретной логической последовательности из таблицы истинности микросхем D18 и D2 в зависимости от введённого в подпрограмму символа

if v==0: jft.DriveGroup(«Input», 0b001)

-

# передача «NULL»

elif v==1: jft.DriveGroup(«Input», 0b011)

-

# передача «ZERO»

elif v==2: jft.DriveGroup(«Input», 0b101)

-

# передача «ONE»

-

# приём сигналов, прошедших через кластер и вернувшихся в микросхему D5

y=jft.GetGroup(“Output”)

-

# проверка совпадения отправленного и принятого символа тестового вектора

if y != v:

-

# при ошибке передачи инкрементируется счётчик ошибок

err += 1

-

# вывод сообщения об ошибке или об удачной передаче символа

print («Error in transmitting symbol», x, «of the test vector»)

else: print (y, «- Symbol», x, «transmitted correctly»)

-

# подпрограмма возвращает в основную программу число ошибок при передаче символа return err

Аналогично диагностируются остальные четыре канала.

Основное принципиальное отличие JFT от классического подхода — это то, что алгоритм автоматической генерации заменяется в данном случае на самостоятельно написанный программистом скрипт.

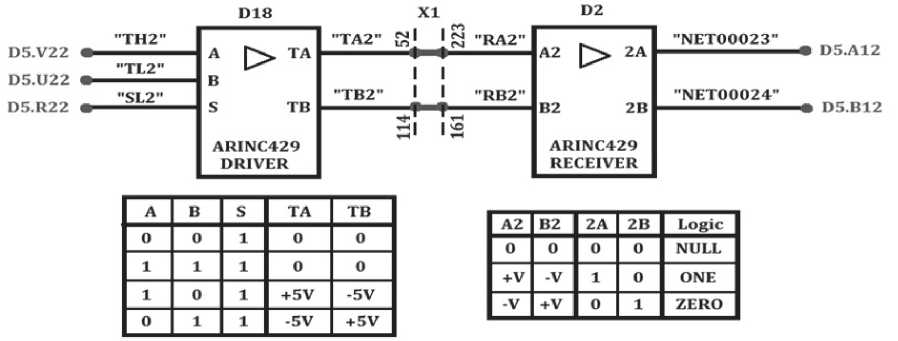

В результате использования JFT - модуля при построении кластерного теста для всех пяти каналов реальное покрытие печатной платы увеличилось на 3%. На рис. 4 показан отчёт, формируемый JTAG ProVision по завершении тестов. Слева изображено покрытие платы без разработанного Python-модуля тестового приложения, а справа с его использованием.

ВЫВОДЫ

Необходимость качественной и полной диагностики электронных плат ставит перед специалистами сложные задачи разработки

|

Net Statistics | Testability | % | Coverage | % |

Net Statistics | Testability | % | Coverage | % | |

|

|

Total number of nets calculated 1079 100% 1079 100% Netsm Nethst 269 269 Nets added for not connected pns (♦) 810 810 Nets ignored by user (-) 0 0 Sensed and driven nets 885 82% 855 79% Sensed by BSCAN device (direct) 847 826 Sensed through transp device (indirect) 21 12 Sensed Pwr / Gnd nets 4 4 Implicitly tested nets 13 13 Nets Covered 100% by user 0 Nets Covered by JET 0 Nets Covered by Imported CSV File 0 Nets not tested by BSCAN 194 18% 224 21% |

Total number of nets calculated 1079 100% 1079 100%. Nets in Nethst 269 269 Nets added for not connected pns (♦) 810 810 Nets ignored by user (-) 0 0 Sensed and driven nets 885 82% 881 82% Sensed by BSCAN device (drect) 847 828 Sensed through transp device Indirect) 21 2 Sensed Pwr / Gnd nets 4 4 Implicitly tested nets 13 13 Nets Covered 1007. by user 0 Nets Covered by JFT 34 Nets Covered by Imported CSV File 0 Nets not tested by BSCAN 194 18% 198 18% |

Рис. 4. Сравнение реального покрытия до и после применения кластерного тестирования

тестов. Программные продукты и аппаратные комплексы, реализующие технологию граничного сканирования, охватывают широкий спектр вопросов диагностики. Однако компактность размещения компонентов на плате и отсутствие прямого доступа к контролируемым точкам может вызвать существенные затруднения. В этом случае может оказать помощь дополнительные программные модули, разрабатываемые под конкретные кластерные цепочки. Создавая подобные модули для неизвестных программе участков платы, можно существенно увеличить её тестовое покрытие.

Список литературы Разработка кластерного теста для электронного модуля с JTAG интерфейсом

- Иванов, А В. Ключевые моменты тестопригодной разработки/А.В. Иванов//Электронные компоненты. -2010. -№ 18. С. 4-8.

- Городецкий А. А. JTAG тестирование кластеров/. А. А. Городецкий//Компоненты и технологии. -2010. -№1. С. 38-39.

- Гречишников В. М. Многофункциональные пакеты программ граничного сканирования/А. Д. Бутько//XII королевские чтения -2013. -Том 2. С. 116-117.

- Иванов, А В. Два подхода к тестированию кластеров в технологии периферийного сканирования/А.В. Иванов//Компоненты и технологии. -2011. -№10. С. 203-206.