Разработка приемопередатчика дифференциальных сигналов по стандарту LVDS с использованием технологии КМОП 180нм

Автор: Калнов А.Д., Лосев В.В.

Журнал: Международный журнал гуманитарных и естественных наук @intjournal

Рубрика: Технические науки

Статья в выпуске: 11-4 (86), 2023 года.

Бесплатный доступ

С развитием технологии интегральных схем и повышением производительности коммуникационных, сетевых и компьютерных систем потребность в более высокой скорости передачи данных и передаче на большие расстояния по кабелю становится все более актуальной. Передатчик LVDS-TX совместно приемником LVDS-RX реализуют высокоскоростной последовательный интерфейс в стандартах ANSI/TIA/EIA-644A и IEEE 1596.3 и разработан для технологического процесса КМОП 180нм. Предназначен для широкого круга применений с последовательной передачей данных в соединениях типа «точка-точка» по различным типам линий с волновым сопротивлением около 100 Ом, включая трассы на печатной плате и витые пары со скоростью 500 Мбит/с и током потребления не более 3,5 мА.

Дифференциальный сигнал, интегральная схема

Короткий адрес: https://sciup.org/170201452

IDR: 170201452 | DOI: 10.24412/2500-1000-2023-11-4-59-63

Development of a differential signal transceiver according to the LVDS standard based on CMOS 180nm technology

With the development of integrated circuit technology and the increased performance of communication, network and computer systems, the need for higher data transfer rates and long-distance transmission over cable is becoming more urgent. The LVDS-TX transmitter together with the LVDS-RX receiver implement a high-speed serial interface in the ANSI/TIA/EIA-644A and IEEE 1596.3 standards and is designed for the CMOS 180nm process. It is designed for a wide range of applications with serial data transmission in point-to-point connections over various types of lines with a wave resistance of about 100 ohms, including circuits on a printed circuit board and twisted pairs with a speed of 500 Mbit/s and a consumption current of no more than 3.5 mA.

Текст научной статьи Разработка приемопередатчика дифференциальных сигналов по стандарту LVDS с использованием технологии КМОП 180нм

Для минимизации рассеиваемой мощности LVDS имеет режим пониженного напряжения передачи (250 мВ – 400 мВт). Дифференциальный режим передачи необходим для повышения устойчивости к скачкам синфазного напряжения и перекрестным помехам, а также для снижения уровня шума при передаче информации [3, с. 704]. Однако, поскольку скорость передачи данных быстро увеличивается, дрейф данных и «дрожание» данных из-за производственных дефектов, шума окружающей среды, перекрестных помех и т.д. затруднят восстановление переданных данных приемником LVDS [2, с. 70]. Для обнаружения и восстановления данных, тактовой ошибки потребуется резервная схема и большая площадь. Но отказоустойчивые архитектуры и схемы с тактовой частотой и данными по-прежнему являются важной методологией решения проблем при проектировании и производстве интегральных схем.

Таким образом, разработка высокопроизводительного с низким энергопотреблением приемопередатчика LVDS очень важна для увеличения надежности и стоимости системы [1, с. 263]. Для того чтобы удовлетворить недавний спрос на широкую полосу пропускания, разработан приемопередатчик LVDS с приемником 500 Мбит/с и передатчиком 500 Мбит/с.

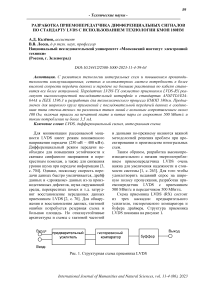

Схема приемника LVDS (RX) состоит из трех каскадов: предварительного усилителя, гистерезисного компаратора и буфера драйвера. Структура приемника LVDS показана на рисунке 1.

Рис. 1. Структурная схема приемника LVDS

Амплитуда дифференциальных сигналов низкого напряжения и синфазного выходного напряжения будет уменьшаться при прохождении большого расстояния по кабелю, и тогда приемник должен сначала усилить дифференциальный сигнал низкого напряжения. Схема предусилителя представляет собой каскадный усилитель со входом дифференциальной пары NMOS и PMOS для реализации синфазного входного диапазона rail-to-rail (выходной сигнал с размахом, равным напряжению питания) [4, с. 100].

Коэффициент усиления предусилителя составляет около 10 дБ, а полоса пропускания -3 дБ составляет 1 ГГц. Гистерезисный компаратор преобразует усиленные дифференциальные сигналы низкого напряжения в цифровой выходной сигнал. Функция гистерезиса используется для устранения эффекта колебаний выходного сигнала, который возникает из-за нестабильности входного сигнала. В соответствии с критерием LVDS напряжение гистерезиса установлено равным 25 мВ, и спроектировано таким образом, что на него не влияет процесс изготовления, температура и синфазное напряжение. Токи смещения и, скорость отклика, напряже- ние смещения и скорость нарастания – это не менее важные показатели производительности, которые следует тщательно учитывать [5, с. 1320].

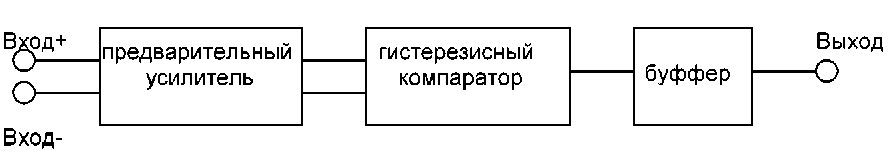

Схема передатчика LVDS (TX) состоит из двух каскадов: предварительного буфера и схемы драйвера, которая показана рисунке 2. Схема создания опорного напряжения требуется для реализации постоянного напряжения, которое не зависит от процесса, температуры и изменения напряжения питания. Предварительный буфер увеличивает возможности формирователя цифрового сигнала для управления схемой формирователя LVDS сигналов. Сигналы LVDS генерируются схемой формирователя. Схема драйвера LVDS является наиболее важной из схемы передатчика. Он работает как источник тока с переключаемой полярностью. Схема драйвера работает более стабильно в режиме двойного источника тока. Синфазное выходное напряжение будет смещаться из-за практически неидеальных линий передачи и паразитного эффекта связанных с контактными площадками, поэтому добавлена синфазная схема обратной связи, чтобы стабильно повышать общее выходное напряжение до 1,2 В.

Рис. 2. Структурная схема приемника LVDS

Ток через драйвер устанавливается равным 3,5 мА с помощью внутренней токовой зеркальной схемы. Разность напряжений между сигналами OUT_plus и OUT_minus составляет +350 мВ или минус 350 мВ. Устанавливается дифференциальное колебание выходного напряжения.

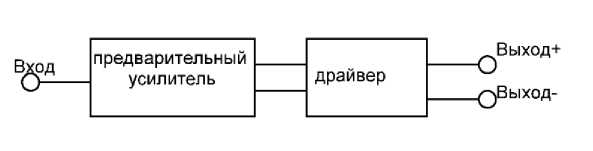

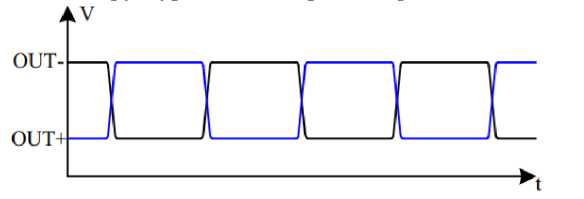

Приемопередатчик LVDS состоит из схемы приёмника RX и схемы передатчика TX. На рисунке 3 показана стандартная архитектура приемопередатчика LVDS с передачей данных "точка-точка". Схема передатчика преобразует цифровой сигнал в низковольтные дифференциальные выходные сигналы. Разница между выходным сигналом VOUT+ и VOUT- составляет примерно 250~400 мВ, а синфазное выходное напряжение составляет 1,125~1,275 В. На рисунке 4 показаны стандартные формы выходного сигнала схемы TX.

Рис. 3. Структурная схема приемопередатчика LVDS

Рис. 4. Выходные сигналы (Vout+ и Vout-) приёмопередатчика LVDS

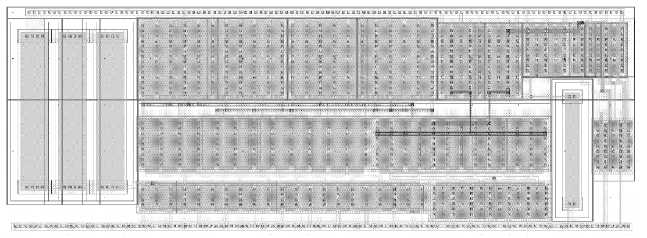

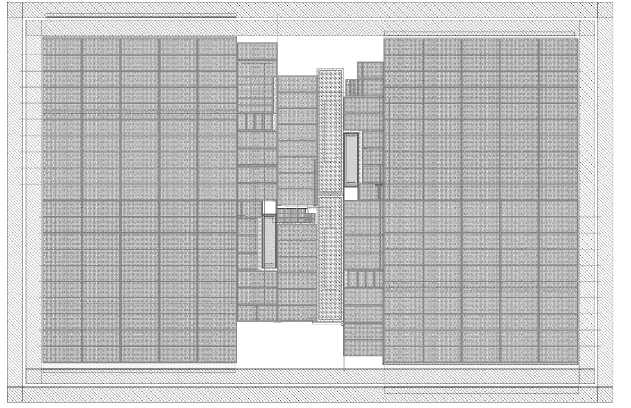

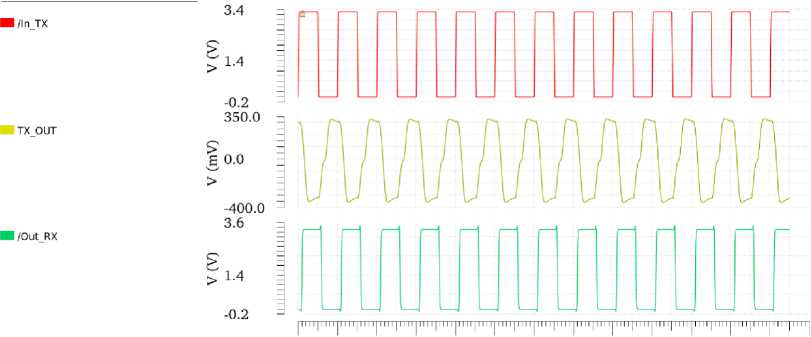

Схема приемопередатчика LVDS разработана с использованием КМОП-технологии 0,18 мкм с использованием шести металлических слоёв. На рисунке 5 показана топологическое представление схемы передатчика и приемника LVDS. Чтобы оценить точную работу схемы приемопередатчика LVDS, схема моделируется с помощью программного обеспечения Cadence Spectre. На рисунке 6 показаны сигналы LVDS подключенных цепей TX и RX со скоростью передачи данных 500 Мбит/с. Время задержки выходных сигналов LVDS в цепи TX составляет примерно 0,75 нс. Время задержки в цепи RX составляет 1,75 нс. Общее энергопотребление цепей TX и RX составляет 26 мВт и 12 мВт при скорости передачи данных 500 Мбит/с соответственно.

а)

б)

Рис. 5. Топологическое представление приемопередатчика LVDS (а – приемник, б – передатчик)

Результат моделирования во временной области приемника и передатчика LVDS-сигналов, спроектированного на отечественной технологии КМОП HCMOS8D 180нм показан на рисунке 6.

Name

0.0 4.0 8.0 12.0 16.0 20.0 24.0 26.0

time (ns)

Рис. 6. Результаты моделирования приемопередатчика LVDS

Применение LVDS технологии позволяет достичь высокой скорости передачи данных на дальние расстояния, совместно с малыми затратами при производстве на технологии 180 нм.

Работа выполнена с использованием технологического сервиса MPW, реализуемого НИУ МИЭТ в рамках прикладной научно-исследовательской работы «Разра ботка методики прототипирования элек тронной компонентой базы на отечествен ных микроэлектронных производствах на основе сервиса MPW (FSMR-2023-0008)» в соответствии с федеральным проектом «Подготовка кадров и научного фундамента для электронной промышленности».

Список литературы Разработка приемопередатчика дифференциальных сигналов по стандарту LVDS с использованием технологии КМОП 180нм

- Abugharbieh K., Krishnan S., Mohan J., Devnath V. and Duzevik I. An Ultra low-Power 10-Gbits/s LVDS Output Driver // Circuits and Systems I: IEEE Transactions on Regular Papers. - 2010. - Vol. 57, № 1. - Pp. 262-269.

- Bozomitu R.G., Cehan V., Barabasa C. A VLSI implementation of a 3Gb/s LVDS transceiver in CMOS technology // 15th International Symposium for Design and Technology of Electronics Packages. - 2009. - Pp. 69-74.

- Lee Jaeseo, Lim Jae-Won, Song Sung-Jun, Song Sung-Sik, Lee Wangjoo and Yoo Hoi-Jun. Design and implementation of CMOS LVDS 2.5 Gb/s transmitter and 1.3 Gb/s receiver for optical interconnections // The 2001 IEEE International Symposium on Circuits and Systems. - 2001. - Vol. 4. - Pp. 702-705.

- Razavi B. Challenges in the design high-speed clock and data recovery circuits // IEEE Communications Magazine. - 2002. - Vol. 40, № 8. - Pp. 94-101.

- Wang Chua-Chin, Lee Ching-Li, Hsiao Chun-Yang and Huang Jin-Fon. Clock-and-Data Recovery Design for LVDS Transceiver Used in LCD Panels // Circuits and Systems II: IEEE Transactions on Express Briefs. - 2006. - Vol. 53. - № 11. - Pp. 1318-1322.