An Energy-Efficient and Robust Voltage Level Converter for Nanoelectronics

Автор: Behzad Alidoosti, Mohammad Hossein Moaiyeri

Журнал: International Journal of Modern Education and Computer Science (IJMECS) @ijmecs

Статья в выпуске: 5 vol.7, 2015 года.

Бесплатный доступ

Low-power design has recently become very important especially in nanoelectronic VLSI circuits and systems. Functioning of circuits at ultra-low voltages leads to lower power consumption per operation. An efficient method is to separate the logic blocks based on their performance requirement and applying a specific supply voltage for each block. In order to prevent an enormous static current in these multi-VDD circuits, voltage level converters are essential. This study presents an energy-efficient and robust single-supply level converter (SSLC) based on multi-threshold carbon nanotube FETs (CNTFETs). Unique characteristics of the CNTFET device and transistor stacking are utilized suitably to reduce the power and energy consumption of the proposed LC. The results of the extensive simulations, conducted using 32nm CNTFET technology of Stanford University indicate the superiority of the proposed design in terms energy-efficiency and robustness to process, voltage and temperature variations, as compared to the other conventional and state-of-the-art LC circuits, previously presented in the literature. The results demonstrate almost on average 35%, 55%, 90% and 68% improvements in terms of delay, total power, static power and energy consumption, respectively.

Nanoelectronics, Carbon nanotube field effect transistor (CNTFET), Low-power design, Voltage level converter

Короткий адрес: https://sciup.org/15014753

IDR: 15014753

Текст научной статьи An Energy-Efficient and Robust Voltage Level Converter for Nanoelectronics

Published Online May 2015 in MECS DOI: 10.5815/ijmecs.2015.05.01

Low-power design has recently become very important in digital integrated circuits for ultra-low power applications. Function of circuits at ultra-low voltages significantly reduces power consumption. In applications such as micro- and nano-sensors, radio frequency identification and medical instruments implanted in the body battery lifetime is more important than performance. Since the lifetime of battery depends on the average power dissipated by the system, the power supply voltage should be lowered in these applications which leads to considerable reduction of power consumption. An efficient technique is to separate the blocks of the circuits based on the required performance and utilize different suitable supply voltages for the blocks. This is an effective approach for lowering the power consumption without degrading the minimum required performance of a VLSI system. [1]. In VLSI designs with multiple supply voltages (multi-VDD) the signals from the high-VDD (VDDH) island can enter the low-VDD (VDDL) island without any problem. However, there can be a relatively high static current in multi-VDD circuits when a signal with logic '1' from the VDDL island enters the VDDH island and consequently the pull-up network of the input stage in the VDDH area will be weakly ON. In this situation, there is a necessity for a voltage level converter as an interface between VDDL and VDDH islands. Therefore, design of energy-efficient voltage level converters is an important challenge in multi-VDD designs [2].

In addition, another effective low-power design technique at the circuit level is device stacking. In this technique the subthreshold leakage current passes through a stack of transistors which are connected serially. Accordingly, the subthreshold leakage current is considerably reduced due to increasing the effective channel length, suppressing the drain induced barrier lowering and higher VSB which increase the threshold voltage of the stacked device in the OFF state [2].

In addition, scaling down the feature size of MOSFET leads to difficulties such as high leakage current, short channel effects, reduced gate control and high power density. To conquer these serious challenges and physical limitations some alternative nanodevices such as carbon nanotube field-effect transistor (CNTFET), nanowire field-effect transistors (NWFET), Graphene nanoribbon field effect transistor (GNRFET), single electron transistor (SET) and quantum cellular automata (QCA) have been introduced and investigated in the literature [37].

Considering these nanodevices, CNTFET seem to be a more feasible alternative due to its operational and structural similarity with MOSFET.

In this study, a CNTFET single supply voltage level converter is proposed which benefits from the unique features of the CNTFET nanodevice such as multiple threshold voltages as well as circuit level low-power design techniques such as transistor stacking.

The rest of the paper is organized as follows: Section II briefly describes the characteristics of CNTFET technology. In Section III, the previous LC designs are reviewed. Section IV describes the proposed SSLC design. Section V includes the simulation results and comparisons and finally section VI concludes the paper.

-

II. A Brief Review Of Cntfet Technology

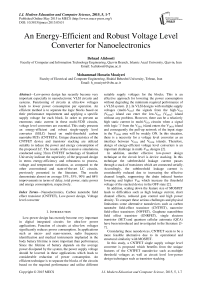

Carbon nanotube (CNT) is an allotrope of carbon with a cylindrical structure of graphene sheets bent to form a tube which has unique electrical and mechanical properties. CNT is fabricated in two forms of singlewalled CNT (SWCNT) and the multi-walled CNT (MWCNT). The arrangement of carbon atoms in a SWCNT is determined with a two dimensional vector called the chiral vector, which is defined according to equation 1 [8].

Ch = n.vx + n.v2 (1)

In this regard, a and a are unit vectors and the n1 and n2 are positive integers which defines some important characteristics of a CNT. Chiral vector has a decisive role in making a CNT metallic or semiconductor. If n 1 - n 2| =3k (k e z ) the CNT becomes metallic and otherwise it becomes semiconductor which can be used as the channels region of a transistor. As the size of the chiral vector of a CNT is equal to its base perimeter, the diameter of the CNT is calculated according to equation 2 [8].

3Vvn Jn 2 + n n + n

D^ = v 0^ 1 ---12---2_ - 0.0783d\ 2 + nn + n2 (2)

n v

Where, a 0 = 0.142 nm is the bond length of carbon atoms in a CNT. The current-voltage characteristics of CNTFET are very similar to MOSFET and it has also a threshold voltage which can be calculated by equation 3 [8].

Vth

Eg dav^ ~ 0.43

2e 3eDCNT DCNT (nm)

Where, e is the charge of an electron and Vπ (≈3.033 eV) is the carbon π–π bond energy in the tight bonding model. Three types of CNTFET including CNTFET the band to band tunneling CNTFET (T-CNTFET), Schottky barrier CNTFET (SB-CNTFET) and the MOSFET-like CNTFET [9]. SB-CNTFET shows ambipolar characteristics and has metal source and drain regions and hence there is a large Schottky barrier between the intrinsic CNT channel and metal S/D regions which restrict the usefulness of this device for high-performance and low-power applications. In addition, T-CNTFET operates based on band-to-band tunneling and has a limited ON current. However, MOSFET-like CNTFET demonstrates unipolar behavior. In this device, the source and drain regions are heavily doped CNTs and the CNTFET operates on the principle of barrier height modulation by applying of the gate potential. The conductivity of the channel of MOSFET-like CNTFET is modulated by the gate-source bias [9]. It is also notable that the electron and hole have the same mobility in the CNT structure.

According to equations 2 and 3 by setting a specific CNT diameter based on a specific chirality, determined by the chirality numbers (nbn2), the electrical conductivity and the bandgap of CNTs and consequently the threshold voltage of the CNTFET can be defined. It is worth mentioning that many effective and achievable solutions have already been presented in the literature for growing CNTs with specific chirality and setting the desired threshold voltage for multi-tube CNTFETs [10,11]. In addition, in [12], fabrication of imperfection-immune VLSI-compatible sequential and combinational CNTFET logic circuits has been reported.

Fig. 1. Schematic of a MOSFET-like CNTFET

-

III. A Review Of The Previous Works

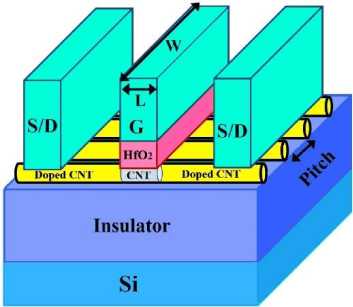

The dual-supply LC (DSLC) [13], shown in Fig.2(a), is a cross-coupled voltage level converter which requires dual supply voltages, which can increase the complexity of the circuit. In DSLC when the input signal is at logic "0", although the M5 and M3 transistor are ON and charge the node "Q1", the total charged voltage is lower than V DDH . This is because, when the voltage at node "Q1" crosses the switching threshold voltage of the output inverter, the output voltage of inverter (Out) begins to discharge. As a result, before the voltage of node "Q1" reaches V DDH , the output voltage becomes zero. Therefore, the M7 transistor completely turns OFF which makes M11 to be turned OFF and hence, M5 also becomes OFF. In this situation, the node "Q1" is not continuously charged to reach V DDH . However, this incomplete voltage of node "Q1" which is lower than V DDH cannot turn OFF the pMOS transistor of this inverter. Therefore, static power dissipation is increased, and this condition becomes worse by scaling down the technology feature size.

Fig.2(b) demonstrates a single supply LC [14] which uses the stacking technique in its both input and output stages, which reduces the power consumption but increases the delay and area. However, the PDP will not be improved considerably.

The conventional SSLC design [15] shown in Fig.2(c) does not work properly in low voltages especially in the sub-threshold region. In the sub-threshold region, as the gate voltage is lowered, drive current of transistors reduces exponentially. When the input is a low-voltage signal, in the conventional LC, pull-down strength of M1 transistor is weak as compared to the strength of the pull-up transistor (M2). In addition, increasing the gate width of M1 is not adequate for a correct conversion. Moreover, in this design, as the input signal is connected to the gate of p-type and n-type transistors (M1, M2), in low input voltages, both M1 and M2 turn ON, and consequently the static current is increased.

The SSLC design demonstrated in Fig.2(d) [16] utilizes static body-biasing for input n-type transistors to reduce the power consumption. However, this dictates the requirement for separated bodies for these transistors to avoid latch-up problem which destroy the reliability. In addition, the possible presence of overshoot of the voltage (during transitions) can potentially causing the pn-junction diode to be asserted. It is worth mentioning that all the previous LC circuits are redesigned and optimized using CNTFET technology for a fairer comparison.

Fig. 2. Previous conventional and state-of-the-art LCs (a) [13] (b) [14] (c) [15] (d) [16]

-

IV. The Proposed Cntfet-Based Sslc

While, the voltage level converters has a significant role in multi-VDD low-power designs they occupy redundant area on integrated circuits and can impact their overall performance and energy-efficiency. However, while decreasing the power consumption, the minimum required performance of the system should be provided. Therefore, design of a robust LC with very low static power dissipation, lower number of transistors and high performance is an important challenge.

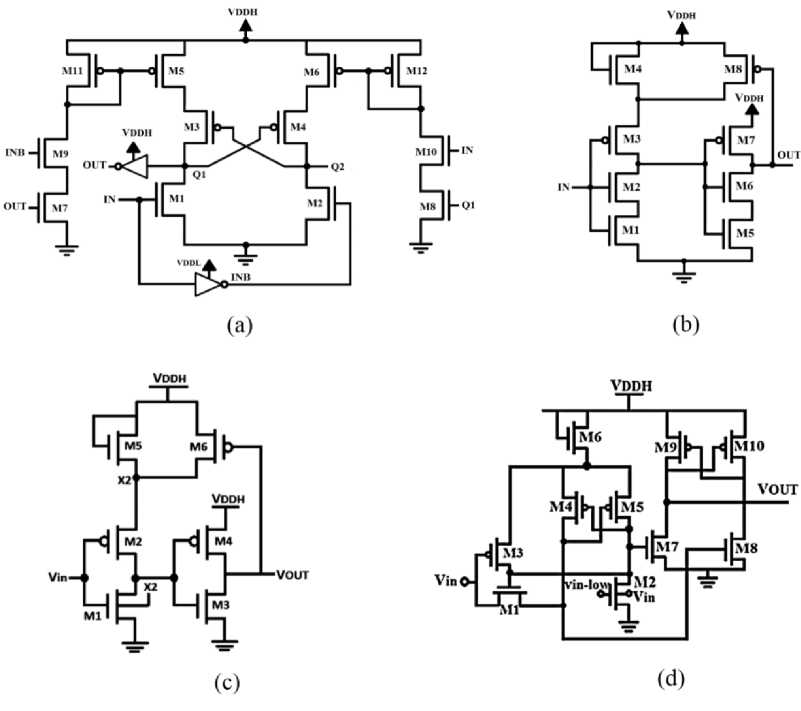

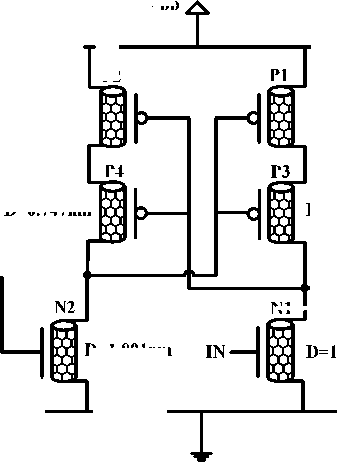

The proposed CNTFET-based SSLC designed based on the Differential Cascode Voltage Switch Logic

(DCVSL) is shown in Fig.3. In this design cross-coupled p-type transistors (P1-P4) provide a positive feedback which increase the performance of the circuit. However, in order to reduce the power consumption and to make a trade-off between performance and power consumption stacking technique is utilized in the cross-coupled devices, which leads to a considerable energy efficiency. In addition, using stacking technique and reducing the diameter of the cross-couple transistors considerably enhance the stability and robustness of the proposed DCVSL level converter circuit

P5

IN

N3

D=0.747nm D=0.747nm

V DD

P2

D=0.747nm

P4

P3

N1

D=0.747nm

D=0.747nm

Fig. 3. The proposed level converter

D=1.801nm

P6

D=0.747nm

N4

D=1.801nm

OUT

Moreover, as in this design both of low-voltage input signal and its inverse are required, an inverter is utilized (P5 and N3). However, by connecting the low-voltage signal (V

in

<

It is worth mentioning that for designing the proposed circuit, only two different CNT diameters, all less than 2 nm, are used. Moreover, all the p-type devices have the same diameter and all the n-type devices have also the same diameter. These features reduce the complexity of the proposed design and considerably enhance its VLSI compatibility and manufacturability.

-

V. Simulations Results And Comparison

This section examines the proposed SSLC as well as the previous LC designs [13-16] based on the comprehensive MOSFET-like CNTFET SPICE model provided by Stanford University [8] at 32nm technology node. In order to make a fair comparison all of the previous designs are also optimized using the CNTFET technology. The simulation results given in Table 1 demonstrate the overall superiority of the proposed designs as compared to the other conventional and state-of-the-art level converters. It is notable that the cross coupled pull-up devices and the output inverter lead to lower delay and the stacking the pull-up devices reduces the overall power consumption of the proposed design. In addition, the LC of [14] requires double supply voltages while the other designs needs a single supply voltage.

Table 1. The simulation results of the level converters (V DDH =1V and C load =1fF)

|

LC |

Delay (ps) |

Total Power (nW) |

Static Power (nW) |

PDP (aJ) |

|

V DDL = 0.6V |

||||

|

Proposed |

16.4 |

181 |

6.45 |

2.96 |

|

[13] |

17.7 |

230 |

3.21 |

4.09 |

|

[14] |

36.8 |

478 |

371 |

17.6 |

|

[15] |

33.6 |

573 |

382 |

19.3 |

|

[16] |

23.9 |

679 |

410 |

16.2 |

|

V DDL = 0.7V |

||||

|

Proposed |

16.2 |

186 |

5.41 |

3.01 |

|

[13] |

15.4 |

257 |

3.01 |

3.96 |

|

[14] |

36.6 |

610 |

496 |

22.3 |

|

[15] |

33.1 |

700 |

566 |

23.1 |

|

[16] |

21.5 |

794 |

478 |

17.1 |

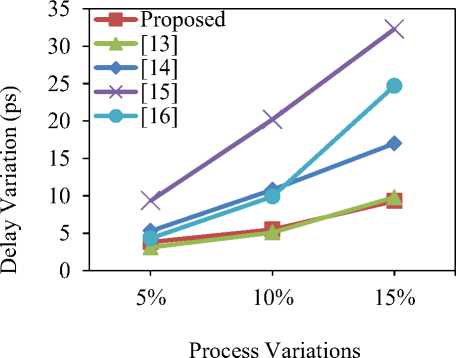

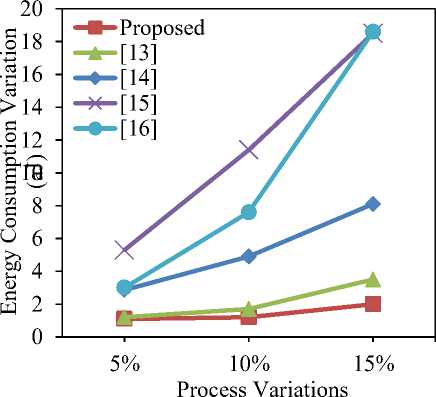

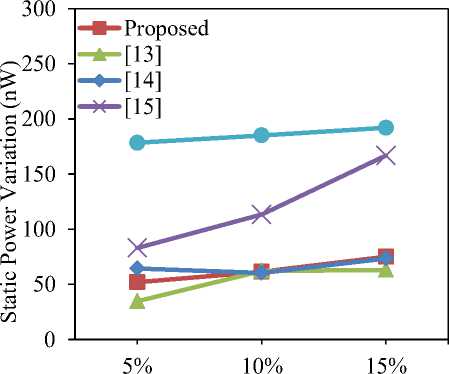

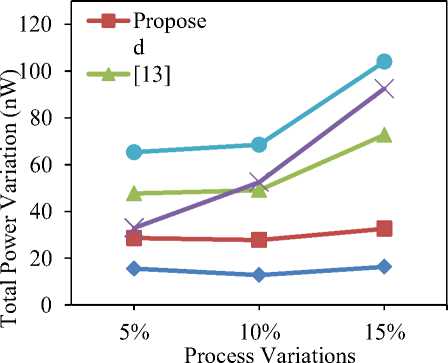

One of the most significant challenges in nanoscale devices and circuits is sensitivity to random process variations, which can degrade the performance, energy efficiency and stability of the circuits. As the diameter of CNTs under the gate dominantly determine the threshold voltage of a CNTFET device, the function of CNTFET-based designs should be investigated in the presence of CNT diameter variations. Furthermore, variations of the number of CNT under the gate, principally caused by variations in the pitch of CNTs grown on the substrate as well as the variation of the number of surviving CNTs after metallic CNT removal techniques, is proven experimentally to be the dominant source of variation in CNTFET circuits [17]. Accordingly, MonteCarlo transient analysis has been performed to assess these process variations with ±5% to ±15% Gaussian distributions and variation at the ±3σ level.

The maximum variations of the parameters of the LC circuits are shown in Fig.4. The results demonstrate that the proposed cell operate correctly with small parametric variations even in the presence of intensive process variations.

Process Variations

Fig. 4. Parametric variations of the level converters in the presence of major process variations

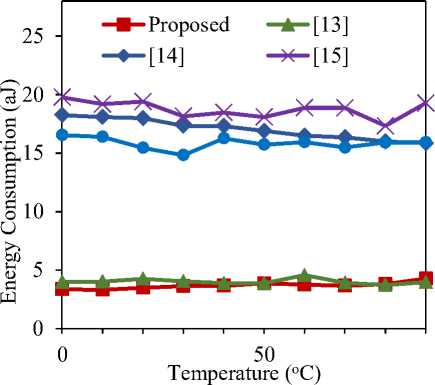

Temperature variations deviates the performance parameter of the circuits from the expected values and alternate the subthreshold swing and static currents of the devices. Hence, the designs are simulated at a wide range of temperatures from 0oC up to 90oC, to examine their sensitivity to the temperature variations.

The results, illustrated in Fig.5, indicate the low PDP with small variation of the proposed single supply LC in the presence of temperature variations. It is worth mentioning that the relatively small parametric variation of the circuits at different temperatures is mostly due to the CNT thermal stability.

Fig. 5. Energy consumption of the designs vs temperature variations

-

VI. Conclusions

Список литературы An Energy-Efficient and Robust Voltage Level Converter for Nanoelectronics

- M. Alioto, "Ultra-Low Power VLSI Circuit Design Demystified and Explained: A Tutorial" IEEE Transactions on Circuits and Systems I, Vol. 59, No. 4, pp. 3-29, 2012.

- K. Roy and SC Prasad, "Low-Power CMOS VLSI Circuit Design", John Wiley & Sons, 2000.

- Y.-B. Kim, "Challenges for Nanoscale MOSFETs and Emerging Nanoelectronics, "Transactions on Electrical and Electronic Materials, Vol. 11, No. 3, pp. 93-105, Mar. 2010.

- M.H. Moaiyeri, , A. Doostaregan and Navi, K., "Design of energy-efficient and robust Ternary circuits for nanotechnology," IET Circuits, Devices & Systems , Vol. 5, No. 4, pp. 285-296, July 2011.

- F. Sharifi, M.H. Moaiyeri and K. Navi, "A Novel Quaternary Full Adder Cell Based on Nanotechnology," International Journal of Modern Education and Computer Science, vol. 7, No. 3, pp. 19-25, 2015.

- J. Liang, L. Chen, J. Han, and F. Lombardi, "Design and Evaluation of Multiple Valued Logic Gates Using Pseudo N-Type Carbon Nanotube FETs," IEEE Transaction on Nanotechnology, Vol. 13, No. 4, pp. 695-708, Jul. 2014.

- S. Sayedsalehi, MH Moaiyeri, and K. Navi, "Design of Efficient and Testable n-Input Logic Gates in Quantum-dot Cellular Automata," Journal of Computational and Theoretical Nanoscience, Vol. 10, No. 10, pp.2347-2353, 2013.

- J. Deng, "Device modeling and circuit performance evaluation for nanoscale devices: silicon technology beyond 45 nm node and carbon nanotube field effect transistors," PhD thesis, Stanford University, 2007.

- A. Raychowdhury, and K. Roy, "Carbon nanotube electronics: design of high-performance and low-power digital circuits," IEEE Transactions on Circuits and Systems I, Vol. 54, No. 11, pp. 2391-2401, Nov.2007.

- A. Lin, N. Patil, K. Roy, A. Badmaev, LG De Arco, C. Zhou, S. Mitra, and H.-SP Wong, "Threshold voltage and on- off ratio tuning for multiple- tube carbon nanotube FETs", IEEE Transactions on Nanotechnology, Vol. 8, No. 1, pp. 4-9, Jan. 2009.

- F. Yang, et al. "Chirality-specific growth of single-walled carbon nanotubes on solid alloy catalysts", Nature, vol. 510, No. 7506, pp. 522-524, 2014.

- Patil N., Lin A., Zhang J., Wei H., Anderson K., Wong H.-S. P. and Mitra S.: 'Scalable Carbon Nanotube Computational and Storage Circuits Immune to Metallic and Mispositioned Carbon Nanotubes' IEEE Transactions on Nanotechnology, Vol. 10, No. 4, pp. 744-750, 2011.

- S. R. Hosseini, M. Saberi, R. Lotfi, "A Low-Power Subthreshold Voltage Level Shifter to Above-Threshold," IEEE Transactions on Circuits and Systems II, Vol. 61, Vol. pp. 753-757, 2014.

- M. Kumar, S.K. Arya and S. Pandey, "Level Shifter Design for Low Power Applications," International Journal of Computer Science & Information Technology, Vol. 2, No. 5, pp. 124-132, 2010.

- R. Puri, L. Stok, J. Cohn, D.S. Kung, D.Z. Pan, D. Sylvester, A. Srivastava, S. Kulkarni, "Pushing ASIC Performance in a Power Envelope," DAC-40: ACM / IEEE Design Automation Conference, pp. 788-793, Anaheim, CA, June. 2003.

- M. Moghaddam, M. Eshghi and M.H. Moaiyeri, "A Low-Voltage Single-Supply Level Converter for Sub-VTH / Super-VTH Operation: 0.3V to 1.2V," International Journal of Computer Applications, Vol. 69, No. 2, pp. 14-18, May 2013.

- J. Zhang, N. Patil, H.-S.P. Wong, and S. Mitra, "Overcoming carbon nanotube variations through co-optimized technology and circuit design," in Proc. IEEE International Electron Devices Meeting, Dec. 2011, pp. 4.6.1-4.6.4.