Динамическая оперативная память с резервированием транзисторов

Автор: Тюрин С.Ф.

Журнал: Вестник Пермского университета. Математика. Механика. Информатика @vestnik-psu-mmi

Рубрика: Информатика. Информационные системы

Статья в выпуске: 4 (35), 2016 года.

Бесплатный доступ

Анализируется динамическое оперативное запоминающее устройство - динамическая оперативная память (ДОЗУ, Dynamic RAM - DRAM). По аналогии с шеститранзисторной ячейкой статической оперативной памяти SRAM, в которой резервируются транзисторы, рассматривается DRAM с резервированным транзистором. Оценивается вероятность безотказной работы DRAM с таким резервированием по сравнению с троированием.

Ячейка памяти sram, ячейка памяти dram, транзистор, избыточность, вероятность безотказной работы

Короткий адрес: https://sciup.org/14730082

IDR: 14730082 | УДК: 681.32 | DOI: 10.17072/1993-0550-2016-4-58-62

Dynamic random access memory with redundant transistors

The article analyzes dynamic random access memory (DRAM). DRAM with a redundant transistor is considered by analogy with a six-transistor SRAM cell, in which the transistors are reserved. The paper estimated the probability of failure-free operation of DRAM with such redundancy compared with triple redundancy.

Текст научной статьи Динамическая оперативная память с резервированием транзисторов

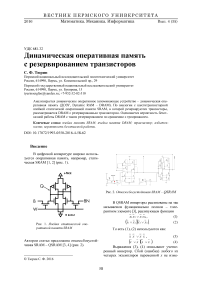

В цифровой аппаратуре широко используется оперативная память, например, статическая SRAM [1, 2] (рис. 1).

Рис. 1. Ячейка статической оперативной памяти SRAM

Автором статьи предложена отказосбоеустой-чивая SRAM – QSRAM [3, 4] (рис. 2).

Рис. 2. Отказосбоеустойчивая SRAM – QSRAM

В QSRAM инверторы реализованы на так называемом функционально полном – толерантном элементе [3], реализующем функции

X 1 X 2 V x 3 x 4 ,

( X 1 V X 2 \X 3 V X 4 )

То есть (1), (2) используются как:

XX V XX , (3)

( x v x \x v x ) (4)

Выражения (3), (4) описывают учетверенный инвертор. Сбой (ошибка) любого из четырех экземпляров переменной х не изме- няет функции (3), (4). Динамическое оперативное запоминающее устройство – динамическая оперативная память (ДОЗУ, Dynamic RAM – DRAM) также является важнейшим компонентом цифровых систем [5–10].

Вызывает интерес вопрос создания высоконадежной, отказоустойчивой динамической оперативной памяти в свете необходимости разработки отечественной радиационно-устойчивой элементной базы [10–11]. Данная тематика стала еще более актуальна в последние два года в связи с работами по так называемому импортозамещению.

Следует отметить, что, как оказалось, в соответствии с [12], скандально известный национальный стандарт ГОСТ Р 27.002-2009 "Надежность в технике. Основные понятия. Термины и определения" [13], "отменивший" понятие "сбой", к всеобщей радости, в том числе и Министерства Обороны, приостановлен и восстановлен прежний – межгосударственный стандарт ГОСТ 27.002-89 "Надежность в технике. Основные понятия. Термины и определения" [14] в качестве национального стандарта Российской Федерации с 1 декабря 2012 г. [12].

WL

Mi

Ci Data

б)

1. Анализ ячейки DRAM

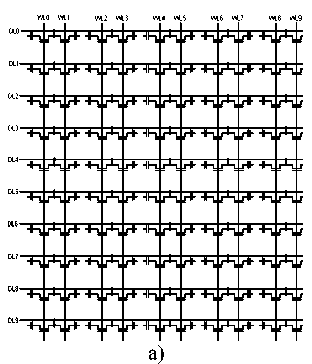

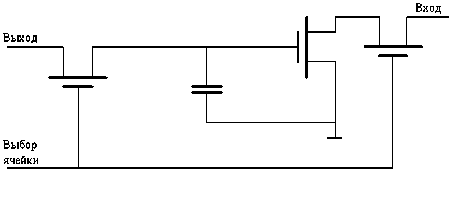

Рис. 4. Организация DRAM: а) матрица ячеек DRAM; б) ячейка DRAM, состоящая из одного транзистора и конденсатора

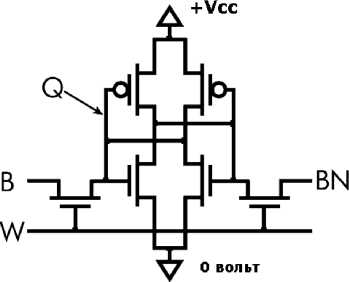

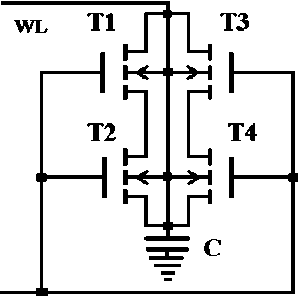

В работе [7] указано, что ячейка DRAM состоит из трех транзисторов и конденсатора (рис. 3).

Рис. 3. Ячейка DRAM, состоящая из трех транзисторов и конденсатора

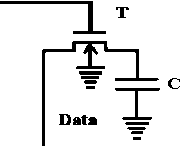

Возможно, что так строились первые поколения ДОЗУ (DRAM), сейчас в большинстве источников изображают ячейку DRAM так, как, например, [8, 9] – из одного транзистора и конденсатора (рис. 4).

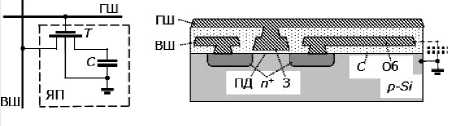

Управляющие затворы (рис. 4) подключаются к шине, которую называют линией слов (Word Line), вторая линия – данные (Data). Причем, в [8] подчеркнуто, что роли конденсатора нет, его роль выполняет емкость между затвором и истоком транзистора. На рис. 5 показан "удлиненный" исток n- канального транзистора (может быть и р -канальный), реализующий емкость С.

а) б)

Рис. 5. Ячейка оперативной памяти (ЯП) DRAM с передающим (ключевым) МДП транзистором Т: а) подключение ЯП к ГШ-горизонтальной шине и ВШ – вертикальной шине; б) топология ЯП: ПД – подзатворный диэлектрик, Об – обкладка конденсатора С

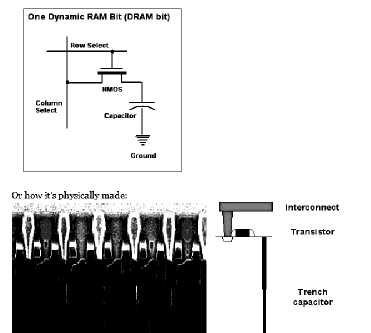

Указано [8], что значительную площадь DRAM занимает тонкопленочный конденсатор (рис. 5, б). Это как бы конденсатор "вдоль". В то же время имеются источники [15], в которых описаны так называемые "траншейные" конденсаторы – т.е. расположенные "поперек" (рис. 6).

Рис. 6. DRAM с траншейным конденсатором

При этом идет постоянная борьба за увеличение отношения длины "цилиндра" конденсатора к диаметру, сейчас оно приближается к 100 (!) [16].

Таким образом, по сравнению со шеститранзисторной SRAM, в DRAM на один бит "тратится" всего один транзистор и один конденсатор. Тем не менее, в DRAM необходима постоянная регенерация заряда конденсатора, что существенно уменьшает быстродействие. Кроме того, при считывании информации используются усилители, и затем информационное слово все равно размещается в SRAM.

2. Резервирование транзистора ячейки DRAM

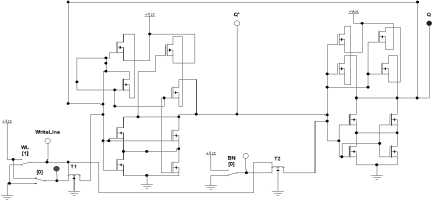

Итак, ячейка DRAM, состоящая из одного транзистора и конденсатора, может быть представлена следующим образом (рис. 7):

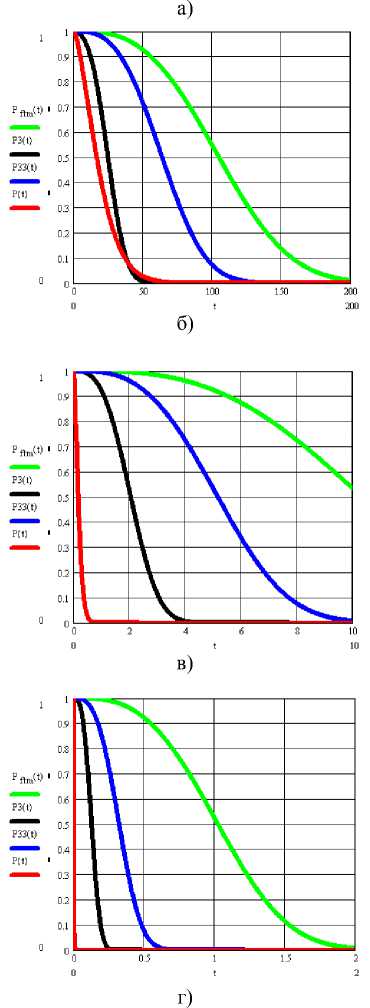

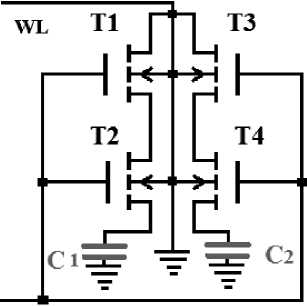

Ячейка DRAM с резервированным транзистором представлена на рис. 8.

Data

Рис. 8. Ячейка DRAM с резервированным транзистором

Таким образом, получаем ячейку, работоспособную при отказе одного транзистора из четырех.

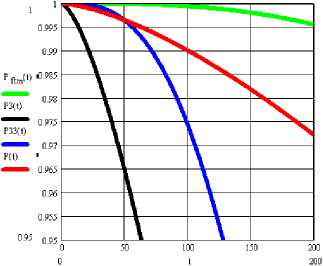

Оценим надежность с учетом распределения Вейбулла [5, 6], наиболее адекватного условиям воздействия тяжелых заряженных частиц –ТЗЧ – на электронные компоненты где λ – интенсивность отказов одного транзистора, α – коэффициент 1 ≤ α ≤ 2 , t – время работы при воздействии радиации.

P(t) = e - (1) ⋅ λ ⋅ t α , (5)

P(t) = e - (210) ⋅ λ ⋅ t α . (6)

При мажоритировании всей DRAM с мажоритарами по выходам 8-разрядного регистра:

P(t) 3 =

= [3 ⋅ e - 2 ⋅ (210) ⋅ λ ⋅ t α - 2 ⋅ e - 3 ⋅ (210) λ ⋅ t α ] ⋅ (e - (10) λ ⋅ t α ) 8 . (7)

Мажоритирование с троированными мажоритарами по выходам 8-разрядного ре- гистра:

WL

Рис. 7. Ячейка DRAM, состоящая из одного транзистора и конденсатора

P(t)33 = [3 ⋅ e - 2 ⋅ (210) ⋅ λ ⋅ t α - 2 ⋅ e - 3 ⋅ (210) λ ⋅ t α ] ⋅ ⋅ [3 ⋅ e - 2 ⋅ (10) ⋅ λ ⋅ t α - 2 ⋅ e - 3 ⋅ (10) λ ⋅ t α ] 8 .

Расчетверение транзисторов ячейки показано на рис. 8.

Сравнение вероятности безотказной работы (5), (6), (7), (8) представлено на рис. 9.

Рис. 9. Сравнение вероятности безотказной работы (5), (6), (7), (8) при α=1,5; Л = 10 - 5 : а) для одной ячейки; б) килобайт; в) мегабайт; г) гигабайт, 64 разряда

Однако схема рис. 8 не парирует отказы конденсатора. Для его резервирования может быть предложена схема рис. 10.

Data

Рис. 10. Ячейка DRAM с расчет-веренным транзистором и дублированным конденсатором

Причем подложки транзисторов также могут быть подключены к отдельному входу шины "Ноль вольт".

Выводы

Таким образом, предложенное резервирование транзистора в ячейке динамической оперативной памяти DRAM позволяет получить вероятность безотказной работы существенно выше, чем при троировании DRAM, за счет большей избыточности. При учете возможной неисправности конденсатора типа "обрыв" в условиях воздействия ТЗЧ имеет смысл его дублирование.

В дальнейшем целесообразно выполнить схемотехническое моделирование такой резервированной ячейки DRAM с учетом нюансов регенерации заряда конденсатора.

Список литературы Динамическая оперативная память с резервированием транзисторов

- Строгонов А., Цыбин С. Программируемая коммутация ПЛИС: взгляд изнутри. URL: http://www.kite.ru/articles/plis/2010_11_56.p hp (дата обращения: 02.09.2016).

- Donald C. Mayer, Ronald C. Lacoe. Designing Integrated Circuits to Withstand Space Radiation. Vol. 4, № 2. Crosslink. URL: http://www.aero.org/publications/crosslink/su mmer2003/06.html (дата обращения: 20.09.2016).

- Тюрин С.Ф., Морозов А.Н. Отказоустойчивая ячейка памяти с использованием функциональнополных толерантных элементов//Вестник Пермского университета. Математика. Механика. Информатика. 2012. Вып. 4(12). С. 68-75.

- Тюрин С.Ф. Ячейка статической оперативной памяти. Патент РФ № 2573226. Опубл. БИ № 2 20.01.2016.

- Угрюмов Е.П. Цифровая схемотехника: учеб. пособие для вузов. Изд. 3-е, перераб. и доп. СПб.: БХВ-Петербург, 2010. 816 с.

- Угрюмов Е.П. Программируемые компоненты устройств и систем на кристалле: учеб. пособие. СПб: изд-во СПбГЭТУ "ЛЭТИ", 2013. 120 с.

- Динамическая оперативная память. URL: http://all-ht.ru/inf/pc/mem_dram.html (дата обращения: 20.08.2016).

- Горбатко С. Динамическая оперативная память. URL: http://www.colocat.ru/texts/ram.html (дата обращения: 20.08.2016).

- Ячейка оперативной памяти. Принцип работы. URL: http://sdelaycomputersam.ru/Cell_ram.html (дата обращения: 20.08.2016).

- Петропавловский Ю. Радиационно-стойкие микросхемы компании Atmel//Современная электроника, 2012. № 7. URL: http://www.soel.ru/upload/clouds/1/iblock/6c f/6cf5d14e94f28ab9112553b8229edb3e/2012 0710.pdf (дата обращения: 20.08.2016).

- Шумилин С., Леонов С. Радиационно-стойкие микросхемы от компании "Миландр"//Компоненты и технологии, 2015. № 7. URL: http://ecworld.ru/media/bip/pdfs/shumilin_ct 715.pdf (дата обращения: 20.09.2016).

- Федеральное агентство по техническому регулированию и метрологии. Приказ от 29 ноября 2012 г. № 1843-ст URL: http://www. consultant. ru/cons/cgi/online.cgi? req=doc;base=EXP;n=552389 (дата обращения: 20.09.2016).

- ГОСТ Р 27.002-2009. Надежность в технике. Термины и определения. URL: http://protect.gost.ru/document.aspx?control= 7&id=177217 (дата обращения: 20.08.2016).

- ГОСТ 27.002-89. Надежность в технике. Основные понятия. Термины и определения. URL: http://www.internet-law.ru/gosts/gost/11290/(дата обращения: 20.08.2016).

- Memories-DRAMs. URL: http://www.engr.uky.edu/~elias/lectures/ln_1 8.pdf (дата обращения: 21.09.2016).

- Samsung придумала, как можно уменьшить DRAM до технологических норм 10 нм. URL: http://www.russianelectronics.ru/leader-r/news/9318/doc/74552/(дата обращения: 22.09.2016).