Самосинхронный регистр с расчетверением транзисторов

Автор: Тюрин С.Ф., Каменских А.Н.

Журнал: Вестник Пермского университета. Математика. Механика. Информатика @vestnik-psu-mmi

Рубрика: Информатика. Информационные системы

Статья в выпуске: 3 (34), 2016 года.

Бесплатный доступ

Самосинхронная схемотехника (ССС) является альтернативой синхронной и обеспечивает фиксацию завершение переходного процесса, что повышает быстродействие, позволяет работать на сверхнизких напряжениях питания и выполнять самоконтроль. Основоположником ССС является Д. Маллер. В настоящее время ССС активно продвигается не только на "зелёной" волне энергосберегающих технологий, но и в русле повышения степени интеграции цифровых чипов до наноуровня, когда уже начинают сказываться квантовые эффекты. В Институте проблем информатики - ИПИ РАН активно работает группа Ю.А. Степченко-ва, которая, продолжая дело группы В.И. Варшавского, разработала обширную библиотеку самосинхронных элементов. В Великобритании работает в направлении ССС проф. А. Яковлев, ранее работавший с В. Варшавским. Однако вопросы отказоустойчивости самосинхронных схем до сих пор исследованы недостаточно. Авторами статьи предложено комбинированное резервирование самосинхронной схемотехники (ССС) на основе расчет-верения (по терминологии классификатора ФИПС) транзисторов. В статье предлагается и оценивается комбинированное резервирование триггеров самосинхронного регистра, выполняющего функции приемопередатчика тестового самосинхронного процессора. Показывается эффективность такого резервирования по сравнению с троированием.

Самосинхронная схемотехника, самосинхронный регистр, кмдп-транзистор, резервирование, вероятность безотказной работы, мажоритарный элемент, транзисторная структура

Короткий адрес: https://sciup.org/14730055

IDR: 14730055 | УДК: 681.32 | DOI: 10.17072/1993-0550-2016-3-103-109

A fault-tolerant self-timed register

Self-timed technology, the foundations of which were laid by D. Muller, has been actively promoted in recent years not only on the "green" wave of energy saving technologies, but also in line with the increasing integration of digital chips to the nanoscale, where quantum effects begin to affect. The Institute of Informatics Problems - IPI RAN, continuing work of V.I. Warsawski's research group, has developed an extensive library of self-timed elements. In the UK, A. Yakovlev, who previously worked with V.I. Warsawski, is now engaged in this field. However, questions of fault tolerance self-timed circuits are still investigated insufficiently. We know that to create reliable, fault-tolerant and radiation-resistant electronic components, redundancy, or redundant structure, is needed. Redundant structures are necessary to design highly reliable, fault-tolerant, radiation-tolerant electronic components. Triplication is often used for this task: the three channels of a discrete circuit are connected with a special major gate which implements the choice function (e.g., 2-of-3, >2). This redundancy is commonly used in critical computing systems with passive fault-tolerance. As is known, such redundant structures provide reliability advantages not for the whole time range. In this case (to reserve self-timed circuits), the basic principle of self-timed, semi-modular, devices is violated. The authors propose another technique of using redundant transistor structures for fault-tolerant computing systems as an alternative to triple modular redundancy. The paper proposes and evaluates a combined backup of triggers of a self-timed register using transistor structures. We show the effectiveness of this redundancy, compared with triple modular redundancy.

Текст научной статьи Самосинхронный регистр с расчетверением транзисторов

Самосинхронная схемотехника, впервые предложенная в работах Маллера [1] в конце 1950-х гг. ХХ в. и развитая в СССР ленинградской группой В. Варшавского [2, 3] в постсоветский период продолжает развиваться благодаря трудам его бывших учеников и последователей, например Алекса Яковлева [3], работающего теперь в университете НьюКасла (Великобритания). В России активно работает исследовательская группа института проблем информатики РАН, возглавляемая Ю. Степченковым, разработавшая и продолжающая совершенствовать библиотеку само-синхронных элементов [5]. Имеются примеры

коммерческого использования самосинхрон-ной технологии [6]. Это направление в нашей стране может внести вклад в создание отечественной электронной компонентной базы [7], степень актуальности которой подошла уже к критической отметке. В этом плане большие надежды возлагаются на базовые матричные кристаллы [8–11], использование которых, в том числе для реализации самосинхронных цифровых решений, в какой-то мере может компенсировать технологическое отставание в критических областях, особенно в оборонной, хотя некоторые подвижки на "интегральном" поприще и внушают определенный оптимизм [12–14]. В этих областях применения весьма востребованы надежные, отказоустойчивые цифровые устройства, особенно радиационно-стойкие [15–17]. Однако вопросы на- дежности самосинхронных схем по большей части рассматриваются в ракурсе активной отказоустойчивости, путем дублирования, в предположении о том, что имеются соответствующие средства контроля, которые зафиксируют отказ [18–20], а средства реконфигурации отключат неисправный канал и подключат исправный. Для ряда важных областей необходима пассивная отказоустойчивость [21], когда отказ или ошибка (этот термин по аналогии с английским "error" теперь использован в ГОСТ [18] вместо термина "сбой") не замечается, маскируется устройством или системой, что требует значительно большей избыточности, но зато не требует временных затрат на восстановление. Тем не менее, исследования в области пассивно отказоустойчивых самосинхронных схем освещены в литературе недостаточно, в основном речь идет о комбинационных схемах [22–23].

В статье предпринята попытка построить пассивно отказоустойчивую регистровую самосинхронную схему, используемую в качестве приемо-передающего порта [5] на основе потразисторного резервирования [24]. Анализ сложности и вероятности безотказной работы нерезервированного самосинхронного приемо-передающего порта, состоящего из трех типов триггеров и описанного в [5], при экспоненциальной модели отказов транзисторов позволяет получить выражением

- (22 + 52 + 54 - 6 + 54 - 8 - ( b - 1) + 16 - 2 r iog28b ^

) Л - t

P(t) b = e

, (1)

где λ – интенсивность отказов одного транзи- стора; b – число байт, принимаемых регист- ром; 22 – сложность в транзисторах первого триггера, именуемого в библиотеке элементов аббревиатурой R1RE11; 52 – последнего R1RE22; 54 – промежуточных триггеров S1RRE2; 16 - 2fl°B28b^ - сложность гистерезис-

R

E

RT

S

QB

I

Q

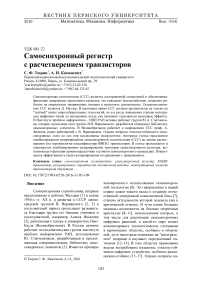

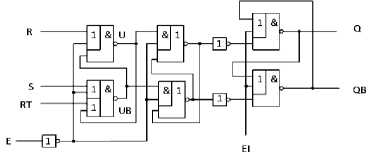

Рис. 1. Первый триггер R1RE11

Первый триггер регистра – R1RE11 – содержит 22 транзистора, при этом во всех цепочках не более 2 транзисторов, поэтому при резервировании путем расчетверения ограничения [25] выполняются [24], получаем:

P(t)«,RE„ = [e-(4M-' + 4 - e-’" (1" e-u-' )]22 .(2)

При увеличении числа байт не изменяется. Затраты – 88 транзисторов. Последний триггер регистра – R1RE22 – представлен на рис. 2.

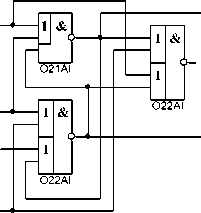

Рис. 2. Последний триггер R1RE22

Триггер R1RE22 содержит 28 транзисторов в самой двухступенчатой памяти, но имеет индикатор АОАI7 (16 транзисторов), в котором число транзисторов в последовательной цепочке превышает ограничения, поэтому предлагается повторить его 4 раза, учитывая блоки NAN2, т. е. получаем формулу:

ных триггеров, остальная аппаратура обрамления имеет незначительную сложность и не учитывается. Предложим потранзисторное резервирование с учетом ограничений на число последовательно включенных транзисторов (не более 4) [25].

P(t)

ft -R1RE22

[e " (4) - Л - t

i [е " (64) Л - t

+ 4 - e - 3 - Л - t(1 - e - 1 - Л - t)]28

+ 4 - e - 48 Л - t

(1 - е - 16 Л - t

)] - e - (16) Z - t(

1.Расчетверение транзисторов триггеров самосинхронного регистра с учетом b байт

Первый триггер – R1RE11 – изображен на рис. 1.

Затраты (112+ 64+16) транзисторов.

Основной триггер S1RRE2 для удовлетворения ограничения [25] требует декомпозиции (детальное рассмотрение которой, названной комбинированным расчетверением, предполагается в отдельной статье) второй ступени A31OI1, A31OI1 и резервирования индикатора ОAOА1 (рис. 3).

Рис. 3. Основной триггер S1RRE2

4. Оценка троирования аппаратуры регистра при наличии b байт порта

В случае мажоритирования с одним мажо-ритаром (сложность которого – 12 транзисторов), R1RE11(сложность – 22 транзистора), имеющий три выхода, описывается формулой (7):

P(t)3-R1REn = [3-e-2 ■ t -2■e-3■(22)л■t]■

- (3 - 12 - + 6 + 6) л - t

e.

Триггер R1RE22 (сложность – 52 транзистора), имеющий 4 выхода, описывается формулой (8):

P(t) 3-R1RE22 = [З^ (52) ^ t - 2^ (52) ^ t ] - (8) - (4 ■ 12 + 6 + 6) ■ л - t

e.

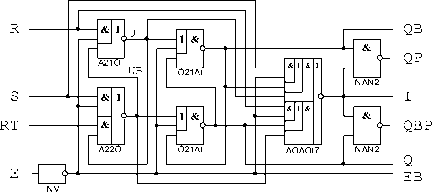

После декомпозиции второй ступени A31OI1 получим (рис. 4).

Рис. 4. Основной триггер S1RRE2 с декомпозицией второй ступени

Триггер S1RRE2 (сложность – 54 транзистора), имеющий 4 выхода, описывается формулой (9).

p+ = ГЗ • e -2 ■ (54) л ■ t

(L) 3-1 x S1RRE2 [ e

- (4 - 12 + 6 + 6) - Л - t

e.

То есть получаем после декомпозиции:

P(t) 6 - ft-S1RRE2

= {[e - (4 R t

+ 4 ■ e - 3 - Z 4(1 - e - 1 - л 4)]44

[e

- (80) л ■ t

+ 4 ■ e - 60 - л - t

(1 - e - 20 - л - t

)] ■ e - (16) л - t

]}6.

В случае b байт

P(t) b-6 - ft-s1RRE2 = {[e - (4) - A t + 4 ■ e - 3 л 4(1 - e - 1 - л )]44

[e

- (80) Л ■ t

+ 4 - e

- 60 ■ л ■ t

(1 - e

- 20 ■ Л ■ t

■ e - (16) ■ л ■ t

]}6-

■ {[e - (4) л + 4 ■ e - 3 л (1 - e " b л )]44 (5)

[e

- (80) л t

+ 4 - e

- 60 л t

(1 - e

20 л t

)] ■ e

,-(16) - л-t

]}

8(b - 1)

.

Затраты – (44*4+80+16) в степени 6+(44*4+80+16) в степени 8*(b-1) транзисторов.

К дополнительной аппаратуре относятся Г-триггеры, количество которых при условии наличия у них двух входов можно оценить числом узлов по уровням соответствующего дерева для одного байта 4, 2, 1 всего 7, т.е. 2 3 - 1 , на единицу меньше байта. Если имеется b байт, получаем 2^ 2 8^ - 1 . То есть, получим:

P(t)ft-r = [e - (4) ' л 4 + 4 ■ e - 3 ■ л4 ■ (1 - e - 1 л 4)]28<2 Гь,1“ L1) .(6)

-

2e 3■ (54)л■ t +

2 e ] (9)

Поскольку для одного байта таких триггеров 6, получим

P(t)3-6 x S1RRE2 =

^■e - 2^ л ■ t

- 4 - 12 л - t к e

—

2 - e - 3 (54) л ■ * ] ■

/

. (10)

При наличии b байт порта вероятность безотказной работы имеет вид

P(t)3-b x S1RRE2 =

,- 2 - (54) - л - t

,- 2 - (54) -л-t

—

—

■ 2-e-3 - (54) л 4]-e-4 - 12 - л 4 )6-|

9 о- 3 - (54) л - t - 4 - 12 - л - t 8 (b - 1)

2 - e J^ ) .(11)

Затраты (162+48) в степени 6+(162+48) в степени 8( b -1).

В случае мажоритирования с тремя ма-жоритарами (сложность которого – 12 транзисторов), R1RE11 (сложность – 22 транзистора), имеющий три выхода, описывается формулой

P(t1 3-RIRE11 =

= [3 ■ e - 2 - (22) л - t - 2 ■ e - 3 ■ (22) л - t ]

■ [3 - e - 2 - (12) - л ■ t - 2 - e - 3 ■ (12) л ■ t ] 3

.

В случае мажоритирования с тремя ма-жоритарами триггер R1RE22 (сложность – 52 транзистора), имеющий 6 выходов, описывается формулой

P(t)3.3-R1RE22

= [3 • e

— 2 - (52) - Л - t

—

2 • e

— 3 - (52) Л - t

] •

• [3 • e

— 2 - (12) - Л - t

— 2 e

— 3 - (12) Л 4]6

.

Триггер S1RRE2 (сложность – 54 тран-

зистора), имеющий 4 выхода, описывается

формулой

0 t 17 - 102

б)

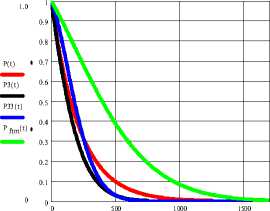

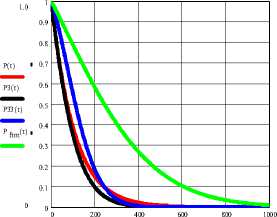

Рис. 5. Графики изменения вероятности безотказной работы а) – в диапазоне от 1 до 0,5; б) в диапазоне от 1 до 0 – схемы без резервирования P(t) , вероятности безотказной работы резервированной схемы – с комбинированным расчетверением P(t) , вероятности безотказной работы резервированной – троированной схемы с одним мажоритаром P3 и троированной схемы с тремя мажоритарами P при интенсивности отказов (сбоев) Л = 10-5

P(t ) 3.3-1 x S1RRE2

= [3- e

,— 2 - (54) Л - t

—2 e

, —3 - (54) Л - t

]•

-[3- e

— 2 - (12) - Л - t

—

2 • e

— 3 (12) Л t 4

]

.

Поскольку для одного байта таких триг-

геров 6, получим:

P(t)3.3-6 x S1RRE2 =

f[3 e

,-2 - (54> 2 - t

—

2 • e

.-3 - (54) Л - t ] -

Ф - e

,— 2 - (12) - Л - t

—

2 • e

,— 3 - (12) Л - t-14

] 7

. (15)

1/час для одного байта

-

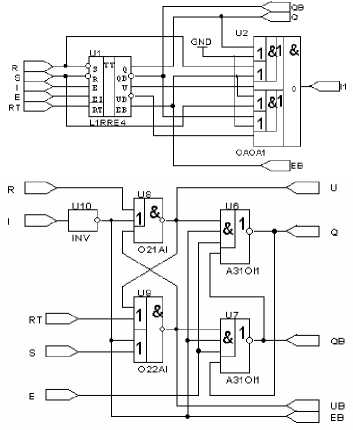

4. Сравнение вероятностей безотказной работы вариантов схем самосинхронного регистра

Построим в СКМ МАТКАД графики изменения вероятности безотказной работы исходной схемы самосинхронного регистра без резервирования P(t) , вероятности безотказной работы резервированной схемы – с комбинированным расчетверением P(t)ftm , вероятности безотказной работы резервированной – троированной схемы с одним мажоритаром P3 и троированной схемы с тремя мажоритарами P33 при заданной интенсивности отказов для заданного числа байтов.

Возьмем интенсивность отказов Л = 10 -5 , один байт, получим рис. 5.

а)

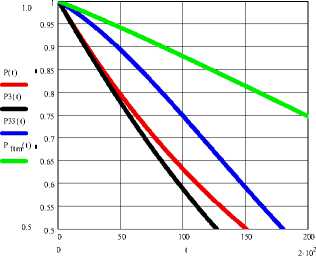

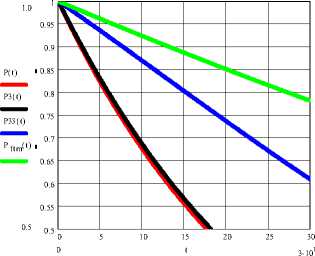

Зададим при той же интенсивности отказов Л = 10 -5 два байта, получим рис. 6.

а)

0 t 10 - 102

б)

Рис. 6. Графики изменения вероятности безотказной работы а) в диапазоне от 1 до 0,5; б) в диапазоне от 1 до 0 – схемы без резервирования P(t) , вероятности безотказной работы резервированной схемы – с комбинированным расчетве-рением P(t) , вероятности безотказной работы резервированной – троированной схемы с одним мажоритаром P 3 и троированной схемы с тремя мажоритарами P33 при интенсивности отказов (сбоев) Л = 10-5 1/час для двух байтов

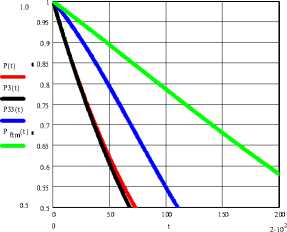

Зададим при тех же условиях восемь байт, получим рис. 7.

Рис. 7. Графики изменения вероятности безотказной работы в диапазоне от 1 до 0,5 – схемы без резервирования P(t) , вероятности безотказной работы резервированной схемы – с комбинированным расчетверением P(t) , вероятности безотказной работы резервированной – троированной схемы с одним мажоритаром P3 и троированной схемы с тремя мажоритарами P при интенсивно сти отказов (сбоев) Л = 10-5 1/час для восьми байтов

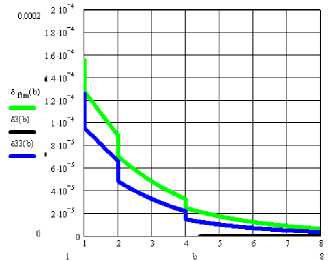

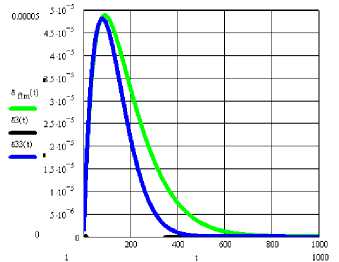

Однако оценим еще и так называемую удельную надежность – в пересчете на один транзистор в зависимости от числа байт (рис. 8) и времени (рис. 9).

Рис. 8. Графики изменения удельной вероятности безотказной работы резервированной схемы – с комбинированным расчетверением δ ftm , резервированной – троированной схемы с одним мажоритаром δ 3 и троированной схемы с тремя мажоритарами δ 33 при интенсивности отказов (сбоев) X = 10-5 1/час для 200 часов работы в зависимости от числа байт

Рис. 9. Графики изменения удельной вероятности безотказной работы резервированной схемы – с комбинированным расчетверением δ ftm , резервированной – троированной схемы с одним мажоритаром δ 3 и троированной схемы с тремя мажоритарами δ 33 при интенсивности отказов (сбоев) X = 10-5 1/час для четырех байт в зависимости от времени

Выводы

Таким образом, предложенное резервирование позволяет существенно повысить вероятность безотказной работы на всем интервале вероятностей по сравнению с троированными вариантами и нерезервированной схемой. Простое троирование (мажоритирова-ние) не имеет смысла – оно уступает не резервированной схеме после определенного времени. При этом удельная вероятность безотказной работы схемы самосинхронного регистра с комбинированным расчетверением при небольшом числе байт превышает удельную вероятность безотказной работы троированной схемы самосинхронного регистра с тремя мажоритарами, а при большом числе байт – незначительно уступает ей.

Список литературы Самосинхронный регистр с расчетверением транзисторов

- Muller D.E., Bartky W.S. A theory of asynchronous circuits//Proc. Int Symp. On the Theory of Switching, Part 1. Harvard University Press, 1959. P. 204-243.

- Апериодические автоматы/под ред. Варшавского В.И. М.: Наука, 1976. С. 304.

- Варшавский В.И., Мараховский В.Б., Розенблюм Л.Я., Яковлев А.В. § 4.3 Апериодическая схемотехника//Искусственный интеллект, т. 3: Программные и аппаратные средства/под ред. В.Н. Захарова и В.Ф. Хорошевского. М.: Радио и связь, 1990.

- Yakovlev A. Energy-modulated computing//Design, Automation & Test in Europe Conference & Exhibition (DATE), 2011. IEEE, 2011. С. 1-6.

- Степченков Ю.А., Денисов А.Н., Дьяченко Ю.Г. и др. Библиотека элементов для проектирования самосинхронных полузказных микросхем серий 5503/5507 и 5508/5509. М.: ИПИ РАН, 2008. 296 с.

- Hollosi B. et al. Delay-insensitive asynchronous ALU for cryogenic temperature environments//Circuits and Systems, 2008. MWSCAS 2008. 51st Midwest Symposium on. IEEE, 2008. С. 322-325.

- Проблемы создания отечественной элементной компонентной базы. URL: http://www.electronics.ru/journal/article/295. (дата обращения: 27.06.2015).

- Инновационный комплекс МИЭТ. URL: http://miet.ru/content/s/200 (дата обращения: 27.06.2015).

- Базовые матричные кристаллы. URL: http://www.asic.ru/index.php?option=com_c ontent&view=article&id=52&Itemid=92 (дата обращения: 27.06.2015).

- Гаврилов С.В., Денисов А.Н., Коняхин В.В.и др. САПР "Ковчег 3.0" для проектирования микросхем на БМК серий 5503, 5507, 5521 и 5529. М.: 2013. 295 с.

- Денисов А.Н., Фомин Ю.П., Коняхин В.В.и др. Библиотека функциональных ячеек для проектирования полузаказных микросхем серий 5503 и 5507/под общ. ред. А.Н. Саурова. М: Техносфера, 2012. 304 c.

- МЦСТ. Микропроцессор нового поколения Эльбрус 2С+. URL: http://www.mcst.ru/modul-comexpress (дата обращения: 28.06.2015).

- Федеральное государственное учреждение "Федеральный научный центр Научно-исследовательский институт системных исследований Российской академии наук" URL: https://www.niisi.ru/(дата обращения: 28.06.2015).

- ОАО КБ "Корунд-М". URL: http://www.korund-m.ru/(дата обращения: 28.06.2015).

- Donald C. Mayer, Ronald C. Lacoe. Designing Integrated Circuits to Withstand Space Radiation. Vol.4, № 2, Crosslink. URL: http://www.aero.org/publications/crosslink/su mmer2003/06.html (дата обращения: 20.05.2015).

- Юдинцев В. Радиационно-стойкие интегральные схемы. Надежность в космосе и на земле//Электроника: Наука, Технология. 2007. № 5. С. 72-77. ISSN 1992-4178. URL: http://www.electronics.ru/files/article_pdf/0/article_592_363.pdf (дата обращения: 29.05.2015).

- Чекмарёв С.А. Способ и система инъекции ошибок для тестирования сбоеустойчивых процессоров бортовых систем космических аппаратов//Вестник Сибирского государственного аэрокосмического университета им. академика М.Ф. Решетнева. Вып. № 4(56). 2014 URL: http://cyberleninka.ru/article/n/sposob-i-sistema-inektsii-oshibok-dlya-testirovaniya-sboeustoychevyh-protsessorov-bortovyh-sistem-kosmicheskih-apparatov (дата обращения: 16.12.2015).

- ГОСТ Р 53480-2009. Надежность в технике. Термины и определения. IEC 60050 (191):1990-12 (NEQ). Москва: Стандартинформ, 2010.

- ГОСТ 20911-89. Техническая диагностика. Термины и определения. Москва: Стандартинформ, 2019.

- Stuck-atfault. URL: http://en.wikipedia.org/wiki/Stuck-at_fault (дата обращения: 28.05.2015).

- Бородин В.А. и др. Отказоустойчивые вычислительные системы. М.: МО СССР, 1990. С. 55.

- Тюрин С.Ф., Каменских А.Н. Анализ отказоустойчивой самосинхронной реализации двоичного сумматора//Вестник Пермского национального исследовательского политехнического университета. Электротехника, информационные технологии, системы управления. 2014. № 1(9). С. 25-39.

- Kamenskih, A.N., Tyurin, S.F. Features that provide fault tolerance of self-synchronizing circuits//Russian Electrical Engineering. 2015. P. 672-682.

- Tyurin S.F., Kamenskih A.N. Research into the reservation of logic function at transistor level. В мире научных открытий. 2014. № 10 (58). С. 232-247.

- Дж. Д. Ульман. Вычислительные аспекты СБИС/пер. с англ. А.В. Неймана/под ред. П.П. Пархоменко. М.: Радио и связь, 1990. 480 с.