Технология и методика обучающего эксперимента КМОП-микросхем

Автор: Мишанов Р.О.

Журнал: Физика волновых процессов и радиотехнические системы @journal-pwp

Статья в выпуске: 1 т.21, 2018 года.

Бесплатный доступ

Рассмотрена методика обучающего эксперимента интегральных микросхем с КМОП-структурой. Проведен анализ конструктивно-технологических особенностей микросхем серии 765. Предложены схемы их включения и измерения основных параметров при проведении обучающего эксперимента. Сделан выбор методов и средств контроля информативных параметров в процессе исследовательских испытаний. Описан процесс выбора объема выборки. Определен подход к разработке программных исследовательских испытаний.

Методика, обучающий эксперимент, микросхема, кмоп-структура, конструктивно-технологические особенности, серия 765, схемы включения, основные параметры, информативные параметры, объем выборки, исследовательские испытания, средства контроля

Короткий адрес: https://sciup.org/140256033

IDR: 140256033

Technology and technique of the CMOS-chip learning experiment

The technique of the learning experiment of the chips with a CMOS structure is considered. The analysis of the constructive-technological features of the 765 series chips have carried out. The connection circuits and schemes of the main parameters measurement during the learning experiment are proposed. A choice of methods and means for the informative parameters control in the investigation tests is studied. The process of the sample size selecting is described. An approach to the development of the routine investigation tests is defined.

Текст научной статьи Технология и методика обучающего эксперимента КМОП-микросхем

Постоянно возрастающие требования к качеству и надежности радиоэлектронных средств (РЭС) приводят к поиску различных методов, позволяющих своевременно определить величину показателей качества и надежности, предотвратить отказ и обеспечить необходимую работоспособность электрорадиоизделий (ЭРИ) и изделия в целом. Одним из таких перспективных методов является индивидуальное прогнозирование показателей качества и надежности, важнейшим этапом которого, наряду с обучением, экзаменом и прогнозированием, является обучающий эксперимент.

Обучающий эксперимент – это испытание в заданном режиме определенного количества (выборки) исследуемых изделий в течение требуемого времени, обычно равного времени последующего прогнозирования tпр , и определение фактического состояния каждого экземпляра выборки к моменту окончания испытания (обычно к моменту tпр ). Цель обучающего эксперимента состоит в получении необходимого массива исходных данных, т. е. такого массива, который требуется для последующего обучения [1].

Таким образом, важнейшим вопросом обучающего эксперимента является разработка методики его проведения. Автор [2] выделяет семь основных этапов общей методики для биполярных микросхем серии 286:

– анализ конструктивно-технологических особенностей ЭРИ и РЭС;

– разработка или уточнение схем включения для контроля их работоспособности и измерения основных параметров;

– выбор методов и средств контроля информативных параметров;

– определение объема выборки;

– разработка программы исследовательских испытаний;

– проведение исследовательских испытаний и экспериментов;

– анализ результатов испытаний и экспериментов.

Воспользуемся данной общей методикой для КМОП микросхем и оценим ее эффективность. Рассмотрим основные этапы.

1. Анализ конструктивнотехнологических особенностей микросхем

Интегральные микросхемы (ИМС) 765 серии получили широкое применение в вычислительной технике, устройствах обработки цифровой информации, системах связи, измерительных устройствах, в гибридных интегральных микросхемах, микросборках, бортовой аппаратуре. Микросхемы серии 765 имеют бескорпусное исполнение и являются функциональными и параметрическими аналогами микросхем серии 564.

Таблица 1

Функциональное назначение микросхем 765ЛН1-1, 765ИП2-1, 765ЛП2-1

|

Вид микросхемы |

Функциональное назначение |

Технические условия |

|

765ЛН1-1 |

Шесть логических элементов «НЕ» с блокировкой и запретом |

бКО.347.151 ТУ бКО.347.151 ТУ3 |

|

765ИП2-1 |

4-х разрядная схема сравнения |

|

|

765ЛП2-1 |

Четыре логических элемента «Искл. ИЛИ» |

Таблица 2

Значения электрических параметров микросхем 765ЛН1-1, 765ИП2-1, 765ЛП2-1

|

Наименование параметра |

Вид микросхемы |

Температура |

||

|

765ЛН1-1 |

765ИП2-1 |

765ЛП2-1 |

||

|

Входной ток логического нуля, I 0 вх , мкА, не более |

0.05 |

0.05 |

0.05 |

+ 25 ± 10; - 60 ± 3 ° С |

|

1.0 |

1.0 |

1.0 |

+ 85 ± 3 ° С |

|

|

Входной ток логической единицы, I 1 вх , мкА, не более |

0.05 |

0.05 |

0.05 |

+ 25 ± 10; - 60 ± 3 ° С |

|

1.0 |

1.0 |

1.0 |

+ 85 ± 3 ° С |

|

|

Ток потребления в статическом режиме, I , мкА, не более, пот . при U num . = 10 В (5 В) |

0.6 (1.0) |

5.0 (200) |

0.5 (30.0) |

+ 25 ± 10; - 60 ± 3 ° С |

|

400 (60.0) |

10 (600) |

1.0 (60.0) |

+ 85 ± 3 ° С |

|

|

Выходной ток логического нуля, I 0 , мА, не менее, вых . при U num . = 10 В (5 В) |

5.3 (2.3) |

0.5 (0.4) |

1.2 (0.6) |

+ 25 ± 10 ° С |

|

3.52 (1.6) |

0.65 (0.28) |

0.9 (0.45) |

+ 85 ± 3 ° С |

|

|

6.6 (2.7) |

1.1 (0.5) |

1.5 (0.75) |

- 60 ± 3 ° С |

|

|

Выходной ток логической единицы, I 0 , мА, не менее, вых . при U num . = 10 В (5 В) |

0.5 (0.5) |

0.5 (0.5) |

0.65 (0.3) |

+ 25 ± 10 ° С |

|

0.35 (0.35) |

0.35 (0.35) |

0.45 (0.21) |

+ 85 ± 3 ° С |

|

|

0.62 (0.62) |

0.62 (0.62) |

0.95 (0.45) |

- 60 ± 3 ° С |

|

|

Выходное напряжение логического нуля, U 0 , В, не более, вых . , , , при U num . = 10 В (5 В) |

0.01 (0.01) |

0.01 (0.01) |

0.01 (0.01) |

+ 25 ± 10; - 60 ± 3 ° С |

|

0.05 (0.05) |

0.05 (0.05) |

0.05 (0.05) |

+ 85 ± 3 ° С |

|

|

Выходное напряжение логической единицы, U 1 вых ., В, не менее, при U num . = 10 В (5 В) |

9.99 (4.99) |

9.99 (4.99) |

9.99 (4.99) |

+ 25 ± 10; - 60 ± 3 ° С |

|

9.95 (4.95) |

9.95 (4.95) |

9.95 (4.95) |

+ 85 ± 3 ° С |

|

|

Максимальное выходное напряжение логического нуля, U , В, не более, вых .max , , , при U num . = 10 В (5 В) |

2.90 (0.95) |

1.0 (0.8) |

2.90 (0.95) |

+ 25 ± 10; - 60 ± 3 ° С |

|

2.90 (0.95) |

1.0 (0.8) |

2.90 (0.95) |

+ 85 ± 3 ° С |

|

|

Минимальное выходное напряжение логической единицы, U 1 вых .min, В, не менее, при U num . = 10 В (5 В) |

7.2 (3.6) |

9.0 (4.2) |

7.2 (3.6) |

+ 25 ± 10; - 60 ± 3 ° С |

|

7.2 (3.6) |

9.0 (4.2) |

7.2 (3.6) |

+ 85 ± 3 ° С |

|

Таблица 3

Предельные и предельно-допустимые электрические режимы эксплуатации микросхем 765ЛН1-1, 765ИП2-1, 765ЛП2-1

|

Наименование параметра |

Вид микросхемы |

|||||

|

765ЛН1-1 |

765ИП2-1 |

765ЛП2-1 |

||||

|

ПДР |

ПР |

ПДР |

ПР |

ПДР |

ПР |

|

|

Напряжение питания, U сс , В |

4.2…13.5 4.2…15* |

–0.5…15 |

4.2…13.5 4.2…15* |

–0.5…15 |

4.2…13.5 4.2…15* |

–0.5…15 |

|

Напряжение на входе и выходе в состоянии «выключено», U x , U 0 , В |

–0.2…15 |

– |

–0.2…15 |

– |

–0.2…15 |

– |

|

Емкость нагрузки, С L , пФ |

Не более 50 3000** |

– |

Не более 50 1000** |

– |

Не более 50 3000** |

– |

ПДР – предельно-допустимый режим

ПР – предельный режим

* для аппаратуры, разработанной до 01.07.91 г., на рабочее напряжение 13.5 В

** для измерений режимов при особых условиях

В табл. 1 приведена информация о функциональном назначении микросхем 765ЛН1-1, 765ИП2-1, 765ЛП2-1.

В табл. 2 приведены значения электрических параметров микросхем 765ЛН1-1,

б )

Таблица истамости

|

Входя |

Выходя |

||||||||||||

|

1 |

3 |

4 |

6 |

10 |

12 |

13 |

15 |

2 |

5 |

7 |

9 |

11 |

и |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

f |

1 |

1 |

||

|

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

1 |

f |

1 |

f |

0 |

0 |

0 |

0 |

0 |

0 |

||

|

1 |

4 |

1 |

w |

м |

ачх |

rv |

cs> |

CSX |

|||||

* - произбо/ъное логическое значение

~ - логическое состояние определяется значением нгряхенип прилаженного к выходу мскрасхемы извне напртер б схеме 'монтажное И/И

в )

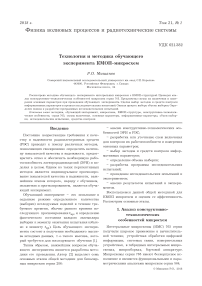

Рис. 1. Микросхема 765ЛН1-1: а ) функциональная электрическая схема; б ) изображение на электрических схемах; в ) таблица истинности

765ИП2-1, 765ЛП2-1 при напряжении питания и пит = 10 В, 5 В и температуре + 25 ± 10 ° С; - 60 ± 3 ° С; + 85 ± 3 ° С.

В табл. 3 приведены предельные и предельнодопустимые электрические режимы эксплуатации в диапазоне температуры среды.

В соответствии с техническими условиями (ТУ) минимальная наработка микросхем в составе гибридных интегральных микросхем (ГИМС) составляет 50 000 ч, а в облегченном режиме

а )

HetHi*

|

Входы |

Выходы |

||||||||||||

|

2 |

1 |

0 |

Е< |

Е= |

Е> |

< |

- |

> |

|||||

|

К1 |

К2 |

К1 |

К2 |

К1 |

К2 |

К1 |

К2 |

||||||

|

15 |

и |

2 |

1 |

7 |

9 |

ю |

11 |

5 |

6 |

4 |

12 |

3 |

13 |

|

1 0 |

1 |

0 |

0 |

1 |

|||||||||

|

К1=К2 |

1 0 |

1 |

0 |

0 |

1 |

||||||||

|

КЕК2 |

К1=К2 |

1 0 |

1 |

0 |

0 |

1 |

|||||||

|

КЖ2 |

К1=К2 |

К1=К2 |

1 0 |

1 |

0 |

0 |

1 |

||||||

|

К5К2 |

К1=К2 |

К1=К2 |

К1=К2 |

0 |

1 |

0 |

0 |

1 |

|||||

|

К1=К2 |

К1=К2 |

К1=К2 |

К1=К2 |

0 |

1 |

0 |

0 |

1 |

0 |

||||

|

К5К2 |

К1=К2 |

К1=К2 |

К1=К2 |

1 |

0 |

0 |

1 |

0 |

0 |

||||

|

К1=К2 |

К1=К2 |

К1=К2 |

0 1 |

1 |

0 |

0 |

|||||||

|

К1Ж2 |

К1=К2 |

0 1 |

1 |

0 |

|||||||||

|

К5К2 |

0 1 |

1 |

0 |

0 |

|||||||||

|

0 1 |

* |

• |

1 |

0 |

0 |

||||||||

* - произдольное логическое значение

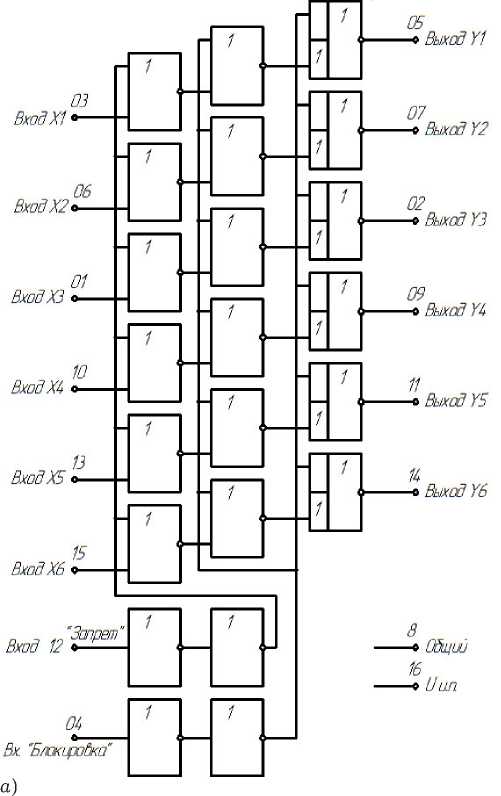

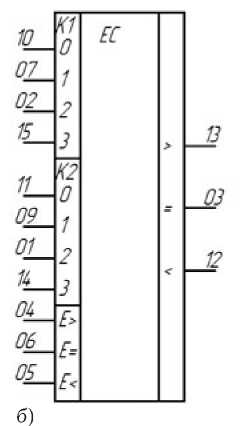

Рис. 2. Микросхема 765ИП2-1: а ) функциональная электрическая схема; б ) изображение на электрических схемах; в ) таблица истинности

(при напряжении питания Ucc = 5 В ± 10 % и температуре (25 ± 10) ° С — 75 000 ч.

Функциональная электрическая схема, изображение на схемах и таблица истинности микросхемы 765ЛН1-1 представлены на рис. 1.

Функциональная электрическая схема, изображение на схемах и таблица истинности микросхемы 765ИП2-1 представлены на рис. 2.

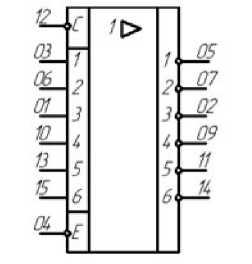

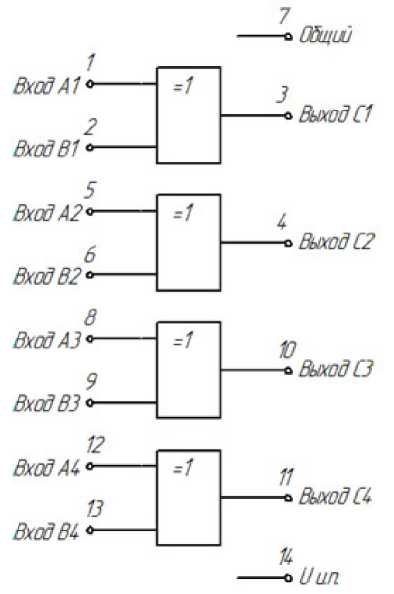

Функциональная электрическая схема, изображение на схемах и таблица истинности микросхемы 765ЛП2-1 представлены на рис. 3.

-

2. Разработка и уточнение схем включения

в )

Уточнение схем включения и измерения интересующих нас параметров имеет огромную важность для корректного проведения обучающего эксперимента. Для исследуемых микросхем измерению подвергаются следующие параметры:

– входной ток логического нуля Iв 0 х ;

– входной ток логической единицы Iв 1 х ;

а )

б )

Таблица истинности

|

Входы |

Выходы |

|

|

1 5 8 12 |

2 6 9 13 |

3 |4 10 |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

Рис. 3. Микросхема 765ЛП2-1: а ) функциональная электрическая схема; б ) таблица истинности

– ток потребления в статическом режиме Iпот ;

– выходное напряжение логического нуля 0

вых ;

– выходное напряжение логической единицы

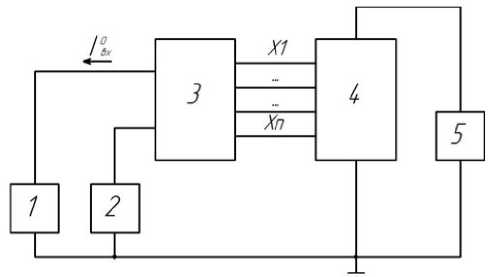

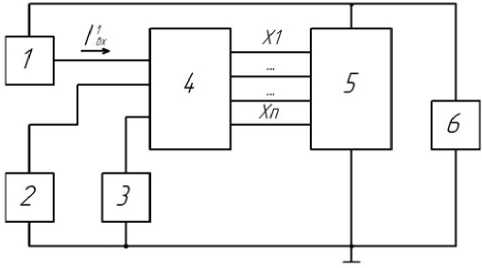

Рис. 4. Схема измерения входного тока логического нуля для микросхем765ЛН1-1 и 765ИП2-1

Рис. 5. Схема измерения входного тока логического нуля для микросхем 765ЛП2-1

Рис. 6. Схема измерения входного тока логической единицы для микросхем 765ЛН1-1, 765ИП2-1, 765ЛП2-1

подбирается в зависимости от исследуемой микросхемы; 4 – исследуемая микросхема; 5 – источник питающего напряжения; x 1 … xn – входы микросхемы.

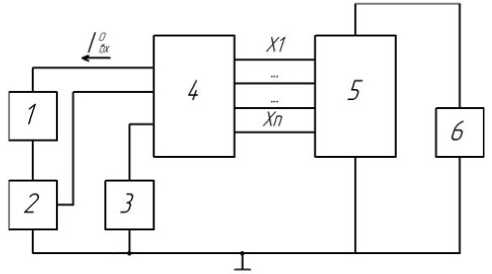

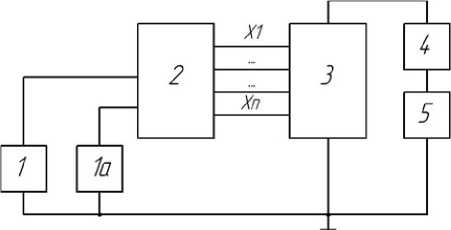

Схема измерения входного тока логического нуля для микросхемы 765ЛП2-1 представлена на рис. 5, где 1 – измеритель постоянного тока, с помощью которого измеряется Iв 0 х ; 2, 3 – источники постоянного напряжения; 4 – коммутатор входов; 5 – исследуемая микросхема; 6 – источник питающего напряжения; x 1 … xn – входы микросхемы.

Для исследуемых в работе микросхем применяется была рекомендована универсальная схема измерения входного тока логической единицы Iв 1 х , представленная на рис. 6, где 1 – изме-

Рис. 7. Схема измерения тока потребления в статическом режиме для микросхем 765ЛН1-1, 765ИП2-1, 765ЛП2-1

Рис. 8. Схема измерения выходного напряжения логического нуля для микросхем 765ЛН1-1 и 765ИП2-1

Рис. 9. Схема измерения выходного напряжения логического нуля для микросхемы 765ЛП2-1

Рис. 10. Схема измерения минимального выходного напряжения логической единицы для микросхемы 765ЛН1-1

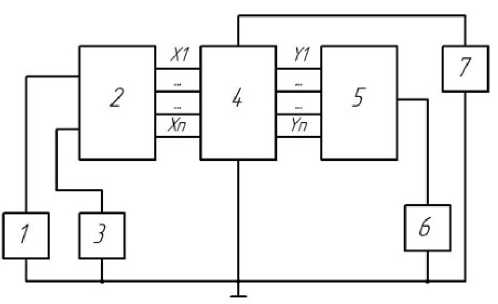

Измерение выходного напряжения логического нуля Uв 0 ых для микросхемы 765ЛП2-1 целесообразно проводить по схеме, представленной на рис. 9, где 1 – источник постоянного напряжения; 2 – исследуемая микросхема; 3 – коммутатор выходов; 4 – измеритель постоянного напряжения, с помощью которого измеряется Uв 0 ых ; 5 – источник питающего напряжения; x 1 … xn , y 1 … yn – входы и выходы микросхемы.

Для измерения выходного напряжения логической единицы Uв 1 ых микросхемы 765ЛН1-1 ложно использовать ту же схему (рис. 9).

Установлено, что схема измерения выходного напряжения логической единицы Uв 1 ых для микросхем 765ИП2-1, 765ЛП2-1 совпадает со схемой измерения выходного напряжения логического нуля Uв 0 ых для микросхемы 765 ЛН1-1 и 765ЛП2-1 (рис. 8).

Эту же схему можно использовать и для измерения максимального выходного напряжения логического нуля Uв 0 ых . max исследуемых микросхем. Также по этой схеме целесообразно измерять и минимальное выходное напряжение логической единицы Uв 1 ых . min для микросхемы 765ЛП2-1.

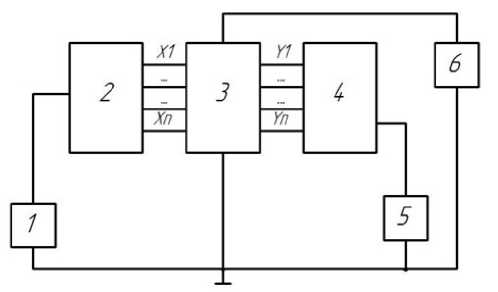

Схема измерения минимального выходного напряжения логической единицы Uв1ых. min для микросхемы 765ЛН1-1 представлена на рис. 10, где 1 – источник постоянного напряжения; 2, 4 – коммутаторы входов и выходов микросхемы; 3 – исследуемая микросхема; 5 – измеритель постоянного напряжения, с помощью которого измеряется Uв1ых. min; 6 – источник питающего напряжения; Xi ...xn, yi ... yn — входы и выходы микросхемы.

-

3. Выбор методов и средств контроля информативных параметров

Наиболее распространенными отказами в микросхемах являются:

-

– обрыв, пробой p-n переходов,

-

– изменение электрических параметров (параметрические отказы).

Практически всегда увеличение обратных токов предшествует отказу микросхемы.

Определение совокупности информативных параметров сопровождается выбором методов и средств контроля. При этом изучаются причины, механизмы отказа, а также проводится подробный анализ отказов конкретного вида микросхем, который также включает анализ статистических данных отказов.

В работе [4] приведена следующая информация по распределению отказов транзисторных сборок: обрыв в p-n переходах – 20 % случаев, параметрические отказы – 80 % случаев отказов. Для интегральных схем и полупроводниковых приборов приводится следующее распределение отказов: дефекты металлизации – 26 %, дефекты внутренних выводов – 23 %, дефекты в сборке корпуса – 17 %, изменение электрических характеристик – 12 %, поверхностные нарушения – 7 %, поверхностные несовмеще-ния – 7 %, дефекты окисла – 4 %, негерметичность – 4 % [4]. Таким образом, для повышения безотказности микросхем детального изучения требуют изменения электрических характеристик (параметрические отказы), несоответствие требованиям ТУ которых приводит к отнесению микросхем к классу негодных.

Для достоверного изучения отказов важнейшее значение имеет анализ причин отказов. Причиной обрывов в p-n переходах наиболее часто являются такие дефекты, как:

-

– пустоты в термокомпрессионных контактах;

-

– разрывы и отслоения выводов от металлизации;

-

– сужение вывода из-за повреждения при сварке;

-

– пустоты контактной площадки;

-

– утончения металлизации из-за нарушения технологии напыления;

-

– отслоения;

-

– прочие причины.

Пробой p-n перехода может быть вызван такими причинами, как:

-

– загрязнение кремния;

-

– усиление электрического поля вблизи примесей;

-

– возникновение микролокальных плазм при E > ЕПР ;

-

– лавинный пробой p-n перехода;

– образование шунтов в базе вследствие распада твердого раствора быстродиффундирую-щих примесей при высоких температурах.

Каждая серия микросхем имеет свои конструктивно-технологические особенности, для которых характерны «свои» дефекты. Так, ИМС серии 286 содержат большое количество элементарных ячеек с диффузионными резисторами. Данное обстоятельство вызывает разброс параметров таких резисторов, прежде всего их номинала. Кроме того, увеличение площади кристаллов для получения большой мощности приводит к росту вероятности активации дефектов (микротрещин, дислокаций, кластеров, нарушение профиля легирования, загрязнений поверхности). Указанные конструктивно-технологические особенности и дефекты могут приводить к неоднородности токораспределения и лавинного пробоя, снижению электрической прочности, локальным перегревам, росту токов утечки [3]. Указанные явления приводят к изменению формы вольт-амперной характеристики (ВАХ) при обратных смещениях p-n переходов.

Кроме того, при проектировании микросхем невозможно учесть возникающий разброс параметров однотипных элементов (в данном случае элементарных ячеек с диффузионными резисторами) из-за неточного воспроизведения технологических процессов при изготовлении ИМС и неидеальной чистоты исходных материалов. Такой разброс параметров однотипных элементов с течением времени и при воздействии дестабилизирующих факторов может привести к параметрическому и даже к функциональному отказу. Для повышения надежности работы аппаратуры автором [5] был предложен метод, основанный на проверке работы логики микросхемы при пониженном питающем напряжении. Чувствительность усилительных свойств транзисторов в микросхеме к токам утечки резко возрастает с понижением питающего напряжения. При этом транзисторы с высокими токами утечки будут неработоспособными, что можно легко определить, подав на входы микросхемы тестовую последовательность и считывая с выходов результат. При несовпадении результата, снятого с выхода микросхемы, и эталонной информации можно судить об отказе микросхемы, а значит и наличии больших токов утечки, рост которых при воздействии дестабилизирующих факторов в дальнейшем приведет к отказу микросхемы. В работе [6] приведена установка диагностического неразрушающего контроля (ДНК) для интегральных стабилизаторов, а также показано, что в качестве информативных параметров целесообразно выбирать ток потребления микросхемы Iпотр при заданном питающем напряжении.

Выбор средств контроля – достаточно сложная задача, возлагаемая на исследователя, т. к. выбранные средства должны удовлетворять следующим требованиям:

– измерение характеристик изделия должен быть простым и дешевым;

– обработка результатов должна быть также автоматизирована, т. к. данная операция не менее ответственная, чем измерение характеристик изделия;

– документирование результатов контроля должно быть также наглядным и удобным;

– принятие решения об уровне потенциально надежных ИМС также должно быть автоматизировано;

– совмещение операций диагностирования с контролем параметров по ТУ на одном рабочем месте с одной установкой микросхемы в адаптер (желательно).

-

4. Определение объема выборки

На данном этапе задачей является нахождение объема репрезентативной выборки, т. е. такой выборки, которая описывает характеристики генеральной совокупности (партии) с минимально допустимой ошибкой. Для нахождения предельной ошибки расхождения (или точности оценки) между характеристиками выборочной и генеральной совокупности б используют связь выборочной дисперсии ст 2, объема выборки n и t-статистику Стьюдента:

б = а

n

Формула (1) справедлива только для выборки с повторами, что для нас не представляет интерес. В случае бесповторной выборки формула усложняется:

б = а

где N – объем генеральной совокупности (партии). Так как изначально дисперсию определить невозможно вследствие того, что необходимо знать среднее значение характеристики x и от- клонения от этого значения, то переходят к использованию понятия доли признака в общей совокупности наблюдений, которую оценивают экспертным путем. Дисперсия доли равна:

^ q = q (i - q ),

где q – доля признака.

Таким образом, формула нахождения объема выборки равна:

n =

"Б2 Г- а^ + N

Данная формула справедлива для нахождения объема выборки, соизмеримого с объемом генеральной совокупности (партии). При использовании данной формулы необходимо использование t-статистики Стьюдента. Для определения а необходимо задать уровень доверительной вероятности и число степеней свободы. Уровень доверительной вероятности обычно задается равным 95 %. Число степеней свободы связано с объемом выборки, который мы определяем. В этом случае используют прогнозную величину объема выборки, после чего вычисляют точное значение, корректируют число степеней свободы и находят точное значение n.

На практике для упрощения вычислений ино- 22

гда принимают а ст q = 1, но такое допущение приводит к увеличению ошибки расчетов, выражающейся в значительном увеличении объема выборки.

При малых выборках их объем может быть определен из условия [7]:

4 t p 3 q (1 - q )

Yl.___■ = ---------------------- nmin 2

5 n

где tp3 – квантиль нормального распределения, соответствующий заданной доверительной вероятности P3; n^= = |Wn - q| — модуль отклонения частоты появления события Wn (числа элемен- тов с определенным видом дефекта) в выборке от вероятности q его появления в генеральной совокупности.

Для неблагоприятного случая ( q = 0.5) это соотношение приобретает вид:

2 tp 3

n min = 2 . (6)

О n

Однако, при определении объема выборки высоконадежных ЭРИ эта формула не дает желаемого результата.

В этом случае необходимо учитывать коэффициент качества k , который рекомендуют выбирать из диапазона 1…2 [8].

-

5. Разработка программы исследовательских испытаний

Исследовательские испытания – основной этап обучающего эксперимента, позволяющий:

-

– выявить процессы и схемы деградации ЭРИ;

-

– установить виды и механизмы отказов;

-

– установить типы дефектов;

– установить диапазоны нагрузок, ускоряющих отказы.

При этом становится возможным определить степень информативности признаков, критерии отбраковки (классификации) для каждого КТВ, выбрать наиболее информативные параметры, оптимизировать исследуемый КТВ, усовершенствовать методики проведения испытаний, обучающего эксперимента и отбраковки [1].

Обычно в программе испытаний выделяют шесть основных разделов:

-

– объект испытаний;

-

– цель испытаний;

-

– обоснование необходимости проведения испытаний;

-

– место проведения и обеспечение испытаний;

-

– объем и методика испытаний;

-

– оформление результатов испытаний.

Высокую сложность представляет разработка раздела «объем и методика испытаний», в котором необходимо указать:

-

– методы, условия испытаний, виды воздействий, их последовательность, уровень и время воздействий;

-

– контролируемые параметры;

-

– технические средства.

Эти вопросы выходят за рамки данной статьи.

Следует отметить, что максимальная эффективность испытания изделий достигается при минимальных погрешностях результатов.

Заключение

Описываемая в статье методика обучающего эксперимента для КМОП-микросхем показала высокую эффективность для получения необходимого набора исходных данных для проведения индивидуального прогнозирования (ИП). К достоинствам методики можно отнести:

-

– учет статистики отказов однотипных с исследуемыми элементами;

-

– контроль электрических параметров элементов с помощью схем, позволяющих осуществлять измерения с малыми погрешностями;

-

– определение статистически обоснованной величины объема исследуемой выборки.

Основным достоинством описываемой методики является получение малых погрешностей исходных данных, необходимых для проведения индивидуального прогнозирования, что увеличивает в дальнейшем точность прогноза.

Список литературы Технология и методика обучающего эксперимента КМОП-микросхем

- Пиганов М.Н. Индивидуальное прогнозирование показателей качества элементов и компонентов микросборок. М.: Новые технологии, 2002. 267 с.

- Тюлевин С.В., Пиганов М.Н. Методика обучающего эксперимента при индивидуальном прогнозировании показателей качества космических РЭС // Актуальные проблемы радиоэлектроники и телекоммуникаций: материалы всероссийской НТК 13-15 мая 2008 г. Самара: Издательство СГАУ, 2008. С. 239-253.

- Тюлевин С.В., Пиганов М.Н., Мишанов Р.О. Разработка методики диагностического неразрушающего контроля микросхем // Сборник научных трудов SWorld. 2014. Т. 5. № 4 (37). С. 66-73.

- Килибаева Ж.К. Анализ отказов и надежности полупроводниковых приборов и интегральных микросхем // Молодой ученый. 2014. № 8.1. С. 12-16.

- Повышение достоверности отбраковки БИС методом понижения питающего напряжения / А.И. Белоус [и др.] // Технология конструирования в электронной аппаратуре. 2001. № 4-5. С. 35-37.

- Mishanov R.O., Tyulevin S.V., Piganov M.N. Analysis of the unreliability reasons and the diagnostic non-destructive testing installation for the integrated stabilizers // SWorld Journal. 2015. J11510-032. P. 179-183.

- Глудкин О.П. Управление качеством электронных средств. М.: Высшая школа, 1994. 414 с.

- Карпов О.В. Определение объема выборки при индивидуальном прогнозировании различными методами // ХХIХ Гагаринские чтения: труды международной конференции. М.: МАТИ, 2004. С. 117-119.