Design of Low Power Sequential Circuit by using Adiabatic Techniques

Автор: Priyanka Ojha, Charu Rana

Журнал: International Journal of Intelligent Systems and Applications(IJISA) @ijisa

Статья в выпуске: 8 vol.7, 2015 года.

Бесплатный доступ

Various adiabatic logic circuits can be used for minimizing the power dissipation. To enhance the functionality and performance of circuit two adiabatic logic families PFAL and ECRL have been used and compared with CMOS logic circuit design. In this paper, A MASTER-SLAVE D flip-flop is proposed by the use of SPICE simulation on 90nm technology files. The simulation result shows that PFAL is a better energy saving techniques then ECRL logic circuit.

Adiabatic Switching, Energy Dissipation, AC Power Supply, Inverter, D Latch And D Flip-Flop

Короткий адрес: https://sciup.org/15010741

IDR: 15010741

Текст научной статьи Design of Low Power Sequential Circuit by using Adiabatic Techniques

Published Online July 2015 in MECS DOI: 10.5815/ijisa.2015.08.06

The expression ‘Adiabatic’ is taken from a Greek language which means no energy transfer with outer environment, this process is known as a thermodynamic. So the dissipated heat loss in adiabatic logic families is very less. But in CMOS logic design, charge flow in the circuit is studied and many methods can be used for minimizing power dissipation in basic CMOS design like: reducing the power supply and switching activities. A combination of above all is important in portable systems which have some common issues such as weight, size and life of battery [2, 4, 27].

In today’s modern era power dissipation is a primary concern in many application especially based on high performance battery operated and portable systems. By reducing the heat dissipation many digital signalprocessing system can improve in performance of the systems.

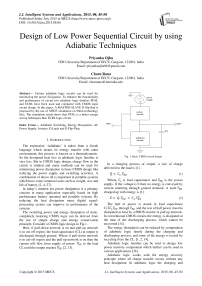

The switching power and energy dissipation of static, completely restoring CMOS logic can be derived from the use of simple charge and energy conservation principle. Consider a CMOS logic design in Fig.1.

Here, if pull-down network is on and pull-up network is in cut-off region, the load capacitance (CL) at output is discharged through ground. Where if pull-down network is in cut-off region and the pull-up network is on then the current will flow from supply of power DD to the load CL until the output reaches ^ DD [2, 13].

Fig. 1. Basic CMOS circuit design

In a charging process of output, a size of charge delivered to the load is [1].

Where, С is load capacitance and 1^щ is the power supply. If the voltage is 0 then no energy is conveyed by current returning through ground terminal. A node ^дд charged up with energy is [1].

E = Q.Vdd = CL.V^D (2)

The half of power is stored in load capacitance Ч^Д» through DD and the rest of half power must be dissipated as heat by a PMOS resistor in pull up network. In conventional CMOS circuits the energy is dissipated at the time of the discharging process, which cannot be recovered [14].

The energy dissipation can be reduced by computation of adiabatic logic family during the charging and discharging process, and some of the energy is reused by recycling from the CL. [1, 2, 14].

Adiabatic logic families can be used to design low power memory components which further can be used in various applications [28].

R

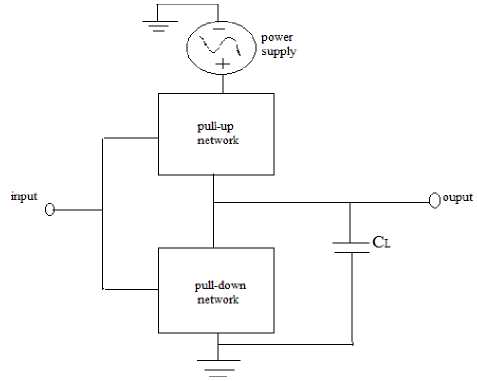

Fig. 2. Adiabatic logic design

In above circuit, the charge transferred is Q = cLvDD and the average current will be Q = ClVdd/2 (Q is transferred charge to the load) so, the computed dissipated energy is [20].

E«ss = P.R.T^ (ct .^У RT = ^R.CfTyWlC^ (3)

Here, EDISS = dissipated energy due to the charging time,

^L = load capacitance,

1^щ = power supply,

T = time of charging,

^ox = ON resistance value of the PMOS,

The energy dissipation (EDISS) is highly depended upon ^D?T , so the energy dissipation can be reduced by minimizing the ^ОУ of PMOS network. The first order approximation of ^G?T is given as: [13, 20, 24].

Ron = kQ/№s " ^r»)) (4)

к — цСм ^

Where, U= mobility,

^ox = oxide capacitance,

W= width,

L= length,

^5 = gate to source voltage,

ТЯ" = threshold voltage,

The result due to the “adiabatic principle” is a very slow change in systems which dissipate less energy than the fast ones; due to dissipation rates are proportional to the rate of change [20]. The equation (3) shows that it is also possible to minimize the energy dissipation by increasing the switching time values.

This is known as the adiabatic charging principle and the “adiabatic” term we are using here to indicate that all transferred charge is occurring without generating the heat [2]. The partially/quasi adiabatic ECRL and PFAL techniques have been implemented and discussed in this paper.

In this paper: In Section II, operation and basic concept of ECRL and PFAL Adiabatic Logic are discussed. In Section III, a D flip- flop is described by using D-LATCH. Simulation results of inverter and D flip-flop are shown in Section IV and Section V shows conclusion.

-

II. Operation of Ecrl and Pfal Adiabatic Logic

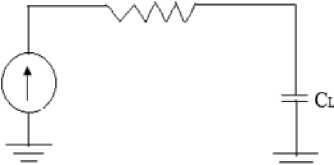

Adiabatic logic circuits manifest their efficiency in real applications. In adiabatic logic there are four phases, evaluate/pre-charge, hold, recovery and wait. Adiabatic circuits deliver energy in pre-charge phase and then recover it in the evaluation phase [1-4]. In Fig.3 According to new method, the load capacitance gets charged (in evaluation phase) and discharged (in recovery phase) through a clock power by CMOS transmission gate, and controlled by inputs. ECRL works on both (precharge and evaluation) phase simultaneously. Hold phase maintains the values (low and high) and then use these values as input for evaluation to next stage [4].

Fig. 3. Diagram of four phase logic for ECRL and PFAL

-

1. Pre-charge phase/evaluate phase

-

2. Hold phase

-

3. Recovery phase

-

4. Wait phase

-

A. Efficient Charge Adiabatic Logic

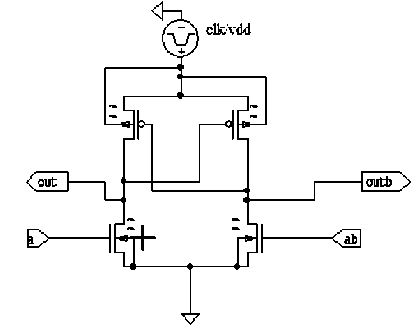

The proposed circuit of ECRL inverter gate uses the four phase clocking rule, the schematic and simulated waveform is shown in Fig.4 and Fig.5 simultaneously.

The ‘evaluation/precharge phase’ when input “a” is 1 and inverterd input “ab” is 0, the clk varies from 0 to vdd then the output “out” will be at ground level and “outb” will follow the pck (power clock).

As clk signal reaches to vdd, out and outb will enter into ‘hold phase’ (hold the logic value 0 and vdd respectively). Now after the hold phase clk signal goes from vdd to 0, the delivered value will recover and outb returns its energy to clk in ‘recover phase’.

ECRL uses 4-phase clock rule to recover all charges delivered through the clk signal, the next stage should be in the evaluation phase, if previous stage is holding the valid phase [4, 14].

Fig. 4. ECRL logic inverter

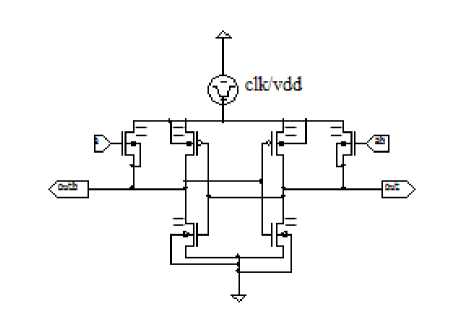

Fig. 6. PFAL logic inverter

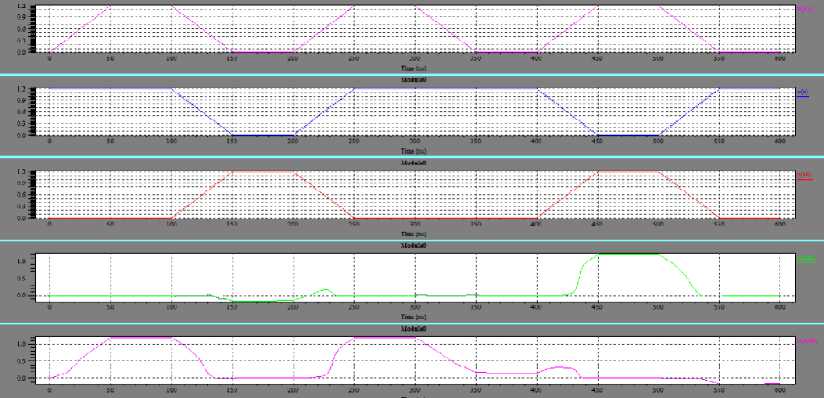

Fig. 5. ECRL and PFAL inverter waveform

-

B. Positive Feedback Adiabatic Logic

The proposed circuit of PFAL inverter gate is also utilizes the 4-phase clock rule, the schematic and simulated waveforms are shown in Fig.6 and Fig.5 simultaneously.

During ‘evaluation phase’ when input “a” is 1 and input bar “ab” is 0, the power clock “clk” goes from 0 to vdd then out will be at ground level and outb will follow the clk signal. As clk (Power Clock signal) reaches to vdd, out and outb will enter in ‘hold phase’ (hold the logic value 0 and vdd respectively).

Now after the hold phase clk signal goes from vdd to 0, the delivered will recover and outb returns its energy to clk ‘recover phase’.

Then ‘idle phase’ will be inserted to manage the symmetry of clock, the authentic inputs are being produced in the wait stage. In wait phase, right inputs arebeing prepared in last stage [5, 14].

-

III. D Flip-Flop Using D-Latch

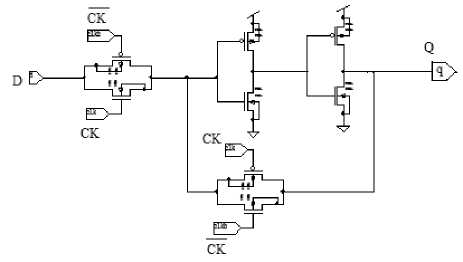

In digital circuit design there are various applications made by D-LATCH for temporary storage of data or as a delay element. Consider a conventional CMOS D-LATCH in Fig.7 which shows a basic two-inverter loop and two CMOS transmission gate switches. Here, D is a single input. If ck is high then Q (output) will follow value of the input D and when ck goes to zero, the Q or the information will preserve its state as the inverter loop. Hence, the ck input acts as a signal which allows data to be latched into the circuit when ck=1.

Fig. 7. CMOS D-LATCH

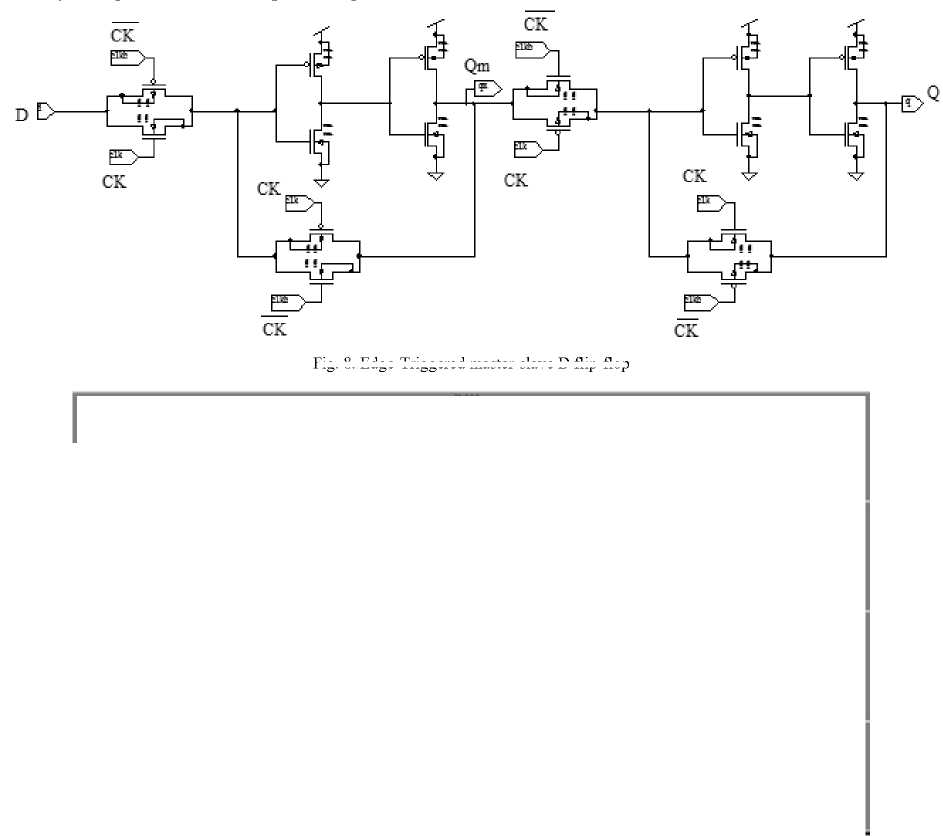

In Fig.7 this circuit is not an edge-triggered storage circuit because the final outcome depends on the input hence; the latch is transparent when ck is high. So this drawback makes it unsuitable for some applications like counters. For removing this drawback considers a two stage MASTER-SLAVE flip-flop circuit in Fig.8 which is designed by cascading two D-LATCH circuits.

sensitive, while master part is positive level-sensitive.

The master stage is d riven by ck signal and slave stage is driven by ck signal. So, the slave part is negative level-

Fig. 8. Edge-Triggered master-slave D flip-flop

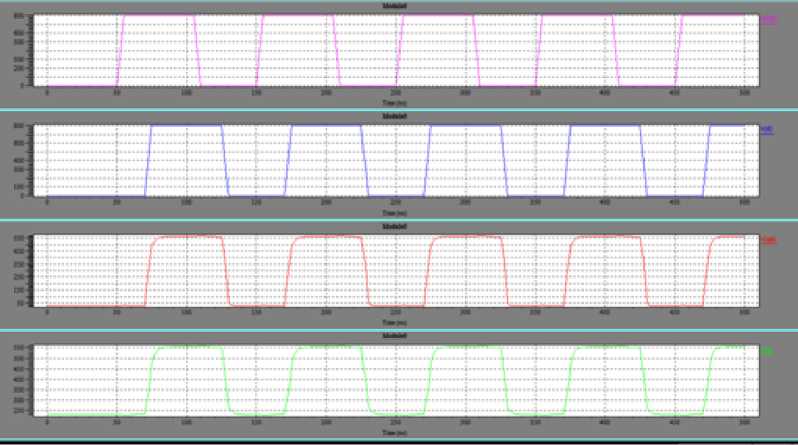

Fig. 9. simulated waveform of CMOS d flip-flop, ECRL and PFAL D flip-flop

-

IV. Simulation Results

The proposed sequential circuit D flip-flop is simulated by the use of SPICE tool based on 90nm technology. For this simulation we have used W/L ratio for NMOS transistors is 135nm/90nm and for PMOS transistors it is 405nm/90nm.

Fig. 10. supply voltage vs power dissipation for an inverter at frequency=10MHz on 90nm technology

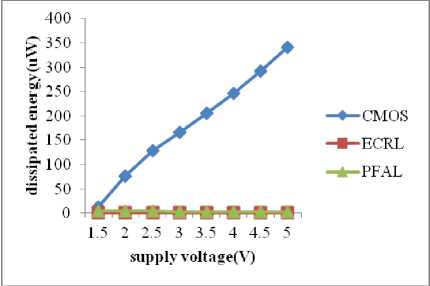

The power consumed by the ECRL inverter and PFAL inverter at various voltage power supplies ranging from 1.5V to 5V is plotted in Fig.10.

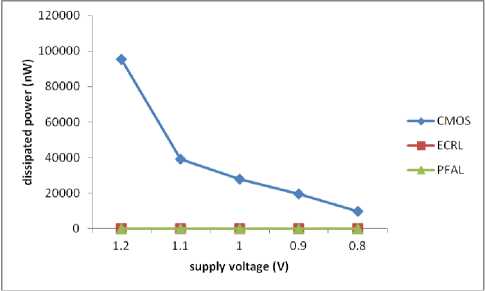

ECRL D flip-flop and PFAL D flip-flop at various power supply variations form 0.9V to 1.2V is plotted in Fig.11. The result has been compared with conventional CMOS circuit design.

Fig. 11. supply voltage vs power dissipation for a D FLIP-FLOP on 90nm technology

Here, it can be seen that in Fig.10 and Fig.11 the gap in between adiabatic logic families and CMOS logic is reducing as supply voltage minimized.

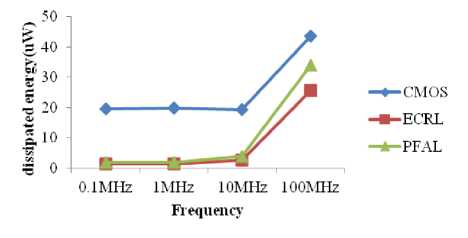

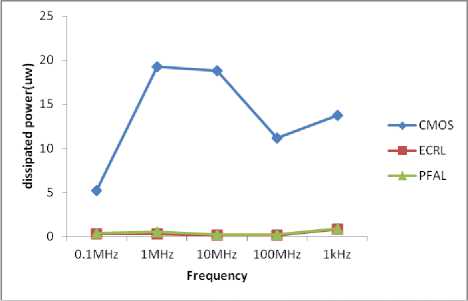

Adiabatic logic families are strongly dependent on parameters variation [17]. Fig.12 and Fig.13 shows graphical representation of frequency versus dissipated power in traditional CMOS logic inverter and a sequential circuit D flip-flop at 1.5V and 1V power supply simultaneously.

For the comparison purpose the ECRL logic and PFAL logic is compared by CMOS logic design at frequency ranging from 0.1MHz to 1 kHz.

Fig. 12. Frequency vs power dissipation for an inverter at VDD=1.5V on 90nm technology

Fig. 13. Frequency vs power dissipation for a D FLIP-FLOP at VDD=1V on 90nm technology

Table 1. Summary of the results for Fig.10 and Fig.11

|

D FLIP-FLOP |

|||

|

VDD (V) |

CMOS (u WATT) |

ECRL (u WATT) |

PFAL (u WATT) |

|

Frequency variation on Technology – 90nm at 1V |

|||

|

0.1MHz |

5.187044 |

0.31157 |

0.370773 |

|

1MHz |

19.23786 |

0.311697 |

0.487944 |

|

10MHz |

18.77796 |

0.157406 |

0.185722 |

|

100MHz |

11.19761 |

0.157006 |

0.166279 |

|

1kHz |

13.73116 |

0.79592 |

0.853199 |

|

Supply voltage variation on Technology – 90nm |

|||

|

1.2 |

95530.18 |

0.132983 |

0.108913 |

|

1.1 |

39136.1 |

0.11151 |

0.089708 |

|

1 |

27715.08 |

0.092326 |

0.0756 |

|

0.9 |

19592.88 |

0.07461 |

0.06117 |

|

0.8 |

9678.32 |

0.059086 |

0.048556 |

Here, we can see that as frequency is increasing power dissipation is reducing and at very high frequency again it starts increase in power dissipation. Hence, it is investigated that at high frequencies, the behavior is no more adiabatic [13, 17].

But still PFAL and ECRL logic families consumes less power dissipation in circuit design by varying the parameters in circuit.

Adiabatic logic families show a advancement w.r.t CMOS, because of a high number of transistors needed in adiabatic implementation comparatively by the traditional CMOS implementation.

-

V. Conclusion

A D flip-flop circuit is designed with the help of inverter by using two adiabatic techniques ECRL, PFAL and a traditional CMOS have been successfully implemented to study the power consumption of digital and sequential circuits. The four phase clocking rule is used for to recover the efficient energy. The result has been carried out by using TSPICE simulation on 90nm technology files. It is investigated that PFAL and ECRL logic are even a better energy saving techniques as traditional CMOS. It is found that at high frequency the behavior is no more adiabatic. In overall conclusion, adiabatic logic can be used for low power circuits in VLSI design which reduced the energy dissipation over traditional CMOS logic design circuits.

Acknowledgement

The authors wish to thank to the ITM University for providing the EDA tools.

Rferences

-

[1] J.S Denker, “A review of adiabatic computing,” in IEEE Symp. On Low Power Electronics, pp.94-97, 1994.

-

[2] William C. Athas, Lars “J.” Svensson, Member, IEEE, Jeffrey G. Koller, Nestoras Tzartzanis, and Eric Ying-Chin Chou, Student Member, IEEE, “Low power digital system based on adiabatic-switching principles,” IEEE Trans. VLSI Systems, vol.2, no.4, pp.398-407, Dec. 1994.

-

[3] A. Kramer, J. S. Denker, S. C. Avery, A. G. Dickinson, and T. R. Wik, “Adiabatic computing with the 2N-2N2D logic family,” in IEEE Symp. on VLSI Circuits Dig. of Tech. papers, pp. 25-26, Jun. 1994.

-

[4] Y-Moon and D. K. Jeong, “An efficient charge recovery logic circuits,” IEEE J. Solid-State Circuits, Vol.31, no.4, pp.514-522, Apr. 1996.

-

[5] A. Vetuli, S. Di Pascoli, and L. M. Reyneri, “Positive feedback adiabatic logic,” Electronic Letters, vol.32, pp. 1867-1869, Sept. 1996.

-

[6] Kramer, J. Denker, B. Flower and J. Moroney, “Second order adiabatic computation with 2N-2P and 2N-2N2P logic circuits,” Proceedings of international symposium on low power design, pp. 191-196, 1995.

-

[7] Blotti, S. D. Pascoli, R. Saletti, and D. S. Landsiedel, “Sample model for positive feedback adiabatic logic power

consumption estimation,” Electronics Letters, vol.36, no. 2, pp. 116-118, Jan. 2000.

-

[8] Blotti, S. D. Pascoli, R. Saletti, and D. S. Landsiedel, “Improving the positive feedback adiabatic logic family,” in Advances in Radio Science, pp. 221-225, 2004.

-

[9] K. Lo and P. C. H. Chan, “An adiabatic differential logic for low power digital systems,” IEEE Trans. Circuits Syst. II, vol. 46, pp. 1245-1250, Sept. 1999.

-

[10] V. G. Oklobdzija, D. Maksimovic, L. Fengcheng, “Passtransistor adiabatic logic using single power-clock supply,” IEEE Trans. Circ. Syst. II, vol. 44, pp. 842-846, Oct. 1997.

-

[11] W. C. Athas, J. G. Koller, and L. J. Svensson, “An energyefficient CMOS line driver using adiabatic switching,” Proceeding Fourth Great Lakes Symp. VLSI Design, pp. 196-199, Mar. 1994.

-

[12] T. Indermauer and M. Horowitz, “Evaluation of charge recovery circuits and adiabatic switching for low power design,” Technical Digest IEEE Sym. Low Power Electronics, San Diego, pp. 102-103, Oct. 2002.

-

[13] Shweta Chauhan, Deepesh Ranka, Kamlesh Yadav, Rakesh Kumar Yadav, Ashwani K. Rana, “Four phase clocking rule for energy efficient digital circuits- an adiabatic concept ,” International Conference on Computer and Communication Technology (ICCCT), pp. 209-214, IEEE, 2011.

-

[14] Rakesh Kumar Yadav, Ashwani K. Rana, Shweta Chauhan, “Adiabatic technique for energy efficient logic circuits design,” Procceding of ICETECT, pp. 776-780, IEEE, 2011.

-

[15] Ashmeet Kaur Bakshi, Manoj Sharma, “Design of basic gates using ECRL and PFAL,” International Conf. on Computer and Communication Technology (ICCCT), pp. 580-585, IEEE, 2013.

-

[16] Atul Kumar Maurya, Gagnesh Kumar, “Adiabatic logic: energy efficient technique for VLSI applications,” International Conf. on Computer and Communication Technology (ICCCT), pp. 234-238, IEEE, 2011.

-

[17] Ettore Amirante, Agnese Bargagli-Stffi, Jurgen Fischer, Giueppe Iannaccone, and Doris Schmitt Landsiedel, “Variations of the power dissipation in adiabatic logic gates,” in Proc. 11th Int. Workshop PATMOS, Yverdon-Les-Bains, Switzerland, pp. 9.1.1-10, Sept. 2001.

-

[18] M. Eisele, J. Berthold, D. S. Landsiedel, R. Mahnkopf, “The Impact of Intra-Die Device Parameter Variations on Path Delays and on the Design for Yield of Low Voltage Digital Circuits,” IEEE Transactions on VLSI Systems, Vol. 5, No. 4, pp. 360-368, Dec. 1997.

-

[19] R. T. Hinman and M. F. Schlecht, “Power dissipation measurements on recovered energy logic,” in IEEE Symp. VLSI Circuits Dig. Tech. Papers, pp. 19–20, June 1994.

-

[20] J. G Koller, W. C. Athas, “Adiabatic switching, low enrgy computing, and the physics of storing and erasing information,” in Physics and Computation, pp. 267-270, Oct. 1992.

-

[21] Reginald H. Vanlalchaka, Soumik Roy, “Power eifficient odd parity generator and checker,” in Emerging Trends and Applications in Computer Science, pp. 65-69, Sept. 2013.

-

[22] Dr. D. Somasundareswari, A. K. Kumar, Dr. D. Duraisamy, G. Sabarinathan, “Asynchronous design of energy efficient full adder,” in International Conference on Computer Communication and Informatics, pp. 1-6, Jan. 2013.

-

[23] V. S. Kanchana Bhaaskaran, “Asymmertical positive feedback adiabatic logic for low power and higher frequency,” in International Conference on Advances in Recent Technologies in Communication and Computing, pp. 5-9, Oct. 2010.

-

[24] A. P. Chandrakasan, S. Sheng, and R. W. Brodersen, “Low-power CMOS digital design,” in IEEE Journal Solid- State Circ., vol. 27, no. 4, pp. 473-484, April 1992.

-

[25] R. T. Hinman and M. F. Schlecht, “Power dissipation measurements on recovered energy logic,” in IEEE Symp. On VLSI Circuits Dig. Of tech. Papers, pp. 19-20, June 1994.

-

[26] L. G. Heller and W. R. Griffin, “Cascode voltage switch logic: A differential CMOS logic family,” in ISSCC Dig. Tech. Papers, pp. 16-17, 1984.

-

[27] Mohammad Gholami, Gholamreza Ardeshir, H. Miar-Naimi, “A noise and mismatches of delay cells and their effects on DLLs,” in IJISA, Vol. 6, No. 5, pp. 37-43, April 2014.

-

[28] Sanjay Singh, Ravi Saini, Anil K. Saini, AS Mandal, Chandra Shekhar, “Performance evaluation of different memory components for FPGA based embedded system design for video processing application,” in IJISA, Vol. 5, No. 12, Nov. 2013.

-

[29] Ch. Praveen Kumar, S. K. Tripathy, Rajeev Tripathi, “High Performance Sequential Circuits with Adiabatic Complementary Pass-Transistor Logic (ACPL) ,” in TENCON 2009, IEEE, pp. 1-4.

-

[30] Moshe Avital, Hadar dagan, Itamar Levi, Osnat Keren, and Alexander Fish, “DPA-Secured Quasi-Adiabatic Logic (SQAL) for Low-Pwer Passaive RFID Tags Emplying S-Boxes” in IEEE transaction on circuits and systems, Vol. 62, No.1, pp. 149-156,January 2015.

-

[31] Yango Wu, Weijiang Zhang, and Jianping Hu, “Adiabatic 4-2 Compressors for Low-Power Multiplier” in IEEE Circuits and Systems, Vol. 2, pp. 1473-1476.

-

[32] Abhishek Agal. Pardeep, Bal Krishan, “comparative analysis of various SRAM cells with low power, high read stability and low area” in IJEM, Vol. 4, No. 3, pp. 1-12, December 2014.

Authors’ Profiles

Charu rana was born in Itanagar, Arunachal Pradesh on 1984. She recieved her B.Tech degree in Electronics and Communication Engineering from Kurukshetra University in 2005 and M.Tech in VLSI Design from Mody Instiute of Technology and Science, Sikar in 2008. She is currently involved in Ph.D

work in Jamia Millia Islamia. Her area of research is Low

Priyanka Ojha was born in Hisar, Haryana, India on September 2, 1989. She received the B.Tech degree from Kurukshetra University in 2013. She is currently involved in M.Tech work in ITM University. Her area of research is Low Power Design Techniques.

Список литературы Design of Low Power Sequential Circuit by using Adiabatic Techniques

- J.S Denker, “A review of adiabatic computing,” in IEEE Symp. On Low Power Electronics, pp.94-97, 1994.

- William C. Athas, Lars “J.” Svensson, Member, IEEE, Jeffrey G. Koller, Nestoras Tzartzanis, and Eric Ying-Chin Chou, Student Member, IEEE, “Low power digital system based on adiabatic-switching principles,” IEEE Trans. VLSI Systems, vol.2, no.4, pp.398-407, Dec. 1994.

- A. Kramer, J. S. Denker, S. C. Avery, A. G. Dickinson, and T. R. Wik, “Adiabatic computing with the 2N-2N2D logic family,” in IEEE Symp. on VLSI Circuits Dig. of Tech. papers, pp. 25-26, Jun. 1994.

- Y-Moon and D. K. Jeong, “An efficient charge recovery logic circuits,” IEEE J. Solid-State Circuits, Vol.31, no.4, pp.514-522, Apr. 1996.

- A. Vetuli, S. Di Pascoli, and L. M. Reyneri, “Positive feedback adiabatic logic,” Electronic Letters, vol.32, pp. 1867-1869, Sept. 1996.

- Kramer, J. Denker, B. Flower and J. Moroney, “Second order adiabatic computation with 2N-2P and 2N-2N2P logic circuits,” Proceedings of international symposium on low power design, pp. 191-196, 1995.

- Blotti, S. D. Pascoli, R. Saletti, and D. S. Landsiedel, “Sample model for positive feedback adiabatic logic power consumption estimation,” Electronics Letters, vol.36, no. 2, pp. 116-118, Jan. 2000.

- Blotti, S. D. Pascoli, R. Saletti, and D. S. Landsiedel, “Improving the positive feedback adiabatic logic family,” in Advances in Radio Science, pp. 221-225, 2004.

- K. Lo and P. C. H. Chan, “An adiabatic differential logic for low power digital systems,” IEEE Trans. Circuits Syst. II, vol. 46, pp. 1245-1250, Sept. 1999.

- V. G. Oklobdzija, D. Maksimovic, L. Fengcheng, “Pass-transistor adiabatic logic using single power-clock supply,” IEEE Trans. Circ. Syst. II, vol. 44, pp. 842-846, Oct. 1997.

- W. C. Athas, J. G. Koller, and L. J. Svensson, “An energy-efficient CMOS line driver using adiabatic switching,” Proceeding Fourth Great Lakes Symp. VLSI Design, pp. 196-199, Mar. 1994.

- T. Indermauer and M. Horowitz, “Evaluation of charge recovery circuits and adiabatic switching for low power design,” Technical Digest IEEE Sym. Low Power Electronics, San Diego, pp. 102-103, Oct. 2002.

- Shweta Chauhan, Deepesh Ranka, Kamlesh Yadav, Rakesh Kumar Yadav, Ashwani K. Rana, “Four phase clocking rule for energy efficient digital circuits- an adiabatic concept ,” International Conference on Computer and Communication Technology (ICCCT), pp. 209-214, IEEE, 2011.

- Rakesh Kumar Yadav, Ashwani K. Rana, Shweta Chauhan, “Adiabatic technique for energy efficient logic circuits design,” Procceding of ICETECT, pp. 776-780, IEEE, 2011.

- Ashmeet Kaur Bakshi, Manoj Sharma, “Design of basic gates using ECRL and PFAL,” International Conf. on Computer and Communication Technology (ICCCT), pp. 580-585, IEEE, 2013.

- Atul Kumar Maurya, Gagnesh Kumar, “Adiabatic logic: energy efficient technique for VLSI applications,” International Conf. on Computer and Communication Technology (ICCCT), pp. 234-238, IEEE, 2011.

- Ettore Amirante, Agnese Bargagli-Stffi, Jurgen Fischer, Giueppe Iannaccone, and Doris Schmitt Landsiedel, “Variations of the power dissipation in adiabatic logic gates,” in Proc. 11th Int. Workshop PATMOS, Yverdon-Les-Bains, Switzerland, pp. 9.1.1-10, Sept. 2001.

- M. Eisele, J. Berthold, D. S. Landsiedel, R. Mahnkopf, “The Impact of Intra-Die Device Parameter Variations on Path Delays and on the Design for Yield of Low Voltage Digital Circuits,” IEEE Transactions on VLSI Systems, Vol. 5, No. 4, pp. 360-368, Dec. 1997.

- R. T. Hinman and M. F. Schlecht, “Power dissipation measurements on recovered energy logic,” in IEEE Symp. VLSI Circuits Dig. Tech. Papers, pp. 19–20, June 1994.

- J. G Koller, W. C. Athas, “Adiabatic switching, low enrgy computing, and the physics of storing and erasing information,” in Physics and Computation, pp. 267-270, Oct. 1992.

- Reginald H. Vanlalchaka, Soumik Roy, “Power eifficient odd parity generator and checker,” in Emerging Trends and Applications in Computer Science, pp. 65-69, Sept. 2013.

- Dr. D. Somasundareswari, A. K. Kumar, Dr. D. Duraisamy, G. Sabarinathan, “Asynchronous design of energy efficient full adder,” in International Conference on Computer Communication and Informatics, pp. 1-6, Jan. 2013.

- V. S. Kanchana Bhaaskaran, “Asymmertical positive feedback adiabatic logic for low power and higher frequency,” in International Conference on Advances in Recent Technologies in Communication and Computing, pp. 5-9, Oct. 2010.

- A. P. Chandrakasan, S. Sheng, and R. W. Brodersen, “Low-power CMOS digital design,” in IEEE Journal Solid- State Circ., vol. 27, no. 4, pp. 473-484, April 1992.

- R. T. Hinman and M. F. Schlecht, “Power dissipation measurements on recovered energy logic,” in IEEE Symp. On VLSI Circuits Dig. Of tech. Papers, pp. 19-20, June 1994.

- L. G. Heller and W. R. Griffin, “Cascode voltage switch logic: A differential CMOS logic family,” in ISSCC Dig. Tech. Papers, pp. 16-17, 1984.

- Mohammad Gholami, Gholamreza Ardeshir, H. Miar-Naimi, “A noise and mismatches of delay cells and their effects on DLLs,” in IJISA, Vol. 6, No. 5, pp. 37-43, April 2014.

- Sanjay Singh, Ravi Saini, Anil K. Saini, AS Mandal, Chandra Shekhar, “Performance evaluation of different memory components for FPGA based embedded system design for video processing application,” in IJISA, Vol. 5, No. 12, Nov. 2013.

- Ch. Praveen Kumar, S. K. Tripathy, Rajeev Tripathi, “High Performance Sequential Circuits with Adiabatic Complementary Pass-Transistor Logic (ACPL) ,” in TENCON 2009, IEEE, pp. 1-4.

- Moshe Avital, Hadar dagan, Itamar Levi, Osnat Keren, and Alexander Fish, “DPA-Secured Quasi-Adiabatic Logic (SQAL) for Low-Pwer Passaive RFID Tags Emplying S-Boxes” in IEEE transaction on circuits and systems, Vol. 62, No.1, pp. 149-156,January 2015.

- Yango Wu, Weijiang Zhang, and Jianping Hu, “Adiabatic 4-2 Compressors for Low-Power Multiplier” in IEEE Circuits and Systems, Vol. 2, pp. 1473-1476.

- Abhishek Agal. Pardeep, Bal Krishan, “comparative analysis of various SRAM cells with low power, high read stability and low area” in IJEM, Vol. 4, No. 3, pp. 1-12, December 2014.